VIVADO 工具与 Verilog 语言之与门IP核设计

与门IP核设计

实验目的

通过实验,让学生进一步熟悉 Vivado 的使用,学会可配置 IP 核的设计与封装方法,同 时也能对与门逻辑有更直观的认识。

实验内容

使用 Verilog HDL 语言的数据流描述方法设计一个数据宽度可在 1~32 之间变化,输入端口数可在 2~8 之间变化的与门 andgate,输入端 8 个,分别是 a,b,c,d,e,f,g,h,输出端为 q。 利用仿真来验证你的设计。并将该与门封装成可配置输入端口数和数据宽度的“与门”IP 核。

实验步骤

1. 创建并仿真andgate项目

- 按照上述步骤创建andgate项目,并创建andgate.v设计文件

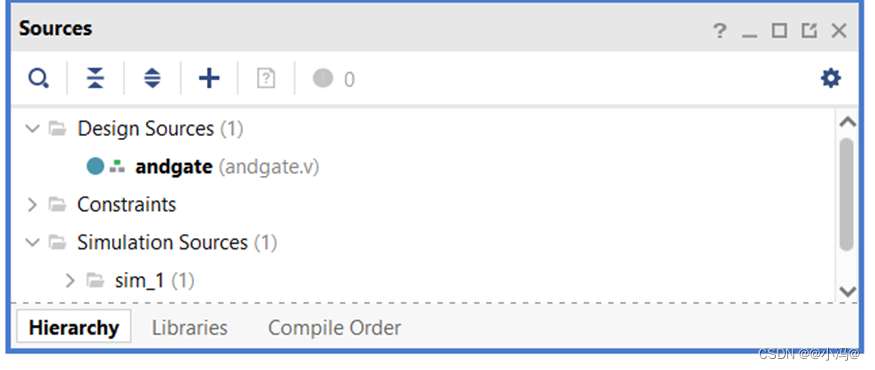

图 1-38 创建andgate项目

图 1-38 创建andgate项目 - 向andgate.v文件中写入如下内容

`timescale 1ns / 1ps

module andgate

#(parameter Port_Num = 2, // 指定缺省的输入是2个输入端口

parameter WIDTH = 8) // 指定数据宽度参数,缺省值是8

(

input [(WIDTH - 1) : 0] a,

input [(WIDTH - 1) : 0] b,

input [(WIDTH - 1) : 0] c,

input [(WIDTH - 1) : 0] d,

input [(WIDTH - 1) : 0] e,

input [(WIDTH - 1) : 0] f,

input [(WIDTH - 1) : 0] g,

input [(WIDTH - 1) : 0] h,

output [(WIDTH - 1) : 0] q

);

assign q = (a & b & c & d & e & f & g & h);

endmodule

- 建立andgate_sim.v仿真文件并写入如下内容

`timescale 1ns / 1ps

module andgate_sim();

// input

reg a = 0;

reg b = 0;

reg c = 1;

reg d = 1;

reg e = 1;

reg f = 1;

reg g = 1;

reg h = 1;

// output

wire q;

// 实例化与门的时候,设定宽度为1

andgate #(8, 1) u(

.a(a),

.b(b),

.c(c),

.d(d),

.e(e),

.f(f),

.g(g),

.h(g),

.q(q)

);

initial begin

#100 a = 1;

#100 begin a = 0; b = 1; end

#100 a = 1;

end

endmodule

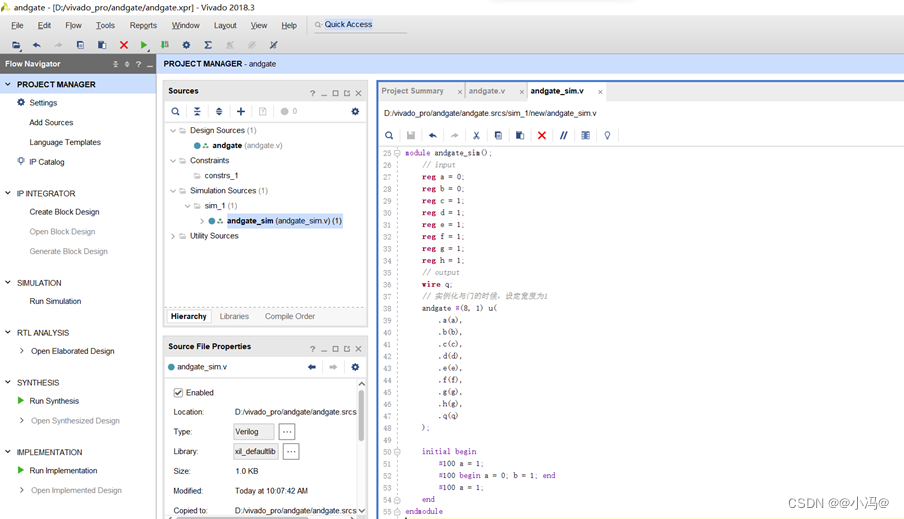

图 1-39 创建andgate_sim.v仿真文件

图 1-39 创建andgate_sim.v仿真文件

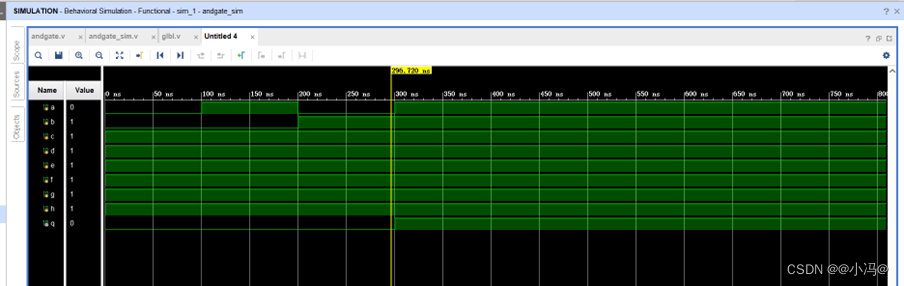

4. 仿真得到如下波形

图 1-40 1 位 8 输入与门的仿真波形

5. 建立andgate32_sim.v文件并写入如下内容

`timescale 1ns / 1ps

module andgate32_sim();

// input

reg [31:0] a = 32'h00000000;

reg [31:0] b = 32'h00000000;

reg [31:0] c = 32'hffffffff;

reg [31:0] d = 32'hffffffff;

reg [31:0] e = 32'hffffffff;

reg [31:0] f = 32'hffffffff;

reg [31:0] h = 32'hffffffff;

reg [31:0] g = 32'hffffffff;

// output

wire [31:0] q;

// 实例化与门的时候,设定宽度为32

andgate #(8, 32) u(

.a(a),

.b(b),

.c(c),

.d(d),

.e(e),

.f(f),

.g(g),

.h(h),

.q(q)

);

initial begin

#100 a = 32'hffffffff;

#100 begin

a = 32'h00000000;

b = 32'hffffffff;

end

#100 a = 32'h007fa509;

#100 a = 32'hffffffff;

end

endmodule

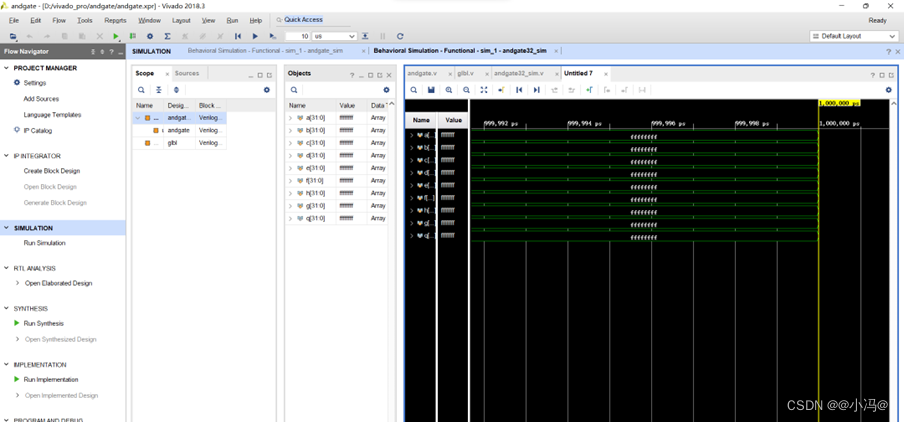

- 仿真后得到如下波形

图 1-41 32 位 8 输入与门的仿真波形

2. 综合并封装IP核

-

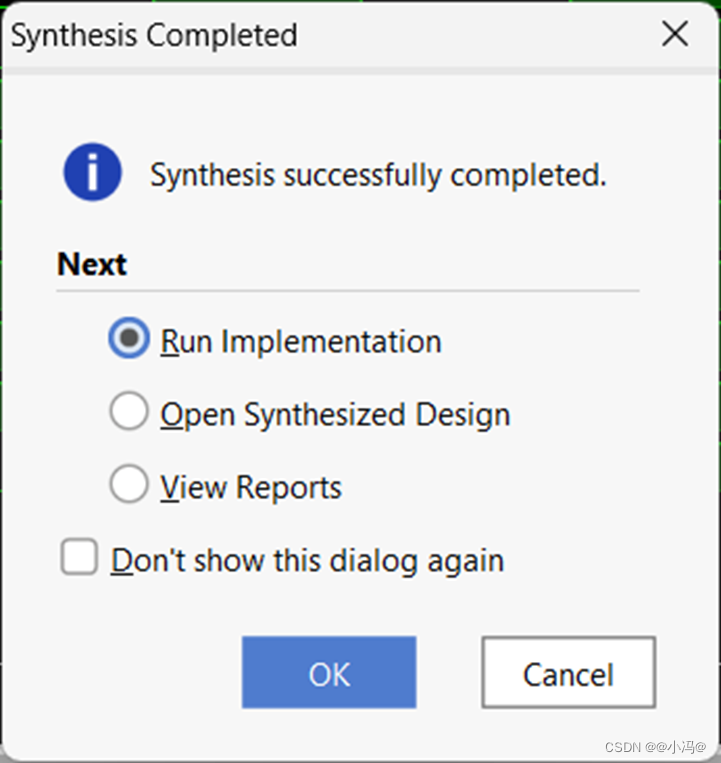

对仿真正确的IP核进行综合,得到如下结果

图 1-42 综合结束

图 1-42 综合结束 -

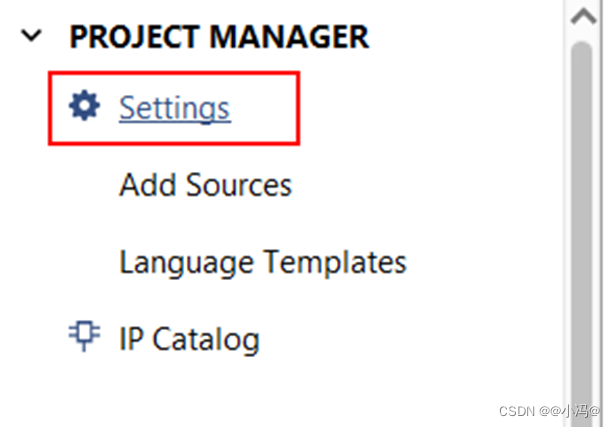

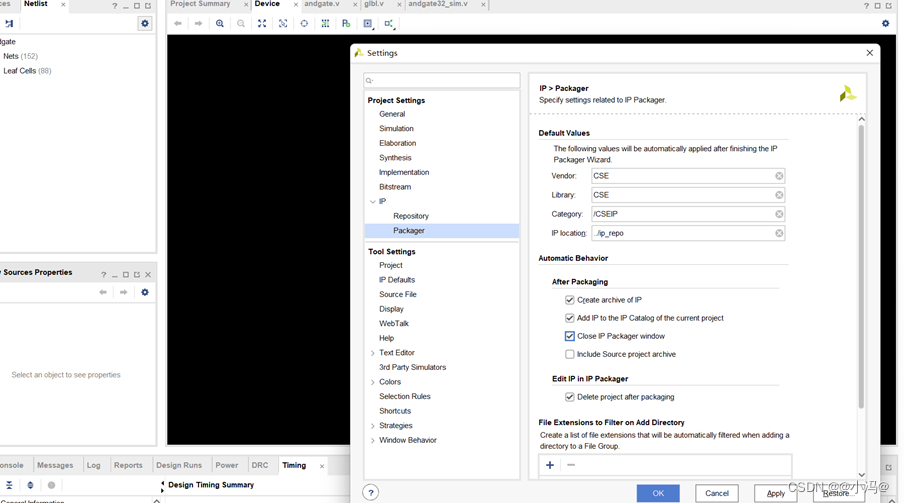

点击PROJECT MANAGER中的Settings,再点击IP、Packager,设置成如下内容,点击OK

图 1-43 Project Manager

图 1-43 Project Manager

图 1-44 项目设置中设置 IP 核封装属性

图 1-44 项目设置中设置 IP 核封装属性 -

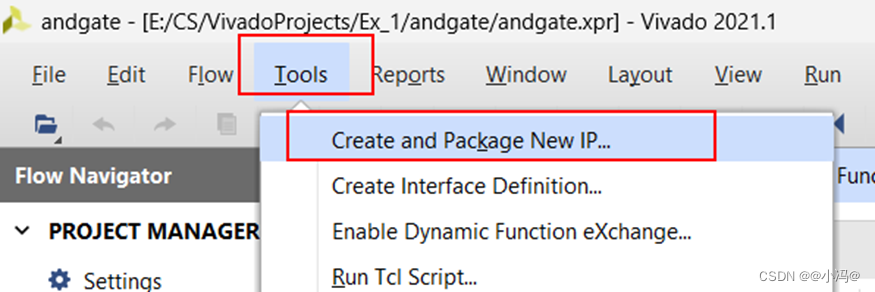

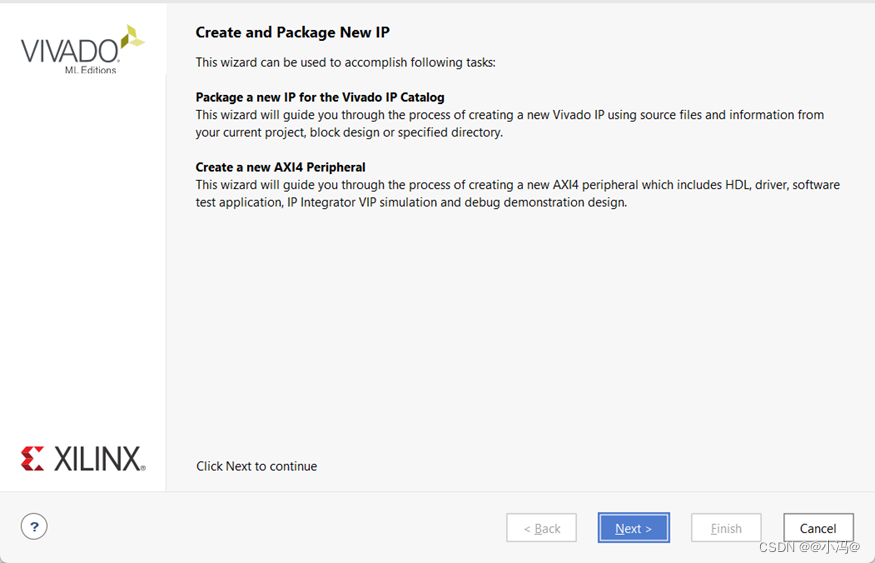

在Vivado的工具栏中选择Tools、Create and Package New Ip…

图 1-45 封装选项

图 1-45 封装选项 -

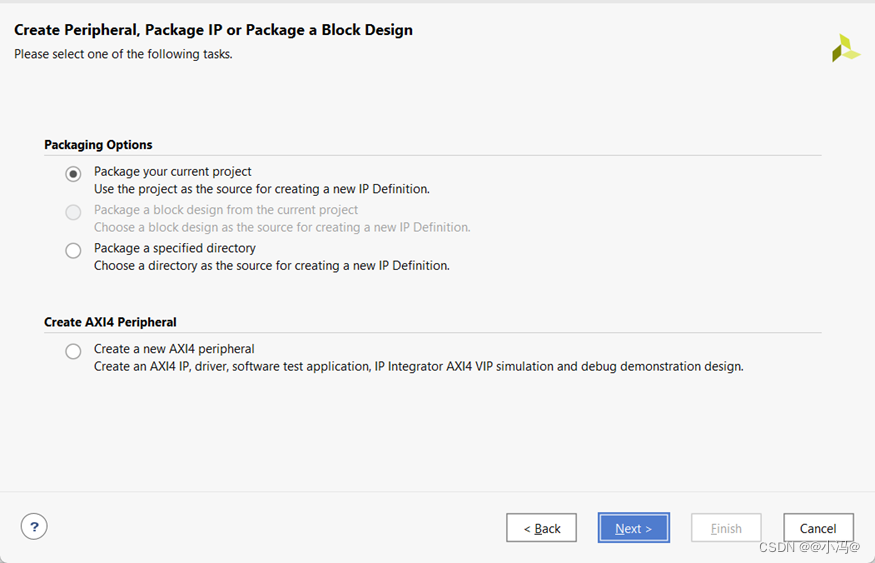

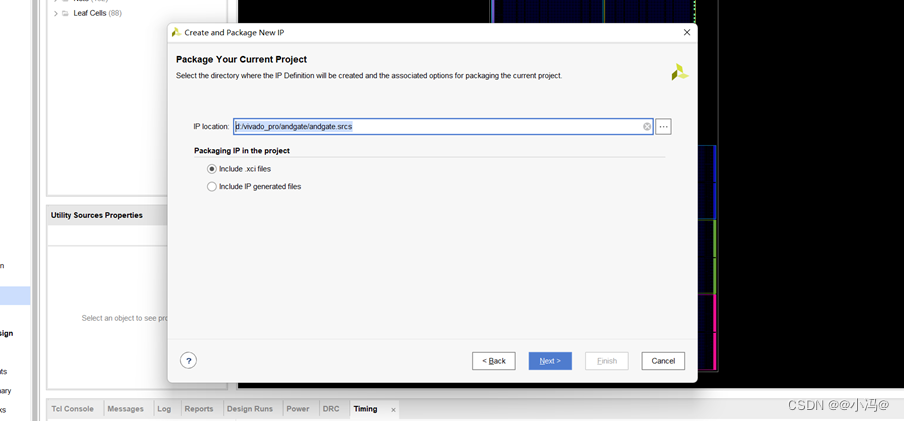

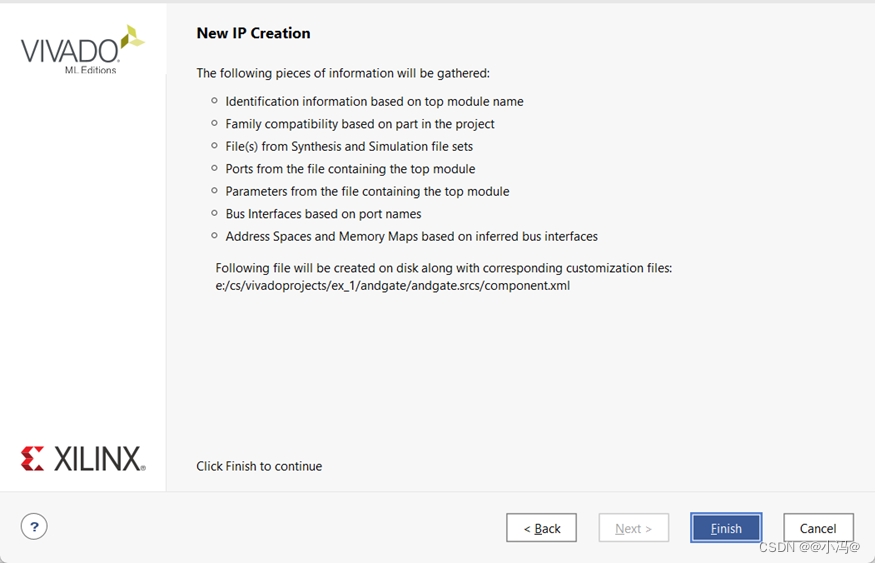

接下来出现的窗口中点击Next、Next、Next、Finish

图 1-46 Next

图 1-46 Next

图 1-47 Next

图 1-47 Next

图 1-48 IP Location

图 1-48 IP Location

图 1-49 创建 IP 核结束 -

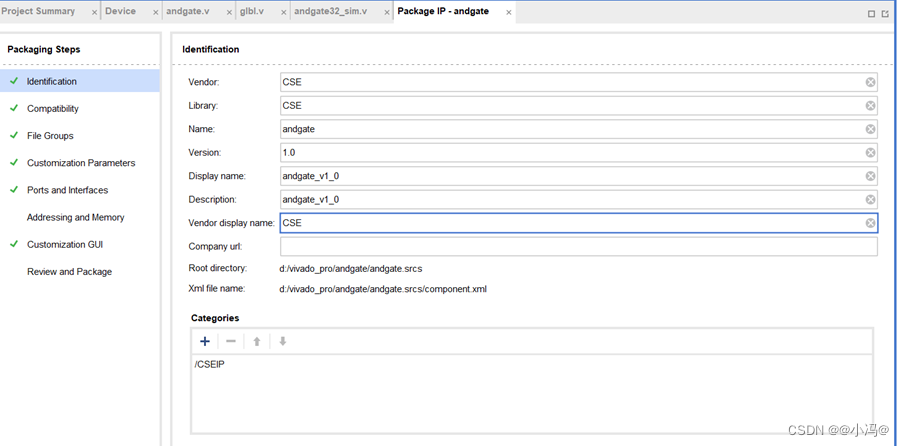

在新出现的窗口中,如图设置属性

图 1-50 设置 Identification

图 1-50 设置 Identification -

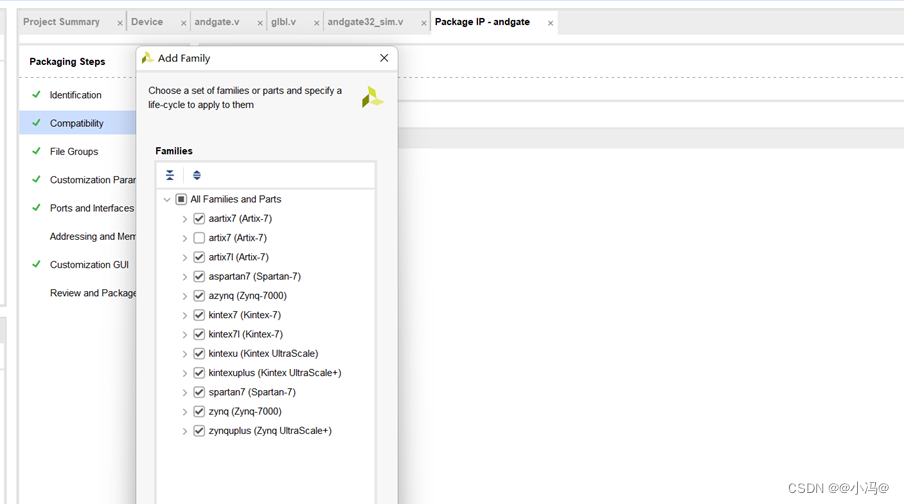

接下来点击Compatibility,在All Families and Parts选项中选中除artix7外的所有芯片家族(因为artix7系列已经有了),Life-cycle 选择 Production,然后点击 OK。这样就设置完了 compatibility。

图 1-51 Add Family 对话框

图 1-51 Add Family 对话框 -

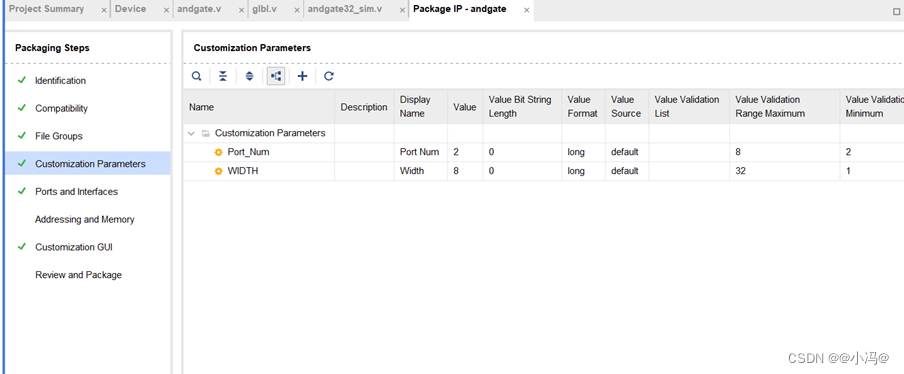

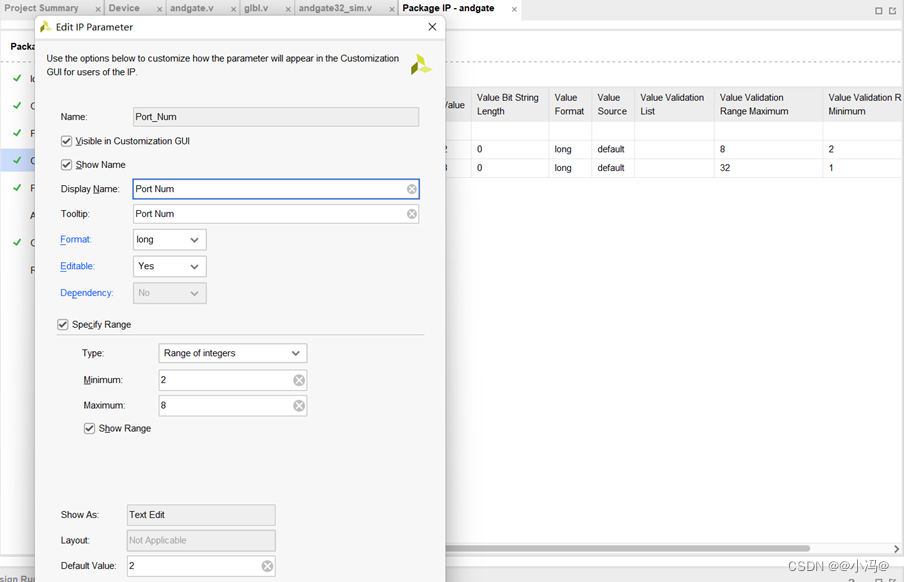

点击进入到Customization Parameters选项中,双击Port_Num得到如下图所示的IP 和参数的对话框,按照下图那样设置Port_Num 参数后点 OK。

图 1-52 Customization Parameters

图 1-52 Customization Parameters

图 1-53 编辑 IP 核的 Port_Num 参数

图 1-53 编辑 IP 核的 Port_Num 参数

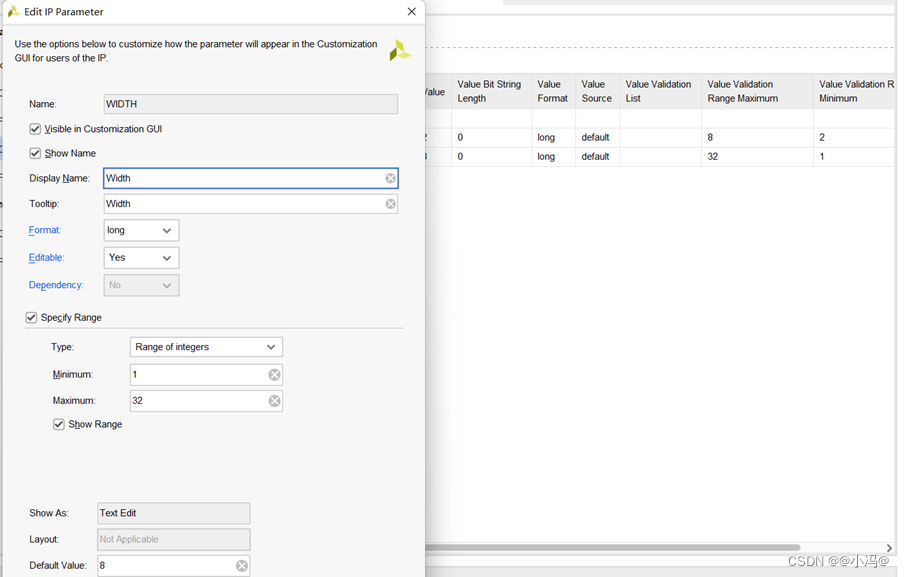

9. 按照相同的方法设置WIDTH选项 图 1-54 编辑 IP 核的 WIDTH 参数

图 1-54 编辑 IP 核的 WIDTH 参数

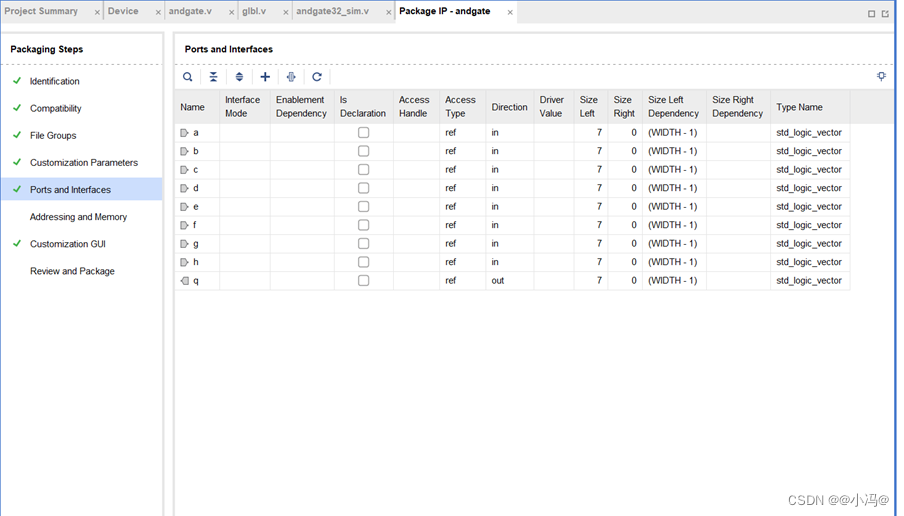

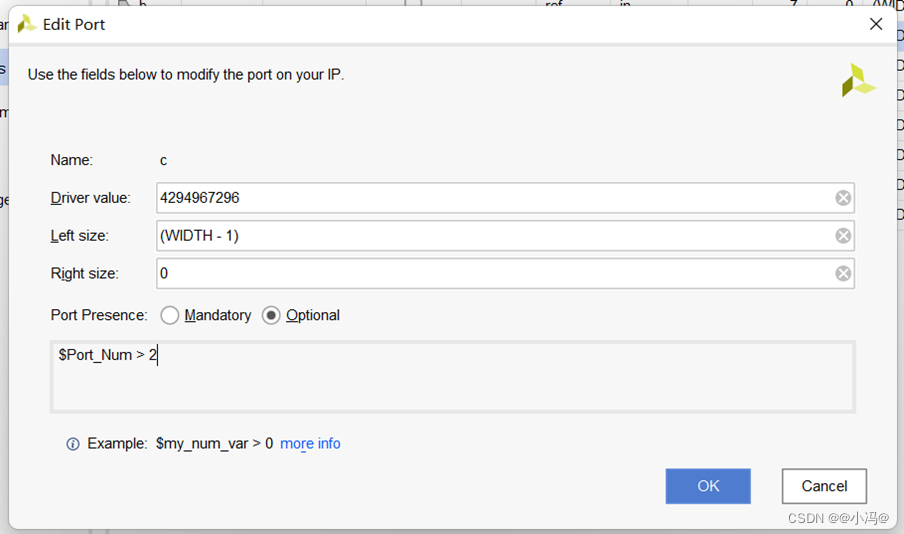

10. 接下来来到到 Ports and Interfaces界面。由于我们设计的数据输入端最小是 2 个,因此,a、b 两个输入端时钟都是 Enable 的。而 c~h 输入端则要根据 Port_Num 的值决定是否 Enable。双击端口 c,在打开的对话框中, 按照下图所示设置。 图 1-54 Ports and Interfaces 设置

图 1-54 Ports and Interfaces 设置 图 1-55 编辑端口 c 的参数

图 1-55 编辑端口 c 的参数

Driver value 是指端口 c 在 disable 时候的取值。在 andgate 模块中,共定义了 8 个输入端口,但实际应用中允许只用 2~8 个中的任意多个输入端口,不用的端口需要设置 成 disable 状态。在 IP 核中,所谓 disable 的端口实际上只是不提供给外部接口输入,但在 模块中该端口依然存在,所以如果必要,需要对它赋一个驱动值。由于制作的是“与门”, 因此所有不接外部接口的 disable 输入端应该赋值为全 1,也就是 16 进制的 FFFFFFFF,十进制的 4294967295,因此在这里给出的赋值是 4294967295。 再看图 1-49 中的 Port Presence(端口存在),选择的是 Optional 说明该端口的存在是有 条件的,在下面的启动表达式编辑框中,输入$Port_Num > 2,表明当输入端口大于 2 的时 候,c 端口被启用(Enable)。 设置好后点击 OK。

- 按照上述步骤设置好端口 d,e,f,g,h 的参数。 设置好以后的 Ports and Interfaces 如下图所示。

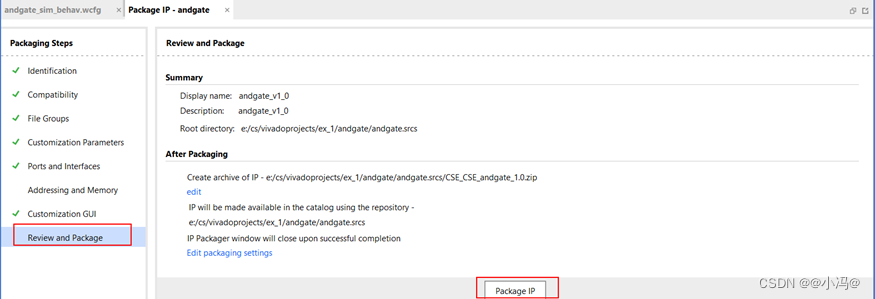

图 1-57 Review and Packaging 设置

图 1-57 Review and Packaging 设置 图 1-58 打包成功

图 1-58 打包成功

564

564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?