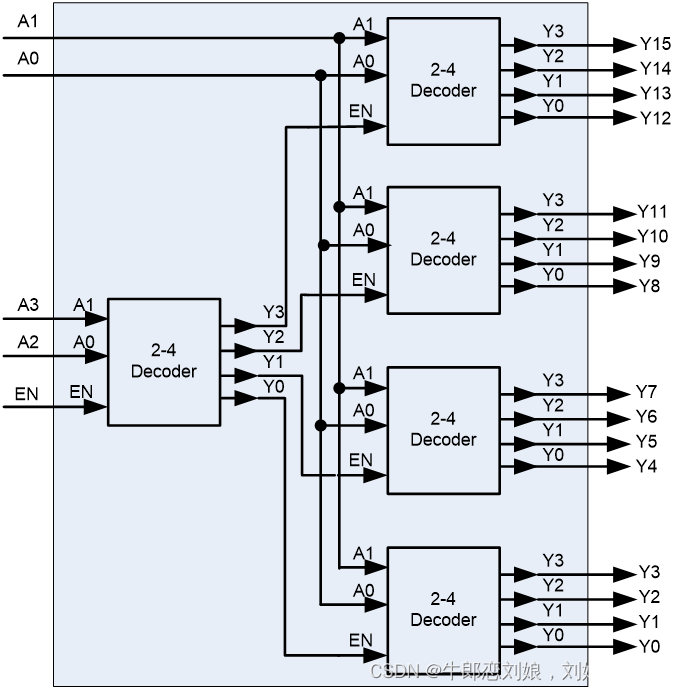

原理图如上

知道原理图 代码也就ok了

需要两个vhdl文件

一个是main文件 也就是主输入输出

另一个是 元件vhdl 实现部分输入输出 在这里指 2-4译码器

由于之前写的奇偶判别器 没有改实体名 这点可以忽略

主程序如下

entity jiou is

port(

signal x:in bit_vector(3 downto 0);

signal en:in bit;

signal z:out bit_vector(15 downto 0)

);

end entity;

architecture behave of jiou is

signal enchild:bit_vector(3 downto 0);

component jo21 is

port(

signal x:in bit_vector(1 downto 0 );

signal en:in bit;

signal y:out bit_vector(3 downto 0)

);

end component;

begin

u1:jo21 port map(x(3 downto 2),en,enchild(3 downto 0));

u2:jo21 port map(x(1 downto 0),enchild(3),z(15 downto 12));

u3:jo21 port map(x(1 downto 0),enchild(2),z(11 downto 8));

u4:jo21 port map(x(1 downto 0),enchild(1),z(7 downto 4));

u5:jo21 port map(x(1 downto 0),enchild(0),z(3 downto 0));

end architecture;

子程序如下

entity jo21 is

port(

signal x:in bit_vector(1 downto 0 );

signal en:in bit;

signal y:out bit_vector(3 downto 0)

);

end entity;

architecture behave of jo21 is

signal k:bit_vector(2 downto 0);

begin

k<=en&x;

with k select

y<="0001" when "100",

"0010" when "101",

"0100" when "110",

"1000" when "111",

"0000" when others;

end architecture;

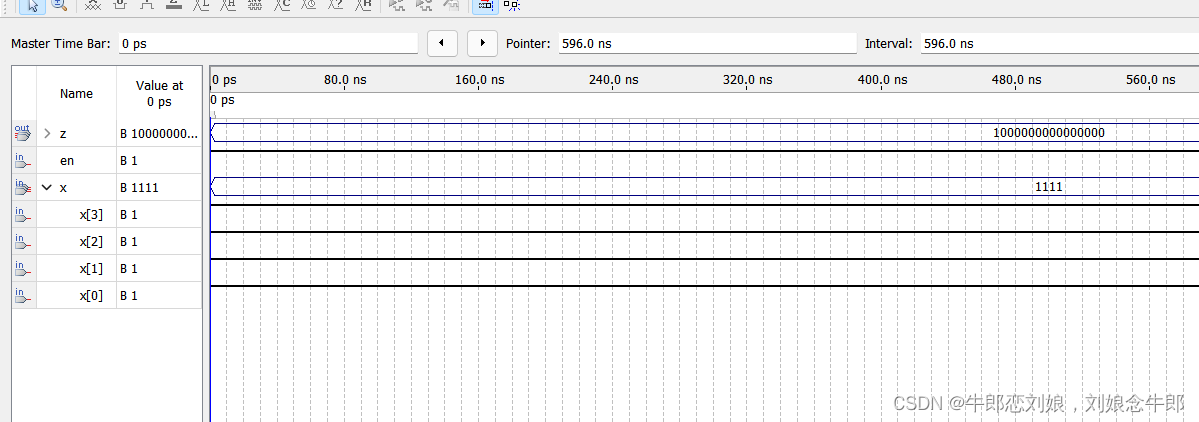

仿真波形图 部分如下

如此即可 。

如果本篇博客有用的话 请点个赞再走呗

该博客介绍了使用VHDL语言设计2-4译码器及其在主程序中的应用。主程序包括一个主输入输出模块和一个元件模块,元件模块实现了2-4译码功能。通过实例展示了如何将2-4译码器并联使用以得到更宽的输出。仿真波形验证了设计的正确性。

该博客介绍了使用VHDL语言设计2-4译码器及其在主程序中的应用。主程序包括一个主输入输出模块和一个元件模块,元件模块实现了2-4译码功能。通过实例展示了如何将2-4译码器并联使用以得到更宽的输出。仿真波形验证了设计的正确性。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?