1、实验内容

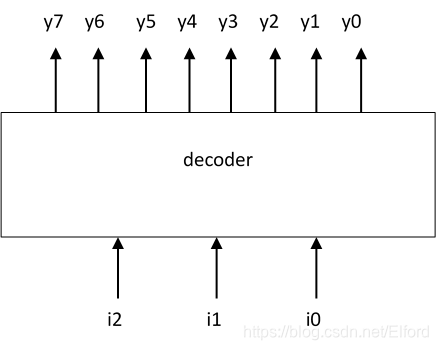

本实验要求完成一个3线-8线译码器的设计。其中i2-i0为译码器输入端,y7-y0为译码器输出端。图3.7为三线―八线译码器的框图,图8给出了三线―八线译码器的原理图。

图3.7 3线―8线译码器框图:

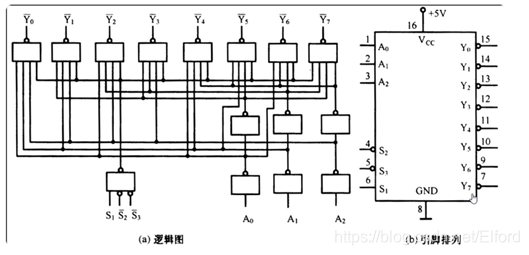

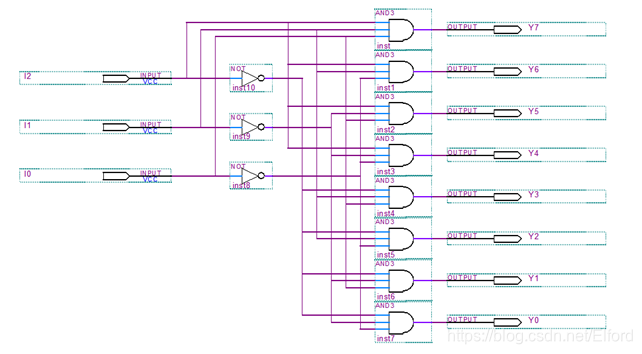

2、实验原理图

①3-8译码器:

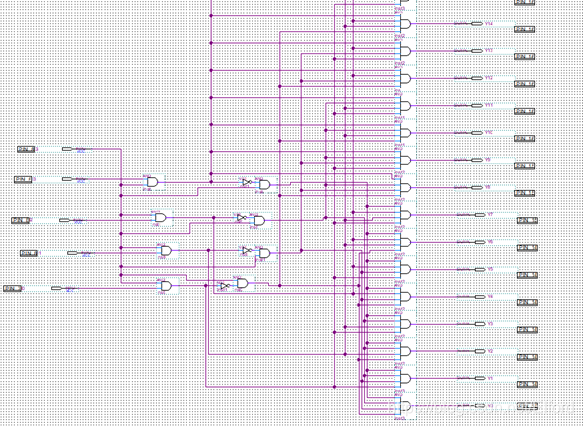

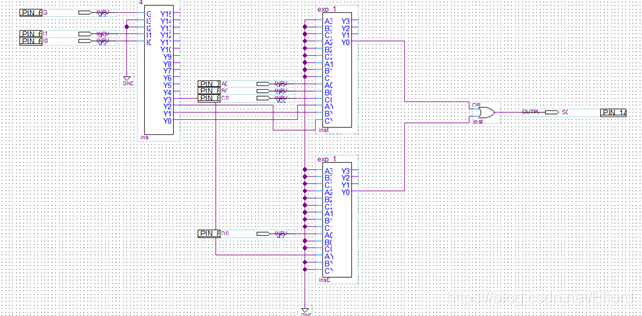

②4-16译码器:

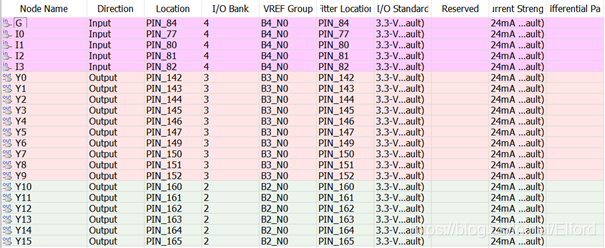

引脚分配图:

键K4是使能端,键K3~ K0控制4位二进制数的读入,小灯LR15~LR0控制译码结果的显示。如果要使用3-8译码器,则只需使用键K1和K0即可。

该译码器为4-16译码器,设计思路是根据输入输出的真值表来连线,逻辑比较简单。

③4选1数据选择器:

其中用到了译码器是实验1画的数据选择器,最终只会显示1个结果。

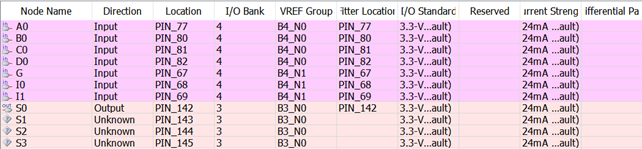

引脚分配图:

其中,键K8为使能端,键K9、K10为要选择的数据,用二进制数表示,键K3~K0表示输入数据。

数字逻辑设计:3-8线译码器与4-16译码器实现

数字逻辑设计:3-8线译码器与4-16译码器实现

实验内容包括设计并理解3线-8线及4线-16线译码器的工作原理。3线-8线译码器采用3个输入,输出8个信号;4线-16线译码器则通过4位二进制数读入,控制16个输出。实验中,4-16译码器的使能端、输入控制和显示部分被详细说明,并指出其设计思路依赖于输入输出的真值表。此外,还涉及了4选1数据选择器的使用,该选择器利用译码器仅显示一个选定的结果。

实验内容包括设计并理解3线-8线及4线-16线译码器的工作原理。3线-8线译码器采用3个输入,输出8个信号;4线-16线译码器则通过4位二进制数读入,控制16个输出。实验中,4-16译码器的使能端、输入控制和显示部分被详细说明,并指出其设计思路依赖于输入输出的真值表。此外,还涉及了4选1数据选择器的使用,该选择器利用译码器仅显示一个选定的结果。

3491

3491

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?