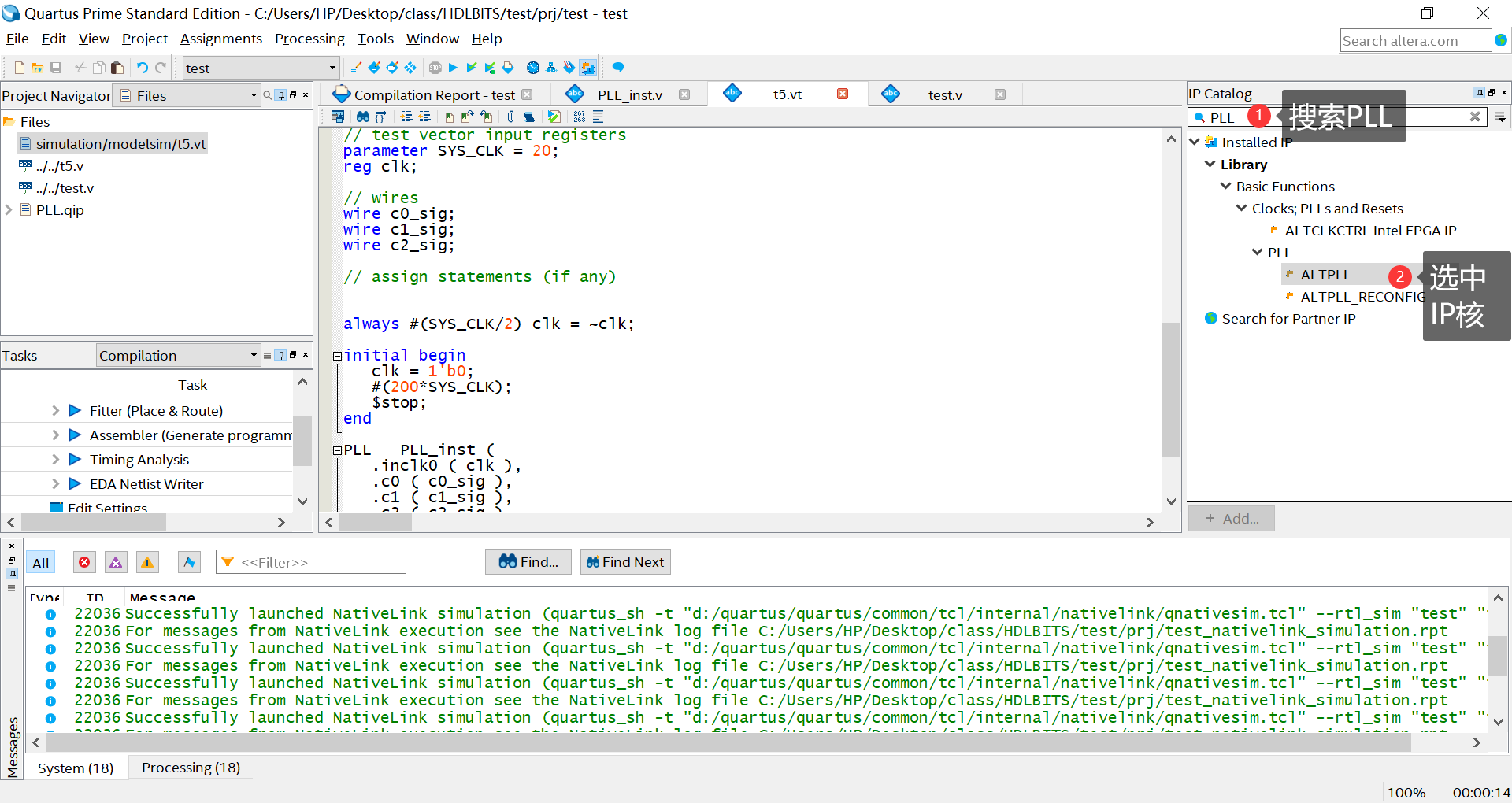

quartus工具篇——PLL IP核的使用

1、PLL简介

PLL(Phase-Locked Loop,相位锁环)是FPGA中非常重要的时钟管理单元,其主要功能包括:

- 频率合成 - PLL可以生成比输入时钟频率高的时钟信号。

- 频率分频 - PLL也可以输出分频后的较低频率时钟。

- 减小时钟抖动 - PLL可以过滤输入时钟中的噪声和抖动。

- 锁相输出 - PLL可以使多个时钟保持一定的相位关系。

- 时钟复用 - 一个PLL可以驱动多个时钟域。

PLL的工作原理是通过控制环路内VCO的相位和频率实现以上功能。

在FPGA中,PLL广泛用于:

- 生成界面、存储等需要的各种工作时钟

- 将外部时钟处理后提供低抖动时钟

- 实现模块间的时钟域同步

PLL提供时钟的稳定性和灵活性,是FPGA设计中必不可少的时钟管理机制

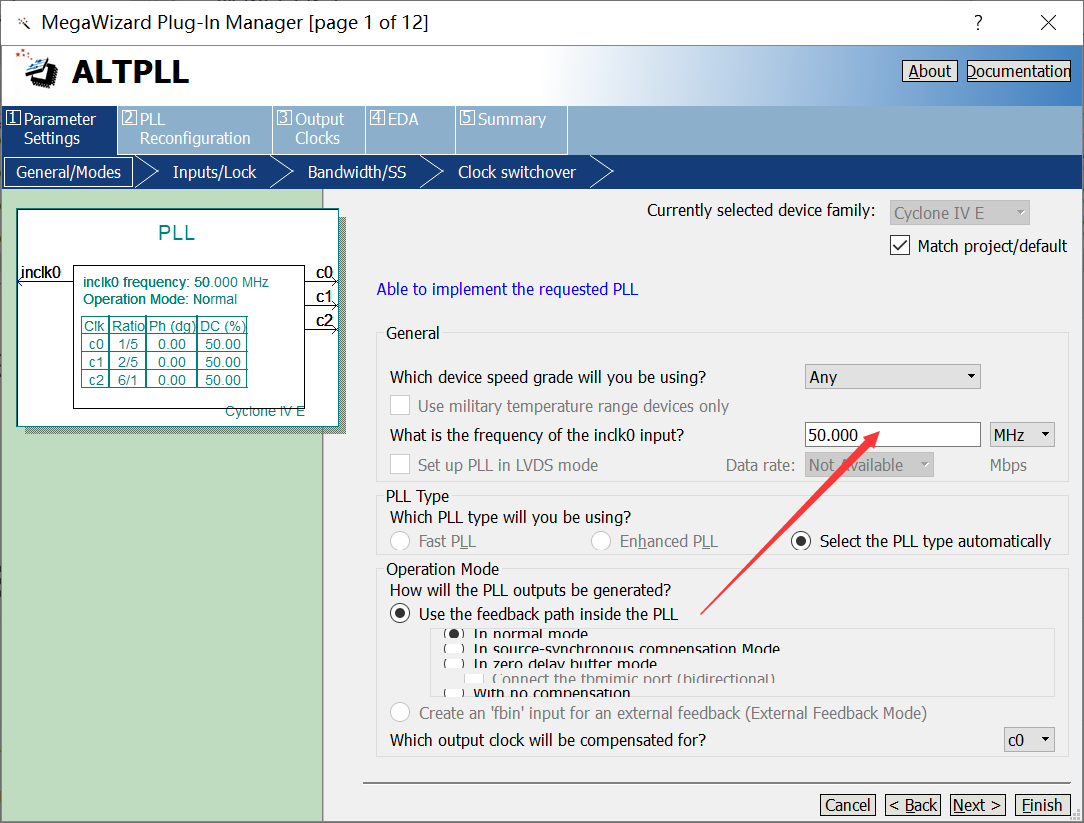

2、具体实现配置

选中点击打开后会出现以下配置界面,配置自己芯片的时钟频率,我这里配置的是50MHZ

取消勾选掉多余的信号

本文介绍了如何在Quartus工具中使用PLLIP核进行时钟管理,包括配置PLL以生成不同频率的时钟信号,如10MHz、20MHz和300MHz,并展示了如何进行仿真验证。PLL在FPGA设计中用于频率合成、分频、减少时钟抖动等功能,是关键的时钟管理机制。

本文介绍了如何在Quartus工具中使用PLLIP核进行时钟管理,包括配置PLL以生成不同频率的时钟信号,如10MHz、20MHz和300MHz,并展示了如何进行仿真验证。PLL在FPGA设计中用于频率合成、分频、减少时钟抖动等功能,是关键的时钟管理机制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2829

2829

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?