目录

前言

第一次接触xilinx系列的zynq,首先拿到手那就按照惯例,先点个灯开始FPGA的劝退之旅

一、系统设计

这一步需要明确按键跟led的链接关系。首先明确需求,按下按键led灯亮,根据这个需求设计。

1.原理图查找

如下图,左侧为按键原理图,可以看到按键是被外部下拉的,按下为高,右侧为LED原理图,想要LED灯亮需要输出高电平进行驱动。

因此可以确定连接关系,LED = KEY

二、创建工程

1.创建vivado工程文件

创建一个新工程

创建工程名字以及路径

直接默认第一个

需不需要添加 verilog代码,没有直接跳过

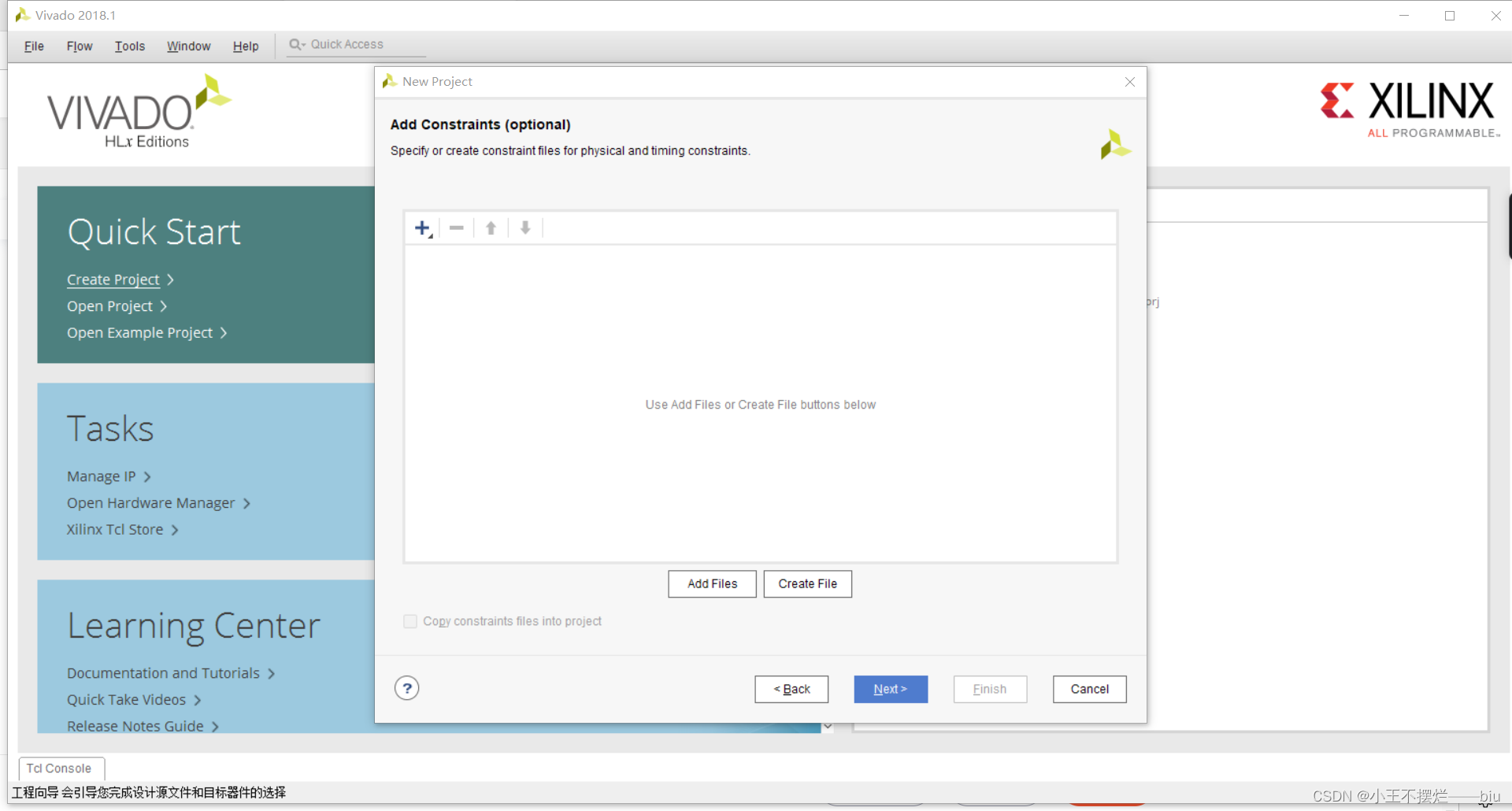

需不需要添加约束文件,比如引脚约束,或者时序约束

选择芯片型号-zedboard是xc7z020clg484 -1

创建verilog代码

双击创建的文件编写如下代码

module led(

input key ,

output led

);

assign led = key;

endmodule

2.编写约束文件

如上图(T18,T22都是根据原理图来设计的引脚驱动电压也是根据原理图来的)设置完之后就会自动生成约束文件如下图:

set_property PACKAGE_PIN T18 [get_ports key] set_property PACKAGE_PIN T22 [get_ports led] set_property IOSTANDARD LVCMOS33 [get_ports led] set_property IOSTANDARD LVCMOS18 [get_ports key] set_property DRIVE 12 [get_ports led]或者直接查看官方提供的约束文件如下图:NET BTNU LOC = T18 | IOSTANDARD=LVCMOS18; # "BTNU" NET LD0 LOC = T22 | IOSTANDARD=LVCMOS33; # "LD0"

三.生成比特流编译

都是默认就好,接下来就是等待了 ,等右上角那个圈圈转完就可以了

完成之后接通开发板电源接上usb烧录线进行如下操作

四.总结

第一次做主要是记录个流程下来,希望这个板子不会是我的劝退板子

150

150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?