一、实验目的

1、 首先基于Quartus 软件采用原理图输入方法完成一个1位全加器的设计。

然后通过4个1位全加器的串行级联,完成一个4位全加器的原理图设计;再改用 Verilog编程(3种模式:门电路、数据流和行为级描述),完成这个4位全加器设计,并观察Verilog代码编译综合后生成的 RTL电路,与之前电路图设计的4位全加器电路进行对比 。

2、编写 测试激励Verilog模块,用Modelsim 对4位全加器 Verilog模块进行仿真测试,观察仿真波形图。

如果仿真波形的逻辑功能正确,就连接的实验室 DE2-115开发板硬件上,完成引脚绑定,烧录,再拨动按钮开关,进行加法器 正确性的验证。

一位全加器原理

一位全加器可以看作由两个半加器组成,其中一个用于计算当前位的求和位,另一个用于计算进位位。全加器在多位加法器中使用,以实现多位数之间的加法运算。

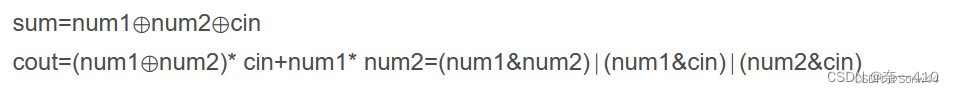

一位全加器输出公式

二、实现一位全加器

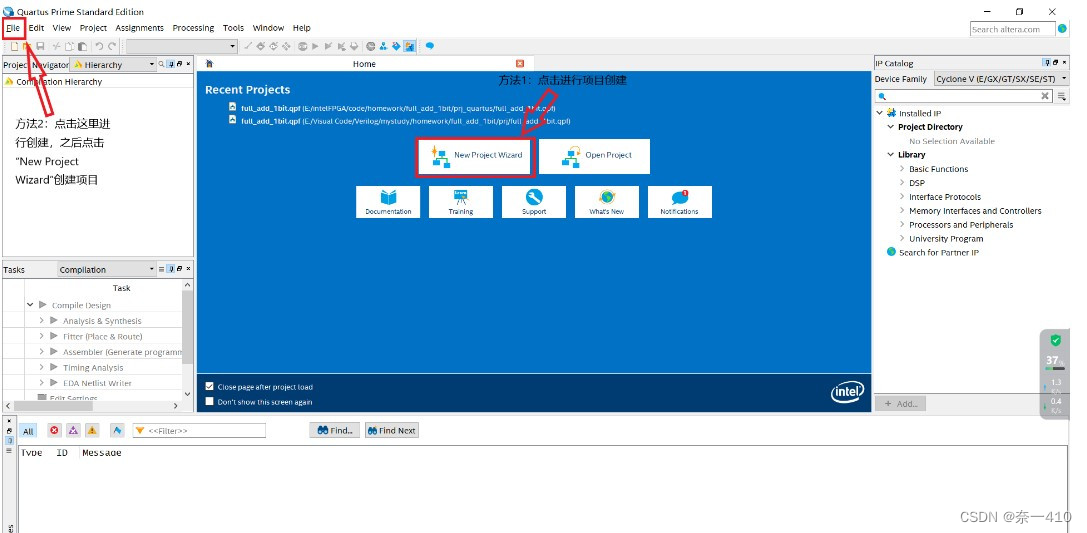

1、在Quartus中新建项目

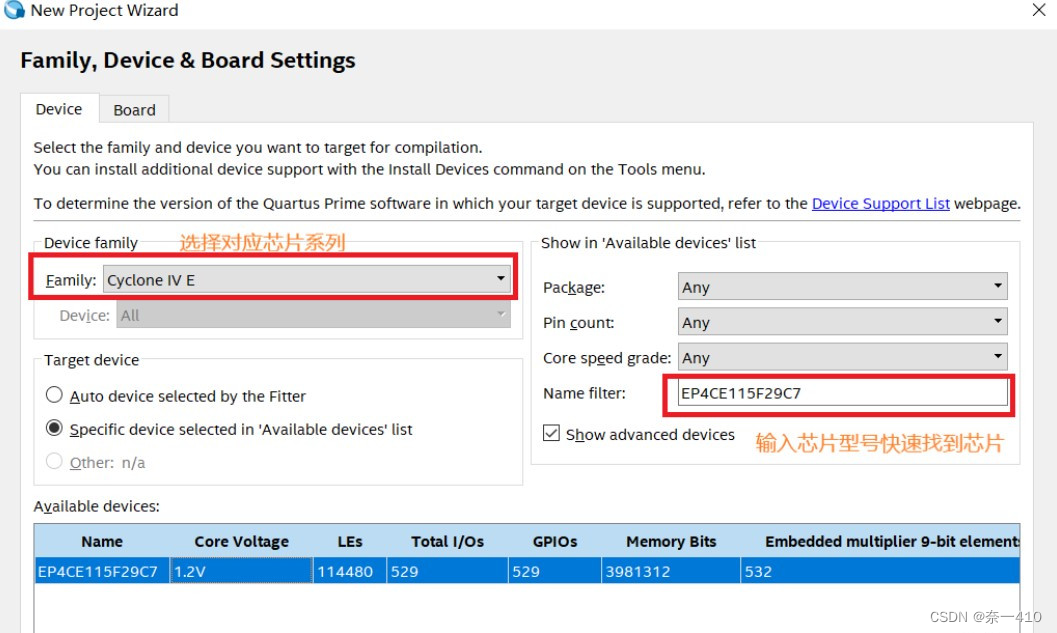

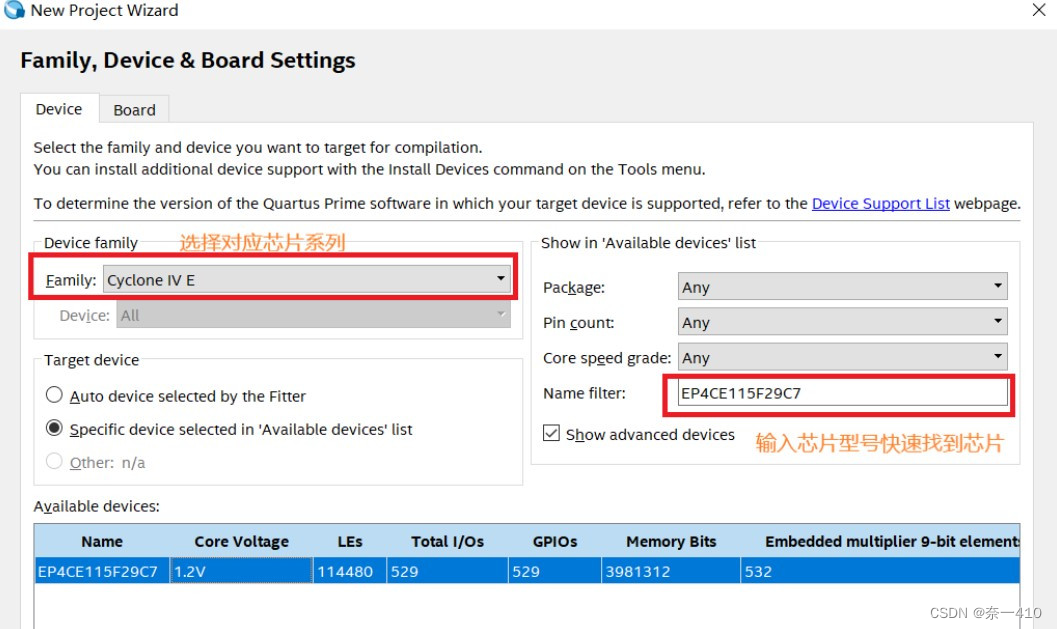

2、然后在出现的界面中填写工程的路径和名称,我这里创建的项目名称为full_add_1bit;接着选择需要的芯片,然后接着Next,直到Finish,完成工程的创建。

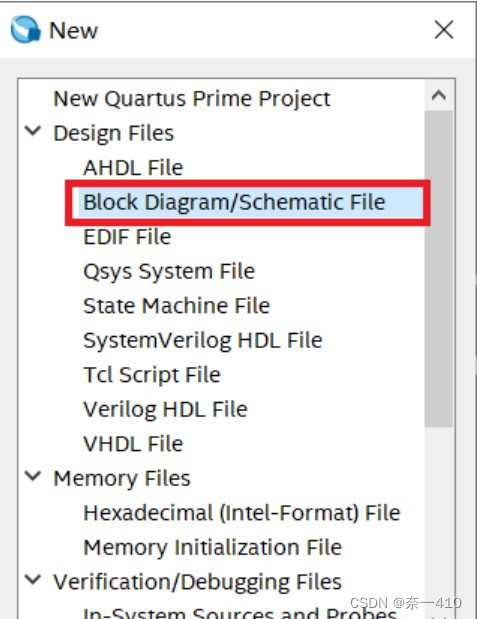

3、在构建好的项目中点击File->New新建如下文件来绘制原理图

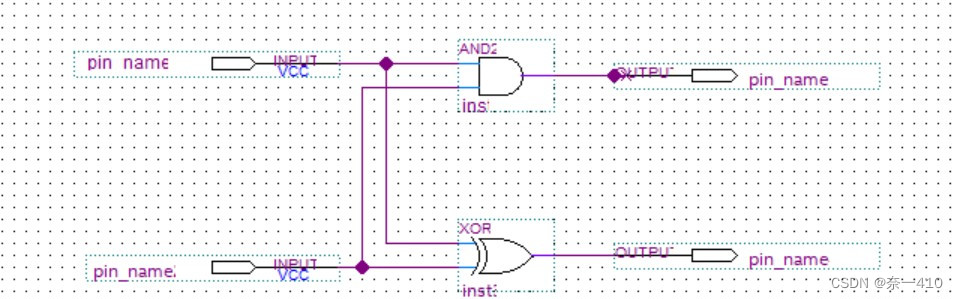

4、根据一位加法器原理图选择组件绘制电路图

双击器件可以修改器件名称,为了之后的试验,将两个input分别修改为num1和num2,and2的输出为cout,xor的输出为sum。绘制好的电路图如下:

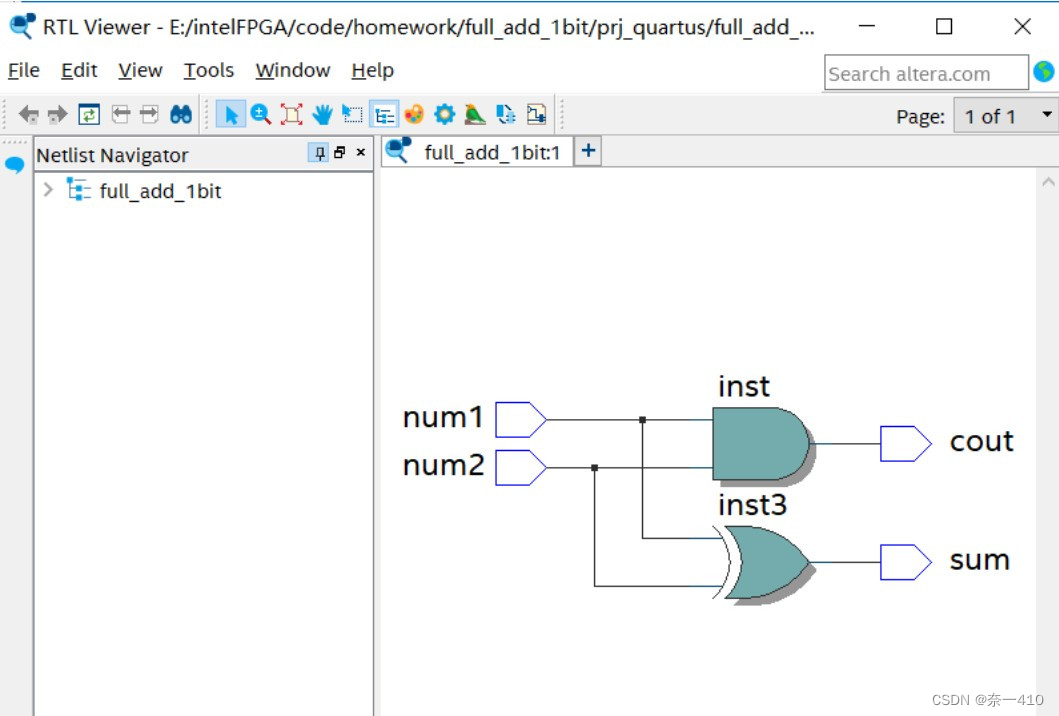

编译电路图,并在Tool->Netlist Viewers->RTL Viewer中查看电路图

三、仿真验证

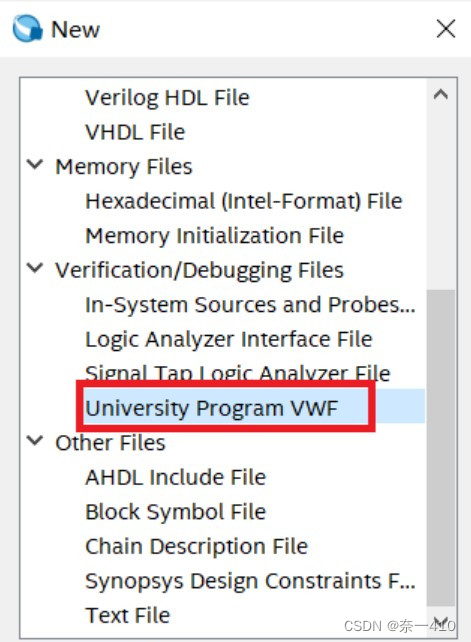

1、创建一个向量波形文件,File->New,然后选择“University Program VWF”

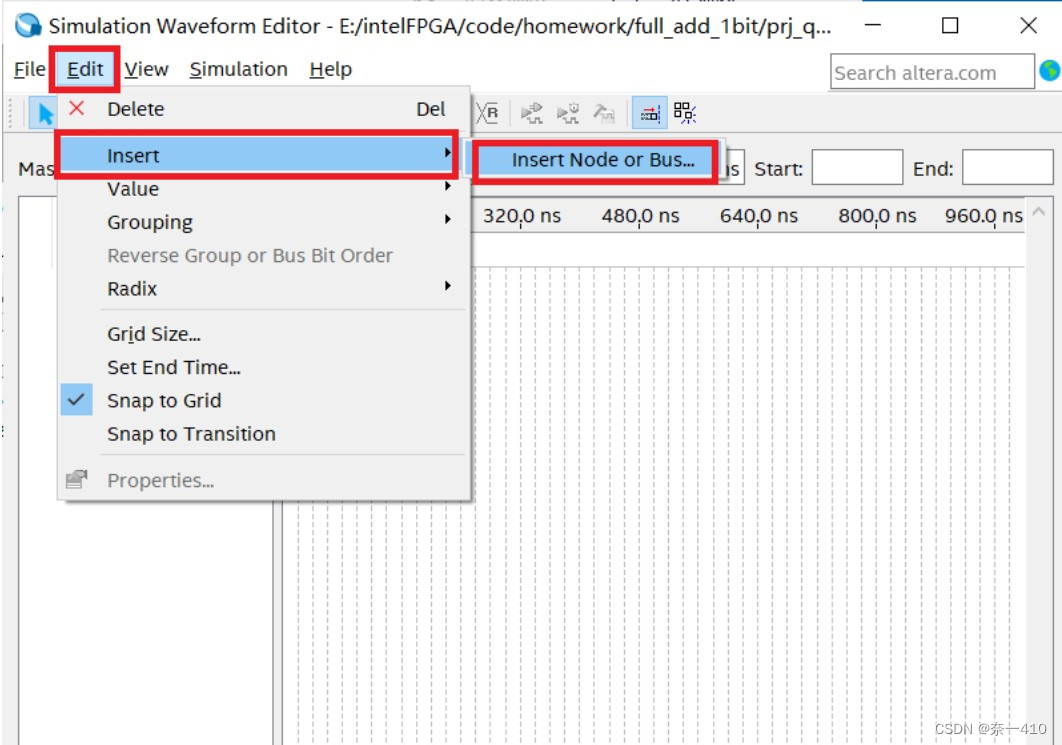

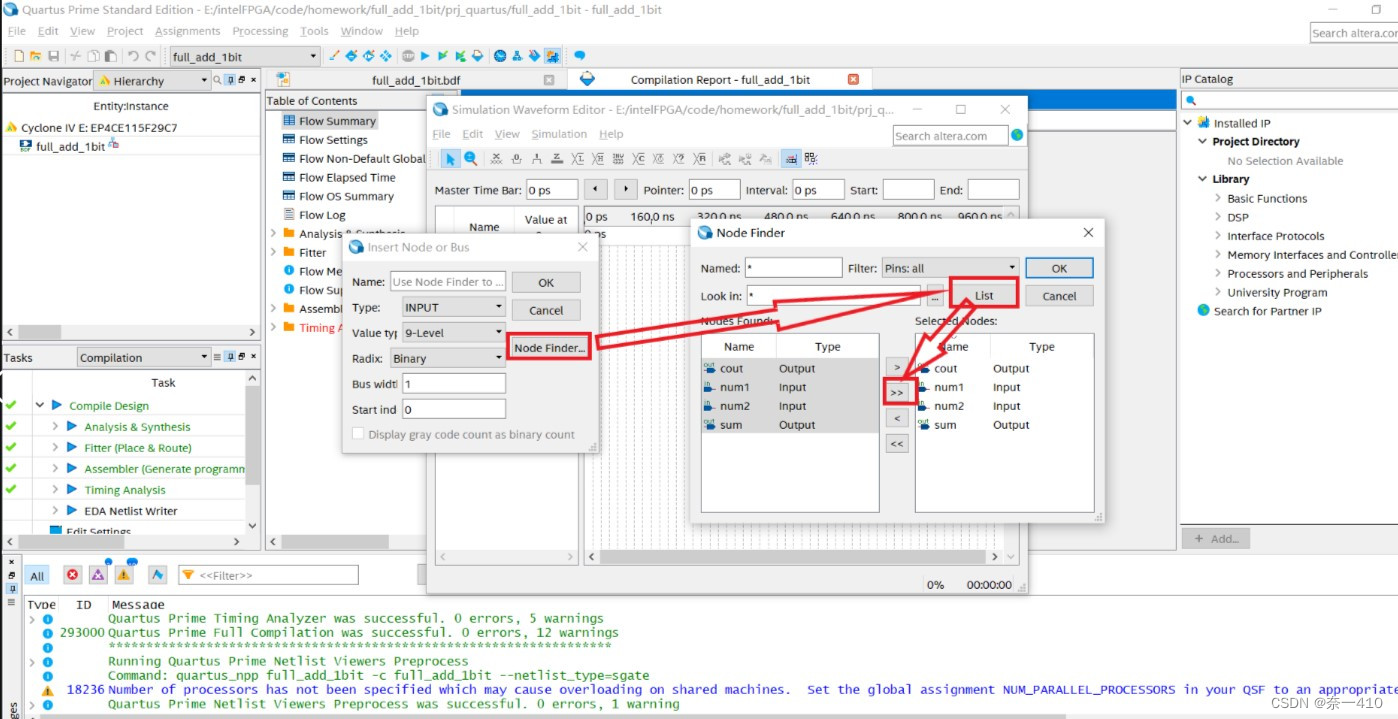

2、在新创建的波形文件中添加前面生成的一位全加器组件

先选择Node Finder这个选项,然后再点击List,之后点击’>>',然后点击两次OK,就可以回到上面的那个界面,并且,此时信号也添加成功了。

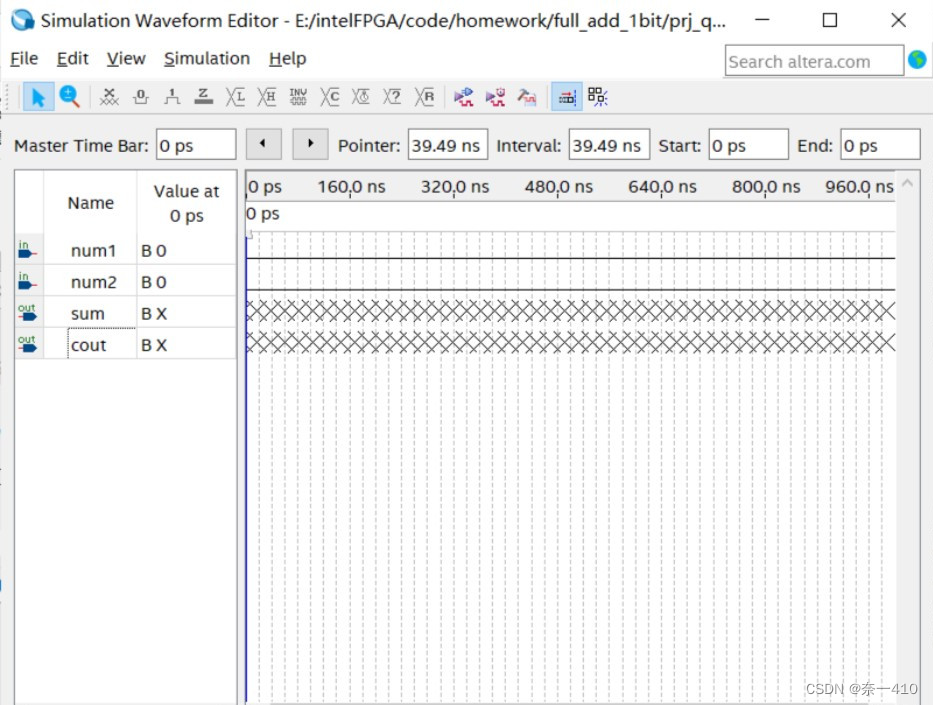

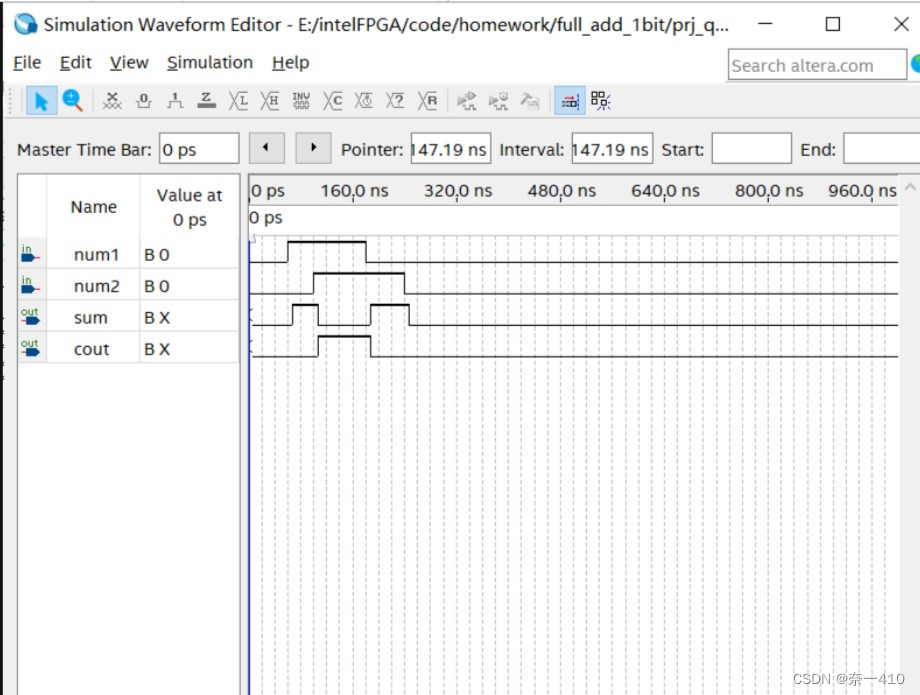

3、添加成功后波形结果如下:

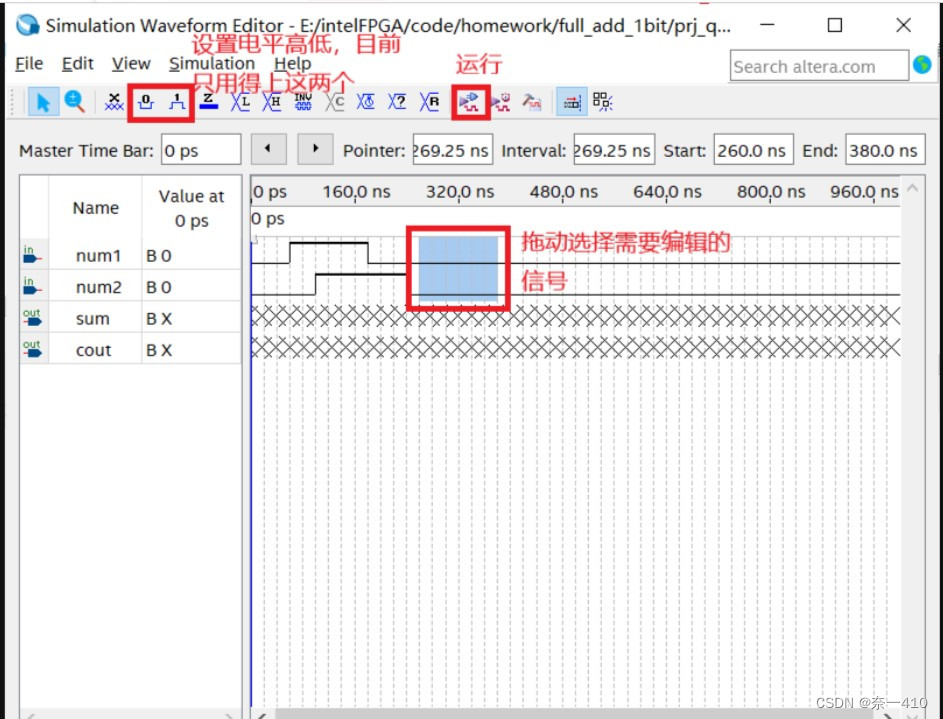

4、对波形信号进行编辑,之后进行仿真检验

5、检验结果如下,对照真值表,发现检验结果符合预期,电路正确,可以进行烧录

四、烧录运行

VID_20231219_205620

417

417

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?