仿真

链接:https://pan.baidu.com/s/1Frhdq1Z4oGQ0xSzELQW4vw

提取码:m8bv

一、实验目的

1、通过实验,能熟练掌握信号发生器、示波器、字信号发生器和逻辑分析仪等常见仪器的使用,并能使用上述器件构建电路仿真所需的输入信号、查看仿真的结果输出;

2、通过实验,加深对译码器、数据选择器等常见集成组合逻辑电路的理解,掌握有上述集成器件的电路的分析和设计方法,并能在multisim中完成相关的仿真验证;

二、实验原理

1、“8-3”编码器、“3-8”译码器,8选一数据选择器、七段数码显示译码器的功能表见教材相关章节;

2、数据选择器和译码器实现逻辑电路见教材对应章节;

3、利用组合逻辑电路分析步骤及原理分析给定逻辑电路功能,并在multisim中实现该电路的功能仿真和验证;

4、根据组合逻辑电路设计步骤和原理设计给定功能的组合逻辑电路,并完成其功能仿真及验证。

三、实验设备和器材

电脑、multisim电路仿真软件(版本不限)

四、实验内容和步骤

4.1 编码器

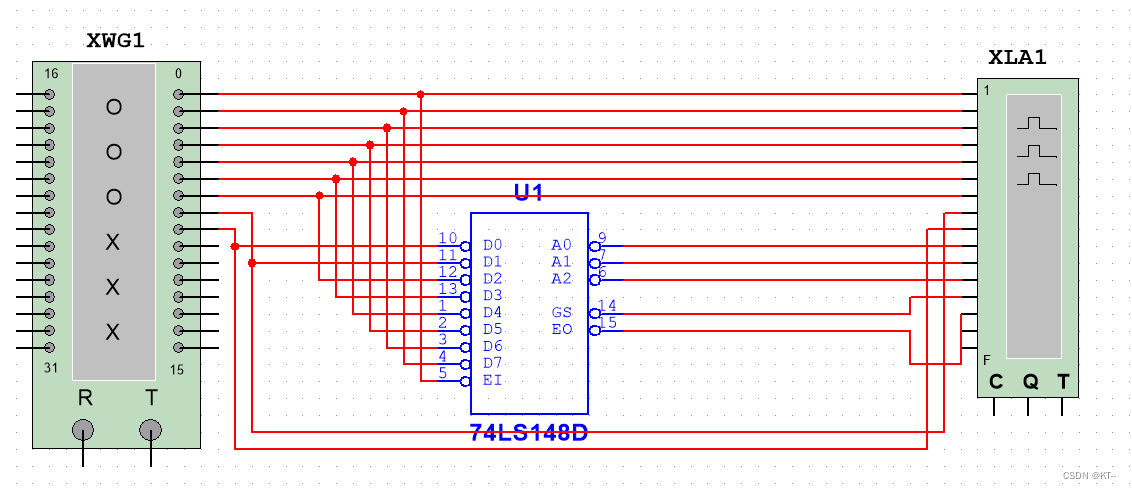

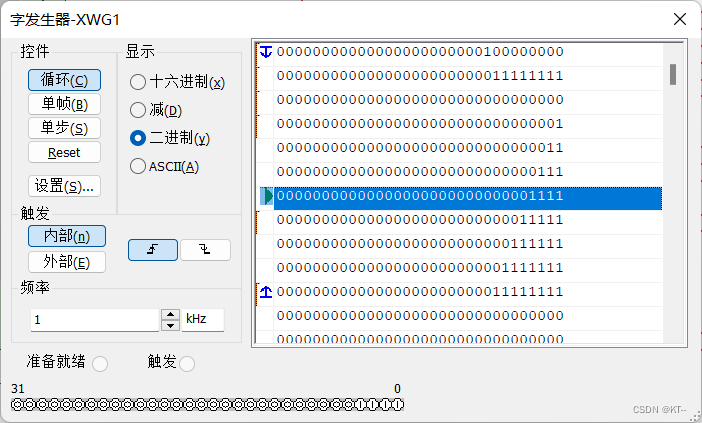

在multisim器件库选择一实现83编码功能的器件,完成下面实验内容;

1.使用相关器件和仪器,完成83编码器的功能仿真和验证,并记录实验相关内容(预习时自行完成);

2.使用选定的83编码器,实现一三人表决电路,并完成该电路的功能仿真与验证,记录相关实验内容;

4.2 译码器

1.在multisim中选择一38译码器,完成下面实验内容:

1)使用相关器件和仪器,完成38译码器的功能仿真和验证,并记录实验相关内容(预习时自行完成);

2)使用选定的38译码器,实现一三人表决电路,并完成该电路的功能仿真与验证,记录相关实验内容;

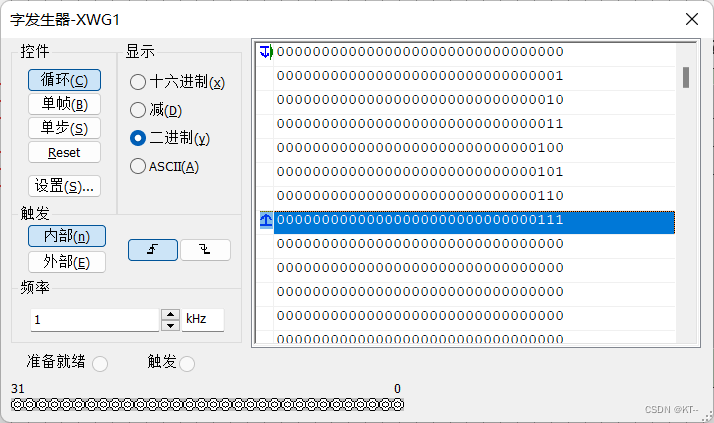

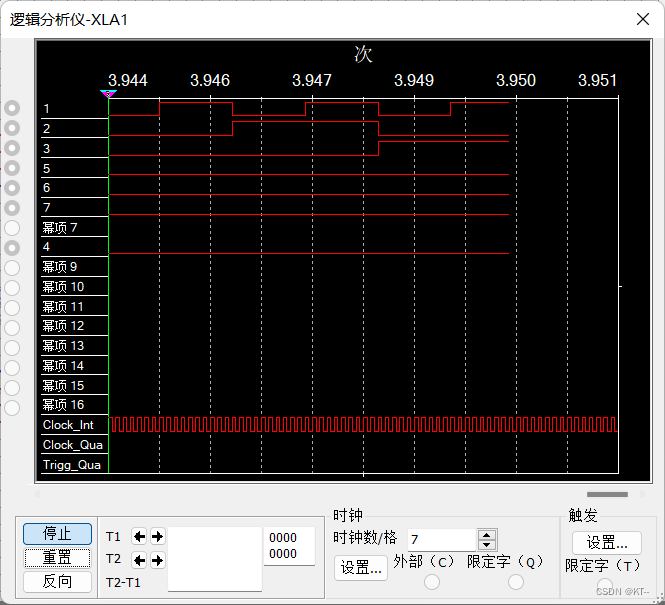

2. 在multisim中选择一七段数码译码器,完成下面实验内容:

1)使用相关器件和仪器,完成七段数码译码器的功能仿真和验证,并记录实验相关内容(预习时自行完成);

2)设计一电路完成一位数码显示电路,能显示以8421BCD码形式给出的任意一个十进制数,要求使用选定的数码译码器完成,并完成该电路的功能仿真与验证,记录相关实验内容;

4.3 数据选择器

在multisim器件库选择八选一数据选择器,完成下面实验内容;

1.使用相关器件和仪器,完成八选一数据选择器的功能仿真和验证,并记录实验相关内容(预习时自行完成);

2.使用选定的八选一数据选择器,实现一三人表决电路,并完成该电路的功能仿真与验证,记录相关实验内容;

五、实验记录和实验结果

5.1 编码器

-

- 给出所选定的编码器的型号、引脚图,给出其功能表,并对功能做简要描述(请预习时完成)

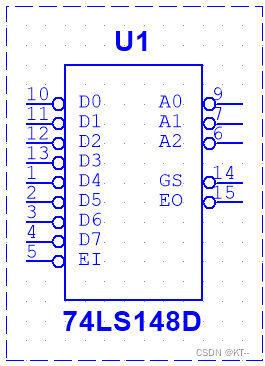

74LS148D

编码器功能:

| 输入 | 输出 | ||||||||||||

| EI | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | A2 | A1 | A0 | GS | EO |

| 1 | X | X | X | X | X | X | X | X | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | X | X | X | X | X | X | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | X | X | X | X | X | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | X | X | X | X | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | X | X | X | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | X | X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | X | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

编码器的逻辑功能就是把输入的每一个高低电平信号编成一个对应的二进制编码。

EI只有是低电平的时候,该芯片才工作;输入7看做是最低位,输入0看做最高位;A2,A1,A0遵循8421码的规律;只要有输入,GS就输出低电平;输入7的优先级最高,输入0的优先级最低,且低电平为有效输入。

-

- 给出使用编码器实现三人表决器过程及设计的电路(预习时完成)

-

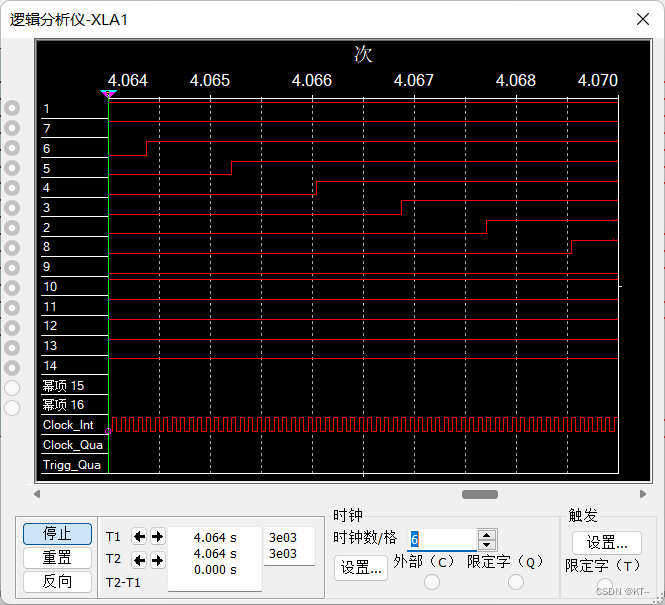

- 在所设计电路基础上,增加适当器件和仪器,实现对所设计电路的功能仿真和验证,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

5.2 译码器

1.38译码器;

1)给出所选定的译码器的型号、引脚图,给出其功能表,并对功能做简要描述(请预习时完成)

2)给出使用译码器器实现三人表决器过程及设计的电路(预习时完成)

3)在所设计电路基础上,增加适当器件和仪器,实现对所设计电路的功能仿真和验证,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

| A | B | C | F |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

此时,将输入放入138只有输出Y3 Y5 Y6 Y7输出为真,将输出为1的连上与非门即可获得三人表决器的输出。

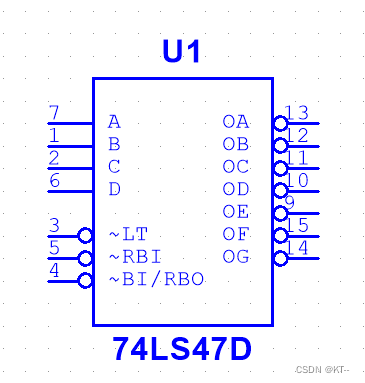

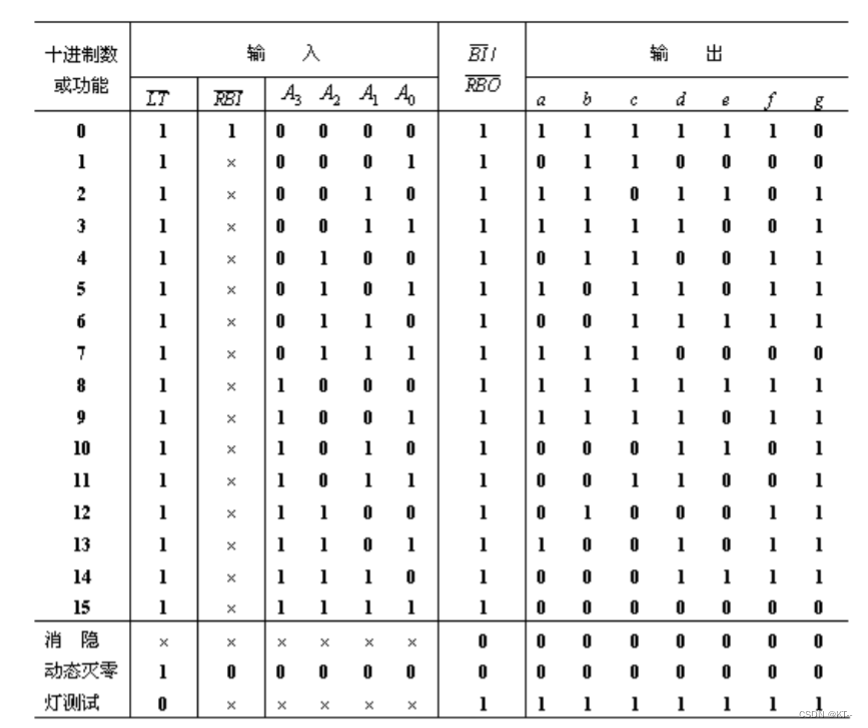

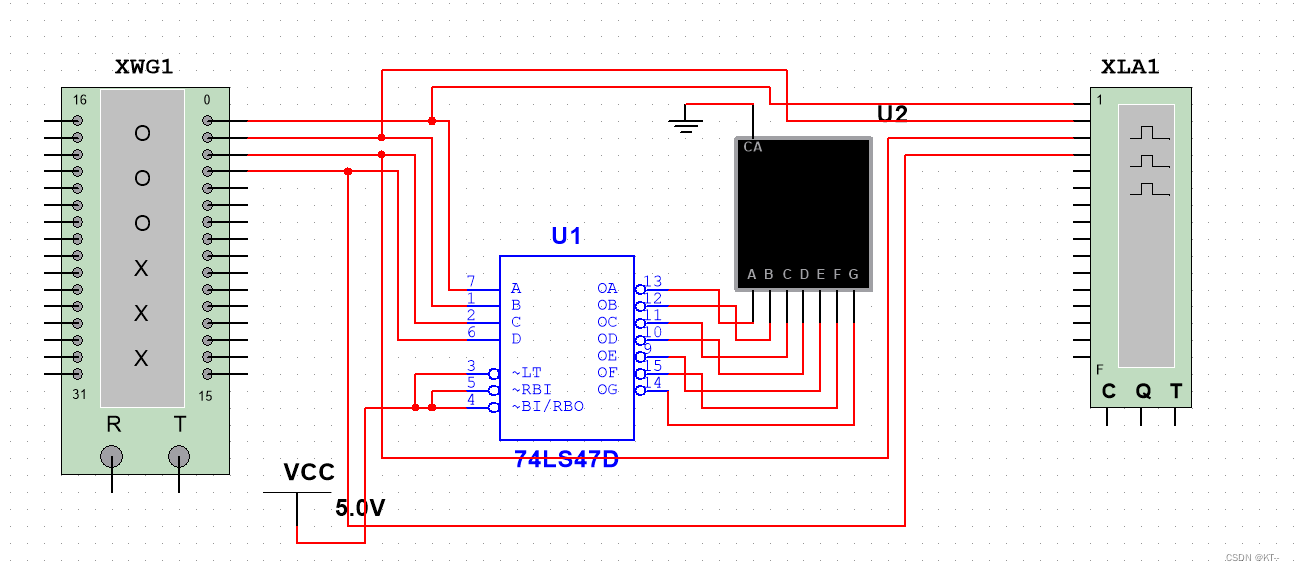

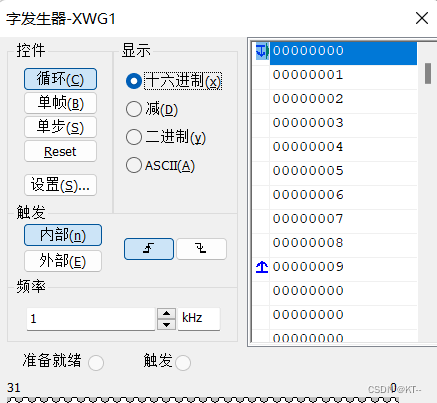

- 七段显示译码器;

1)给出所选定的七段显示译码器的型号、引脚图,给出其功能表,并对功能做简要描述(请预习时完成)

A0~A3 :地址输入端

OA~OG :输出端(低电平有效)

RBI 和BI\ RBO :自动前、后沿灭零控制

LT :试灯

74LS47是BCD-7 段数码管译码器驱动器,74LS47 的功能用于将BCD 码转化成数码块中的数字,通过它来进行解码,可以直接把数字转换为数码管的数字,从而简化了程序,节约了单片机的IO开销。因此是一个非常好的芯片!

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出的高、低电平信号。常用的译码器电路有二进制译码器、二–进制译码器和显示译 码器。译码为编码的逆过程。它将编码时赋予代码的含义“翻译”过来。实现译码的逻辑电路成为译码器。译码器输出与输入代码有唯一的对应关系 74LS47 是输出低电平有效的七段字形译码器,它在这里与数码管配合使用,表2.1列出了74LS47的真值表,表示出了它与数码管之间的关系。

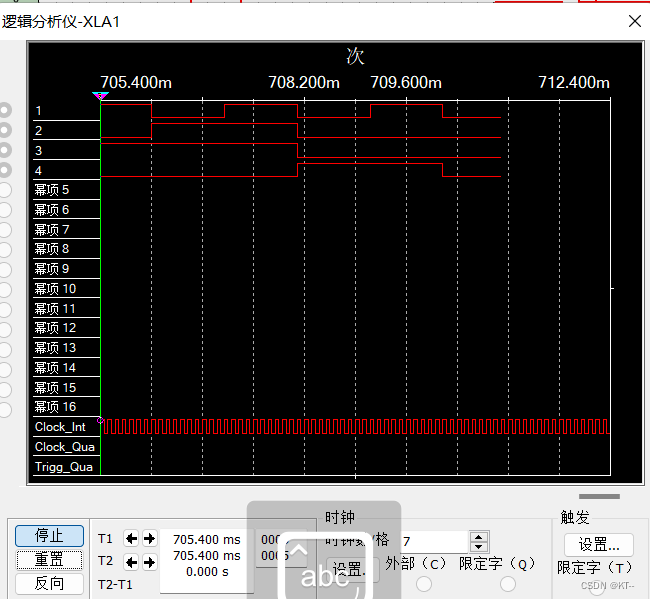

2)给出七段数码显示器的功能仿真和验证电路,并记录其过程及相关数据。

| 输入 | 输出 | |||

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 2 |

| 0 | 0 | 1 | 1 | 3 |

| 0 | 1 | 0 | 0 | 4 |

| 0 | 1 | 0 | 1 | 5 |

| 0 | 1 | 1 | 0 | 6 |

| 0 | 1 | 1 | 1 | 7 |

| 1 | 0 | 0 | 0 | 8 |

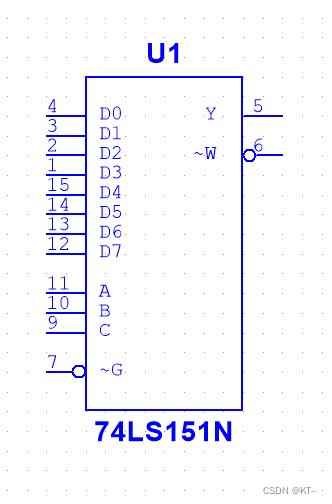

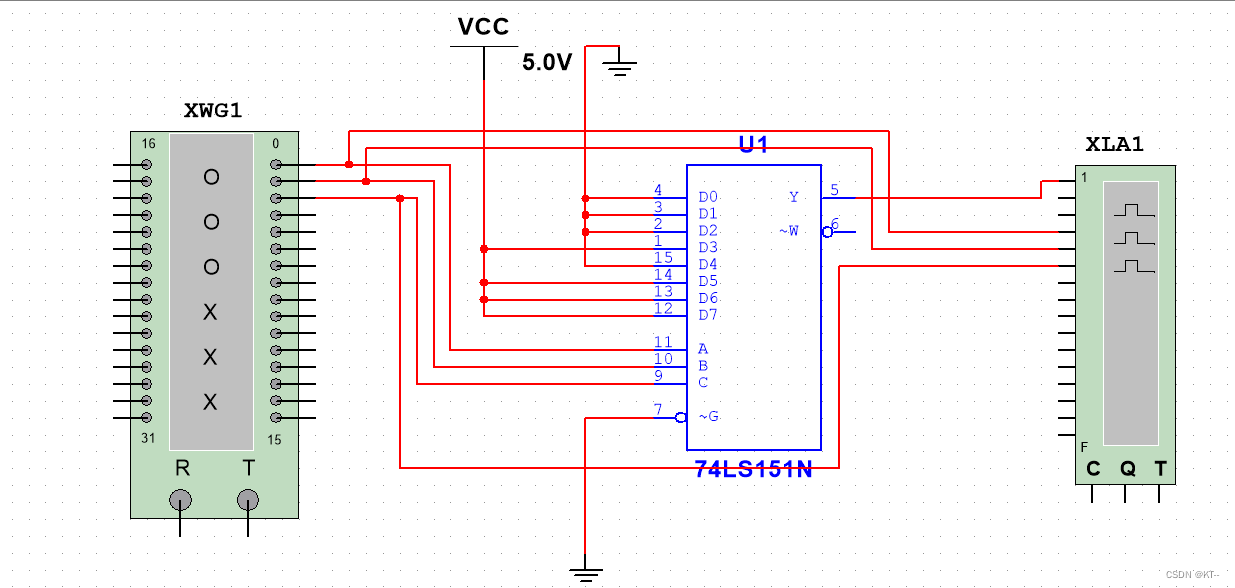

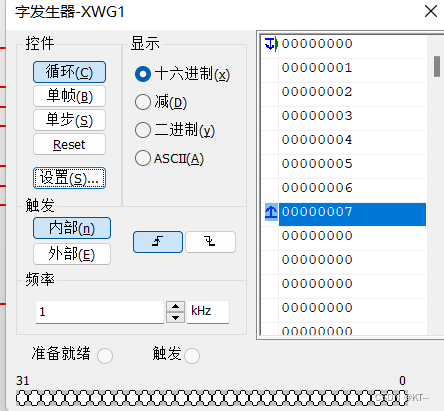

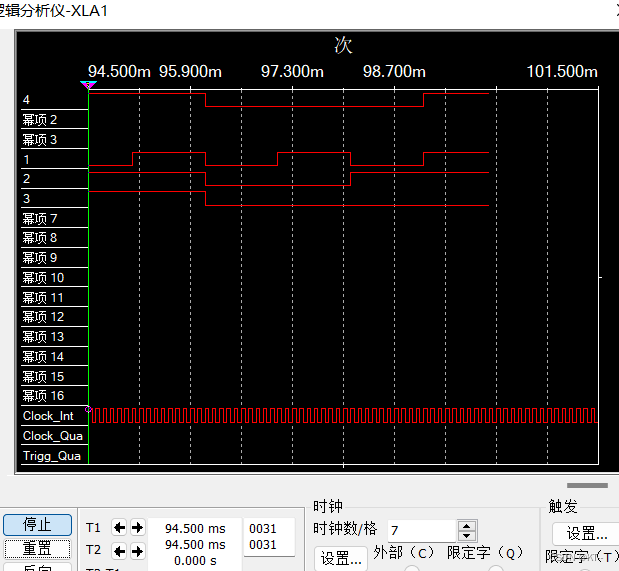

5.3数据选择器

- 给出所选定的数据选择器的型号、引脚图,给出其功能表,并对功能做简要描述(请预习时完成)

- 给出使用数据选择器实现三人表决器过程及设计的电路(预习时完成)

- 在所设计电路基础上,增加适当器件和仪器,实现对所设计电路的功能仿真和验证,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

| A | B | C | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

因为输出Y是由ABC决定的地址输入D,所以可将D0~D7固定为00010111,使得固定D0~D7可输出相应的Y值符合三人表决器,此数据由三人表决器得来:验证其结果是否符合三人表决器,选择ABC分别输入001时,分析可知此时输出Y为0结论符合三人表决器,所以仿真成功

六、实验预习要求

- 实验前认真阅读本实验指导;

- 熟悉multisim中相关操作及相关器件。

- 完成四和五中要求预习时完成的内容。

七、思考题

完成对组合逻辑电路设计、功能仿真及验证的步骤有哪些?

- 根据任务的需求,写出状态循环图;

- 列出真值表;

3、用卡诺图或代数化简法求出最简的逻辑表达式;

4、根据表达式,画出逻辑电路图,用标准器件构成电路;

5、最后,用实验来验证设计的正确性。

2844

2844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?