SDIO的配置问题

1.选好mcu 的选型,配置晶振,调试接口。

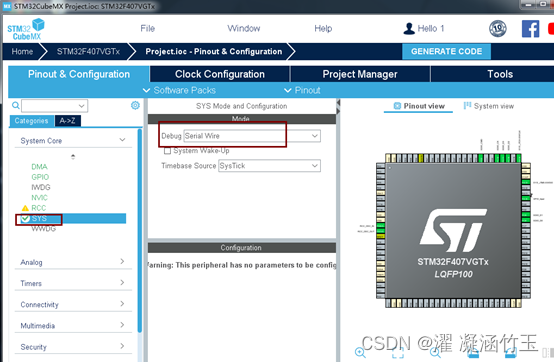

1.1调试接口

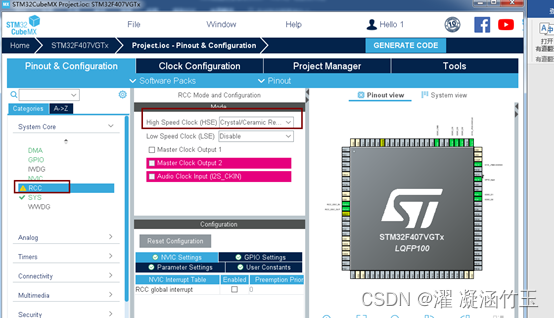

1.2晶振

2.配置时钟频率

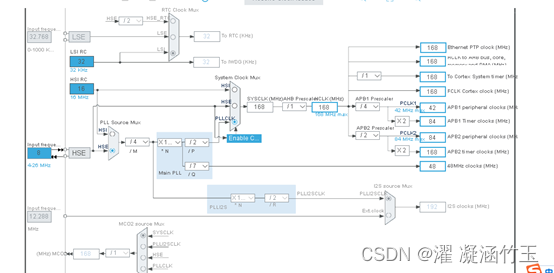

2.1说明

Sd_CLK 时钟是挂载到APB2总线上,从HSE引出,配置好预分频器,倍频器,锁相器,使得APB2总线达到最佳频率。

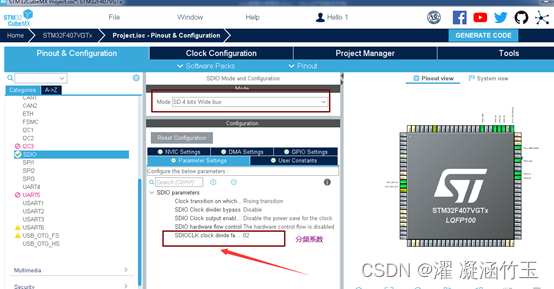

Sd_CLK在0-25M范围,所以需要在sdio配置里,给apb2分频

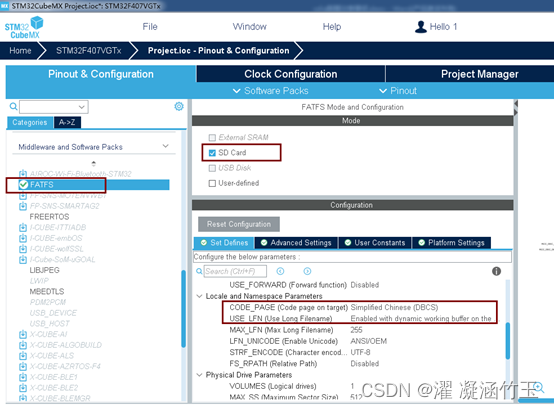

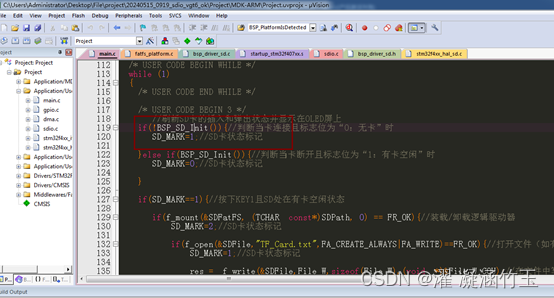

3.挂载文件系统

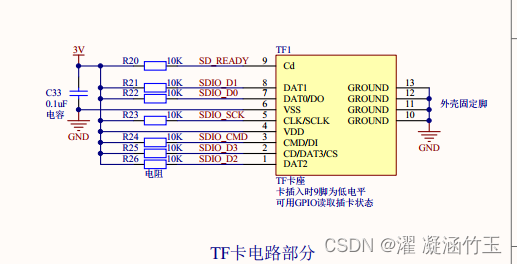

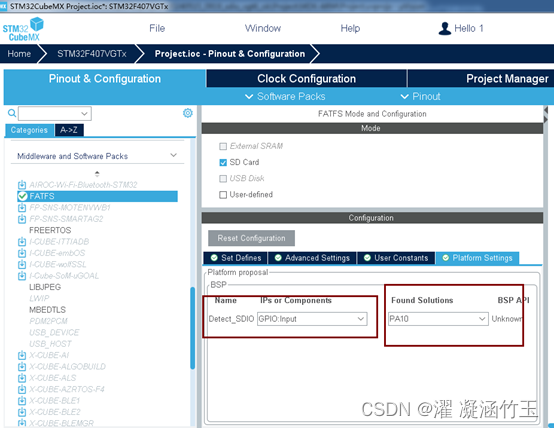

3.1硬件设计

3.1.1SD_READY

3.1.1.1 SD_READY引脚用于识别卡是否插入。空闲时为高电平,被识别时电平拉高。

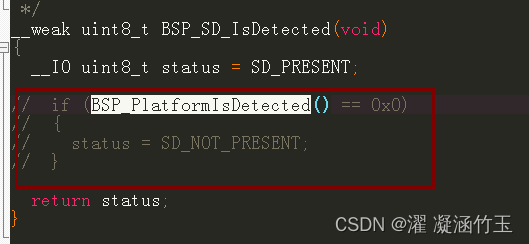

3.1.1.2 如果在硬件设计上没有SD_READY引脚,那就先随便设计一个GPIO的输出模式,再需要注销以下代码

4.软件修改

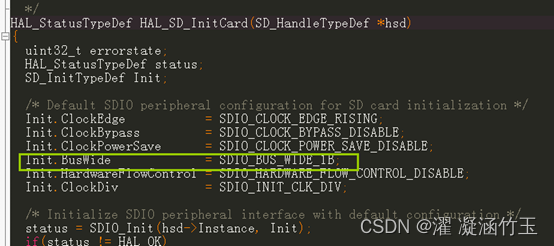

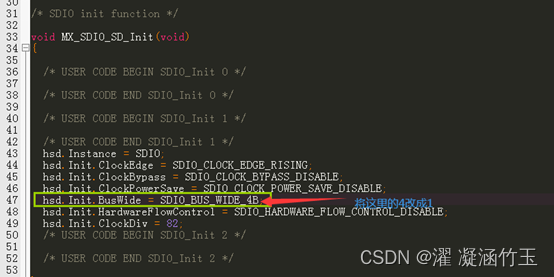

值得注意的是,在新版本的cubemx中,对于四线制的设计存在一个小bug,那就是追到最底层后

BSP_SD_Inità HAL_SD_Inità HAL_SD_InitCard

这里依然是1线制

尝试过改成4线制,依然通不过。所有就需要在最顶层的结构体中修改

至此,对于sdio的配置运行就结束了。

1287

1287

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?