一篇文章简单易懂地搞懂交叉访问存储器

前言

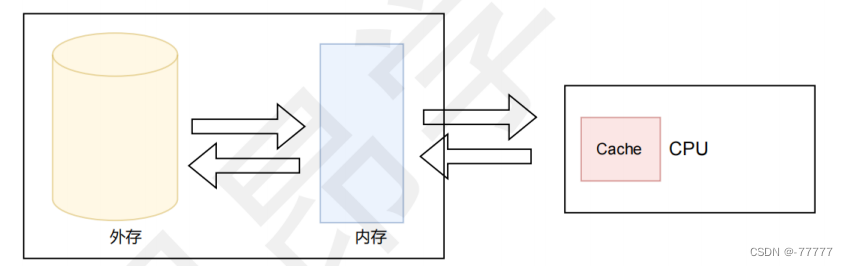

我们知道,CPU速度快,主存慢,两者速度上的差距导致CPU需要等待主存,为此我们需要提高主存的速度。而交叉访问存储器是其中一个改善主存速度的方法,也是最常见的一种方法。下面将 会按照个人的理解详细讲解交叉访问存储器的原理。

一、关于主存

在介绍交叉访问存储器之前,我想先讲一下关于主存。

我们在初学计算机组成原理这门课程的时候,会知道计算机采用的是“存储程序”的工作方式,而存储器相当于计算机的仓库,在运行之前会将要执行的数据和指令先放在主存当中。

通过前文的介绍,我们为了提高主存的速度,采用交叉访问存储器来提高速度。

二、交叉访问存储器

1.交叉访问存储器的介绍

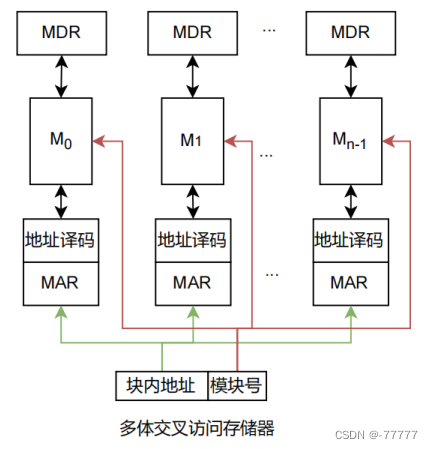

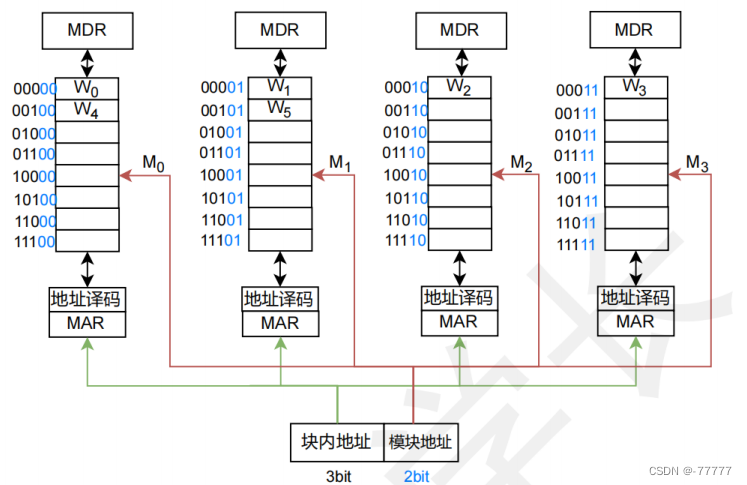

交叉访问存储器采用的是并行结构技术,交叉访问存储器中有多个容量相同的存储模块(也叫做存储体),而各个存储模块具有独立的地址寄存器(MAR)、读写电路和数据寄存器(MDR),这就是多体系统。各个存储体既能并行工作,又能交叉工作。

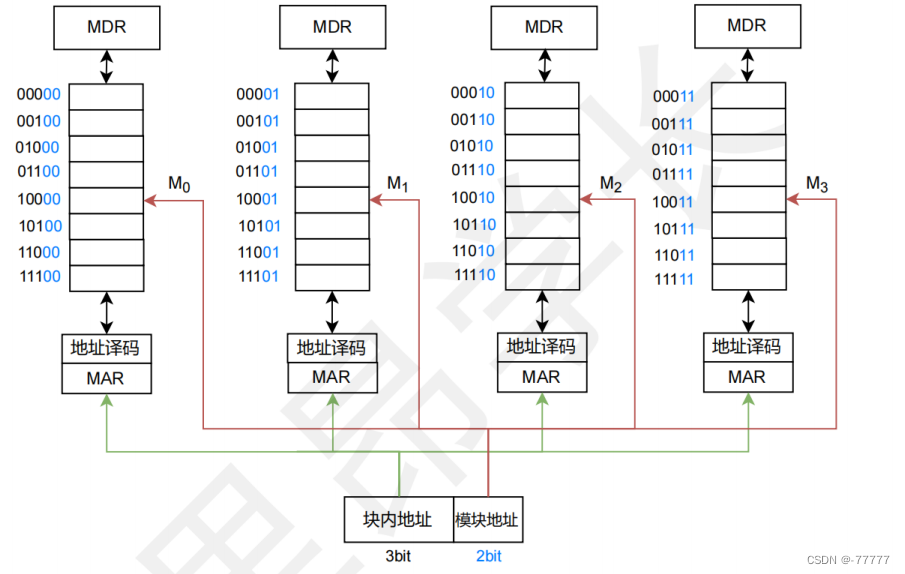

上图中,M0,M1...Mn-1代表了各个存储体,各个存储体都有各个对应的MAR和MDR。而一个二进制序列可以分为块内地址和模块号。首先会根据模块号找到对应的存储体,然后根据块内地址找到对应存储体内的存储单元,从而进行读写操作。

而根据对多个模块编址方式的不同,其组织方式又可以分为高位多体交叉和低位多体交叉。

2.高位多体交叉

高位多体交叉方式的主要目的是扩充存储器的容量。

高位地址译码产生片选信号,选择不同的存储模块。

低位地址选择对应的存储模块内对应的存储单元。

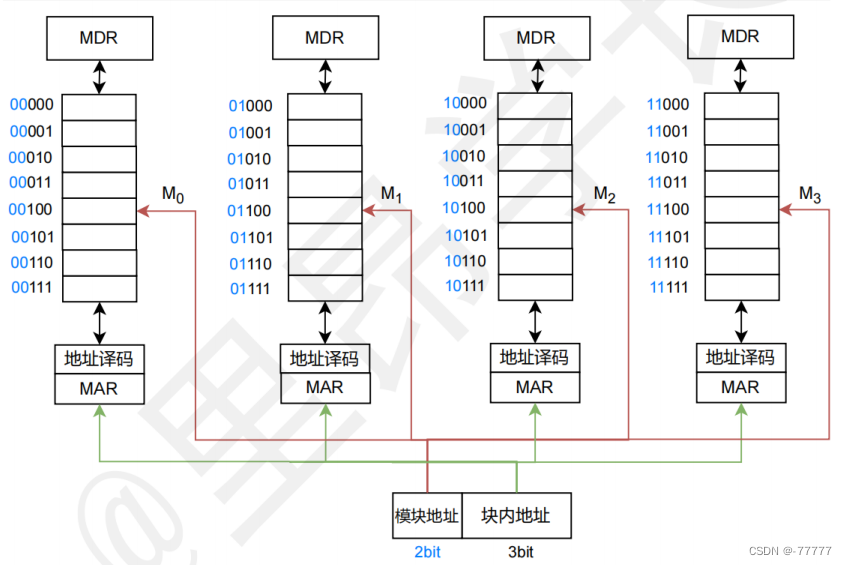

假设在一个5bit的二进制序列中,选择高位2bit为模块地址,低3位为块内地址。

例如,高2位地址为00,对应的十进制为0,此时先选择模块号为M0的存储体。剩下的低3位地址则从000一直到111为止分别对应M0存储体每一个存储单元。又例如高2位地址为01,则对应的十进制为1,此时先选择模块号为M1的存储体,剩下的低3位为地址仍然从000一直到111为止分别对应M1存储体每一个存储单元。

因此,高位交叉方式中不同存储模块对应不同的地址区间,将地支顺序分配给一个存储模块后,按顺序为下一个模块分配地址。因此,高位多体交叉又称为顺序编址模式。

3.低位多体交叉

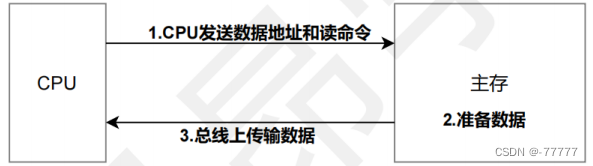

低位多体交叉则与高位多体交叉相反,低位地址作为选择不同的存储模块,而高位地址则对应每个存储模块内的存储单元。

假设在一个5bit的二进制序列中,选择低位2bit为模块地址,高3位为块内地址。

例如,低2位地址为00,对应的十进制为0,此时先选择模块号为M0的存储体。剩下的高3位地址则从000一直到111为止分别对应M0存储体每一个存储单元。又例如低2位地址为01,则对应的十进制为1,此时先选择模块号为M1的存储体,剩下的高3位为地址仍然从000一直到111为止分别对应M1存储体每一个存储单元。

从上图可以清晰地看出,将有序的M个地址依次分配给M个存储模块后,再将下面的M个地址依次分配给M个存储模块,直到将全部地址分配完。因此低位多体交叉又称为交叉编址。

因此上图还可以看出,低位多体交叉有下特点:

相邻的地址处在不同的存储体内,如00000位存储模块M0第一个存储单元的地址,而加1得到00001则变成存储模块M1第一个存储单元的地址。而同一个模块中的地址是不连续的。

4.交叉存储器的作用

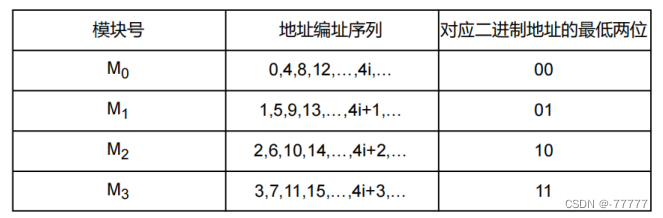

首先先了解一下CPU访存的过程:

1.CPU发送数据地址和读命令,需要花费时间T1

2.存储器接收到地址和命令后,准备数据并将数据送到数据总线上需要花费时间T2

3.总线上传输数据,需要花费时间T3

访问时间一般用读出时间TA和写入时间Tw来表示,TA是指从存储器接到读命令开始至信息被传送到数据线上所需的时间。

因此CPU进行一次数据读取的总时间是T1+T2+T3,其中T2=TA

存储周期:存储器进行一次读写操作所需要的全部时间,由于存储器中有读出放大器、驱动电路等都有一段稳定恢复时间,休息完后才能继续下一次访问操作。因此,存储周期=访问时间+恢复时间。

我们一般会把存储周期看作就是T2。

下面举例子进行说明交叉存储器的作用。

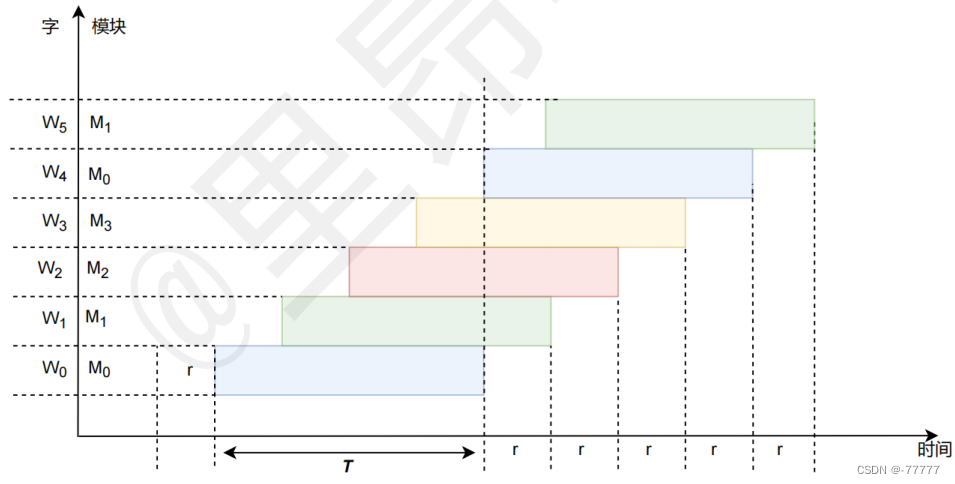

【例】假设我们想要连续访问的地址为0,1,2,3,4,5一共6个存储单元。保存的存储字分别为W0,W1,W2,W3,W4,W5,其中存储周期为T,传输周期为r,(T>r)。设T=4r。给出地址和命令的时间等于r。

1.先考虑高位多体交叉编址的情况。

存储器一般只会关心自己花了多少时间准备数据,因此每一个存储模块准备数据的时间均为T,6个存储模块读取出6个存储字的时间一共为6T。

所有n个存储字读取所需要的时间为nT。

2.我们再考虑低位多体交叉编址的情况。

还是一样,由于存储器一般只会关心自己花了多少时间准备数据,因此每一个存储模块准备数据的时间均为T,但此时读取出6个存储字的时间则变为T+5r。(因为在低位多体交叉编址中,CPU会按照低位交叉编址的方式去进行访问,因此当读取完W0存储体后会读取W1的存储体。因此,当存储体M0在进行准备数据的过程中,过了时间r后便会读取M1存储体,以此类推)

所以,如果读取n个存储字,所需要的时间为T+(n-1)r的时间。

综上所述,在高位多体交叉编址下,读出一个数据的平均时间为t1=nT/n=T

在低位多体交叉编址下,读出一个数据的平均时间为t2=T+(n-1)r/n

当n趋近于正无穷时,此时 t1的极限为T,t2的极限为r。

因此,低位多体交叉编址速度会更快。

5.启动方式

交叉编址多模块存储器有轮流启动和同时启动两种方式。

轮流启动:每个存储体一次读写的位数正好等于系统总线中数据线数,则采用轮流启动方式。(上述讨论的问题都是采用轮流启动的方式)

同时启动:所有模块一次读写操作的总位数正好等于数据总线位数,则采用同时启动所有模块进行读写的方式。

三、题目总结

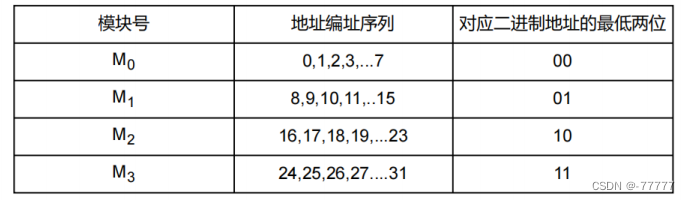

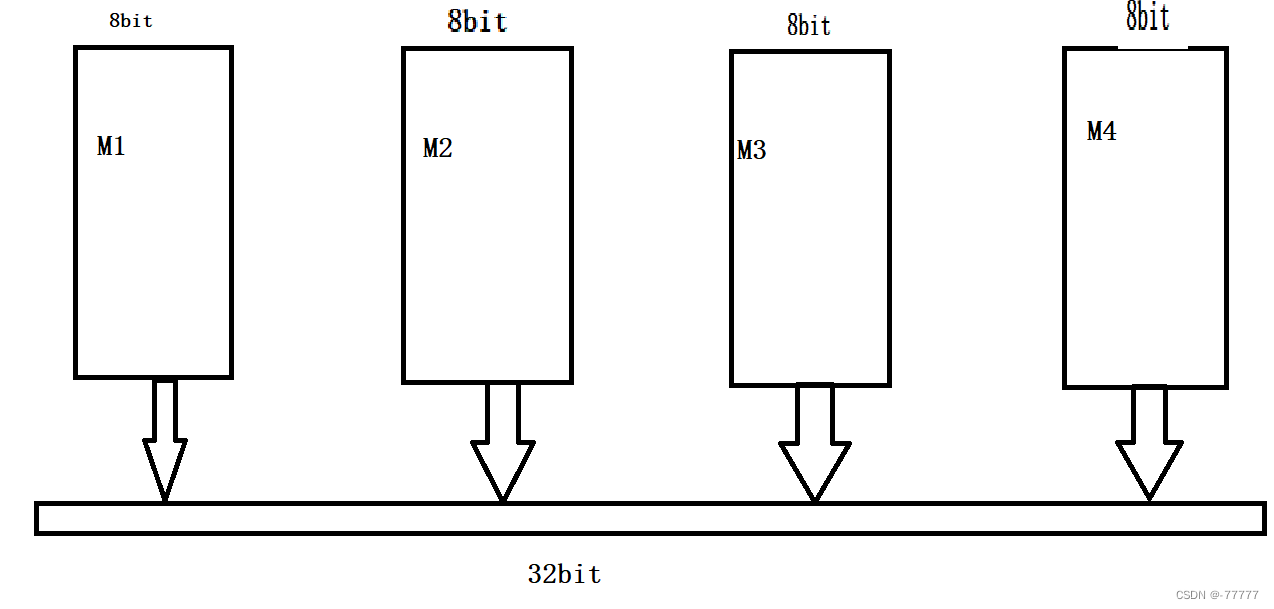

某计算机主存按字节编址,由4个64M×8位的DRAM芯片采用交叉编址方式构成,并与宽度为32位的存储器总线相连,主存每次最多读/写32位数据。若double型变量x的主存地址为804001AH,则读取x需要的存储周期数是()

A.1 B.2 C.3 D.4

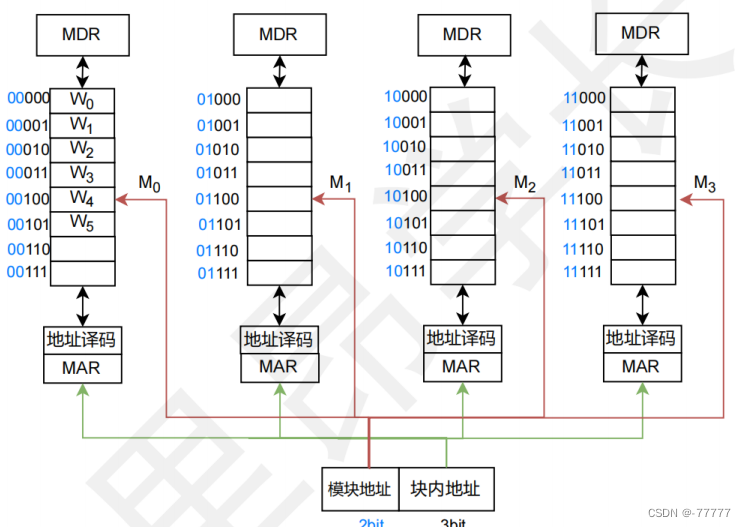

(上图存储体模块号有误,从左到右依次为M0,M1,M2和M3)

首先,每个存储模块能读取的数据为8位,而主存每次能读写32位的数据,且与数据总线的宽度相同,因此,该低位多体交叉编址采用的是同时启动模式。即每次读取会读取32bit(4个存储体)的数据。

由于x变量的主存地址位804001AH为十六进制,先找到最低2位地址确定首个存储体块号。因为最低位A的二进制位1010,因此最低两位为10,对应的存储体块号为M2。

而又因为double类型变量的大小为8B即64位,因此可以画出x的存储情况。

(上图存储体模块号有误,从左到右依次为M0,M1,M2和M3)

由于采用同时启动的方式,因此一个存储周期会读取4B的数据,根据 图可以知道需要3次便能读完8B的数据。即选择C

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?