时序违例分析(三)

文章目录

前言

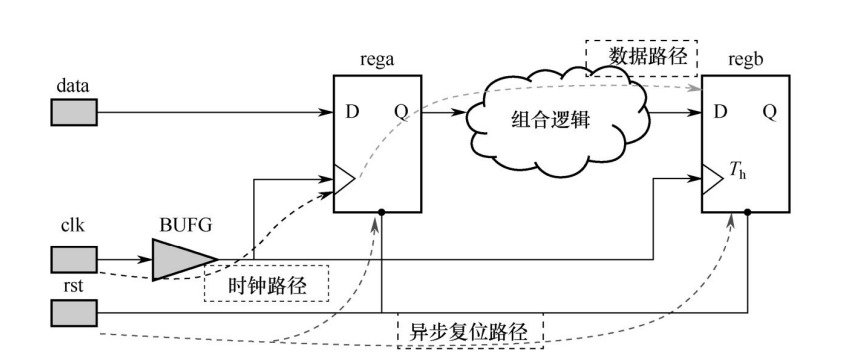

Vivado时序引擎会分析的3类时序路径,包括时钟路径、数据路径和异步复位路径在这里我们将关注点放在数据路径上。数据路径起始于发送触发器的时钟端口,终止于接收触发器的数据端口。事实上,很多时序违例就发生在这类路径上。

这章节只做分析和分析步骤,解决方法再下一篇

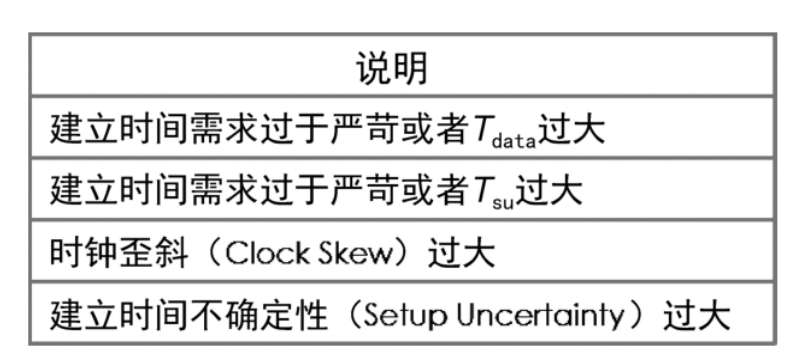

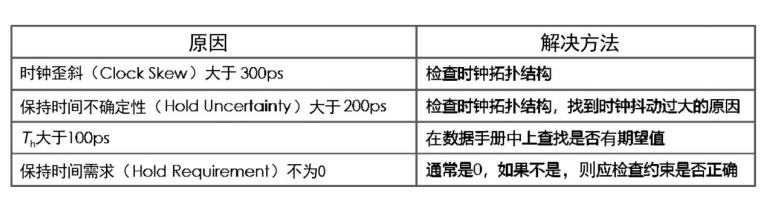

从本质上讲,都是违反以下规则导致时序违例,对于来讲,就看文章具体的分析了

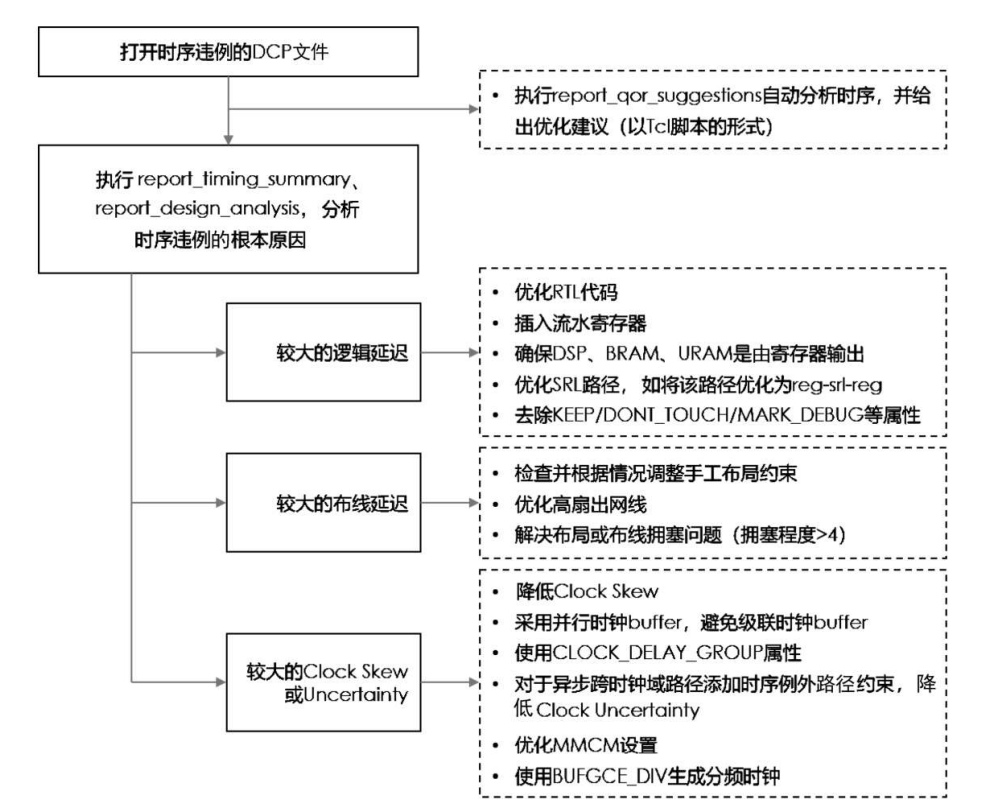

1. 分析步骤总体框架

2. 分析步骤

分为二步

- 软件自动分析

- 手动判断

2.1 软件分析

使用report_qor_suggestions的好处在于工具会自动分析最糟糕的路径,并给出优化建议,同时以Tcl命令的形式给出针对这些建议的实施方

法。设计者可直接使用或参考这些命令。

report_qor_suggestions -outout_dir qor

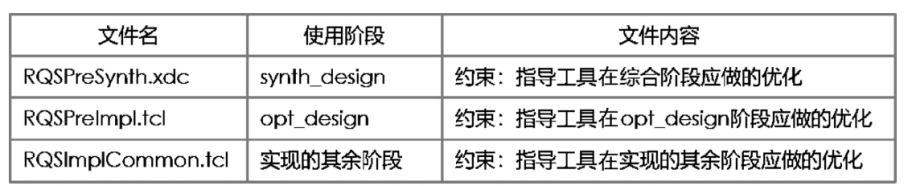

在 Non-Project 模 式 下 , 如 果 设 计 是 从 综 合 阶 段 开 始 执 行 , 则RQSPreSynth.xdc 要 在 综 合 阶 段 之 前 读 入 ,RQSImplCommon.tcl 要 在opt_design阶段之前读入.

注意:这3个文件所做的优化并不会影响设计的功能。

2.2 report_design_analysis

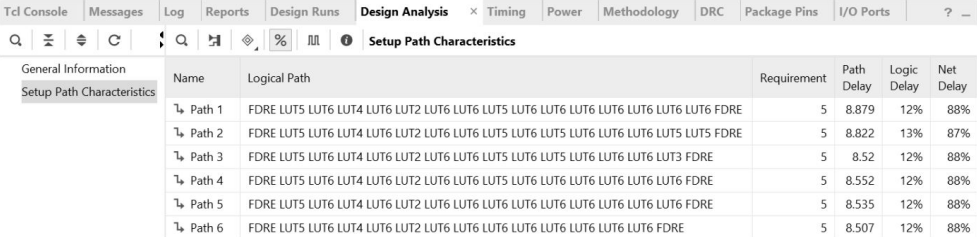

通过report_design_analysis命令可获得路径的逻辑、时序和物理特征(布局、布线),从而简化寻找时序违例根本原因的过程。该命令并不检查时序约束,因此,在运行该命令之前,要保证时序约束正确、合理。

除了图中三个属性,这个条命令生成的其他内容也有很多值得关注的地方

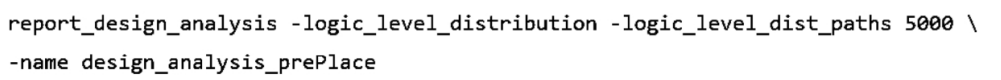

2.3 分析逻辑级数

通常的标准是1个LUT+1根网线的总延迟为500ps,也就是0.5ns,以Tclk表示时钟周期,fclk表示时钟频率,那么对于频率为fclk的时钟,如果该路径的逻辑级数大于floor(Tclk/0.5),则该路径就是长路径(floor表示向下取整)。例如,对于频率为400MHz的时钟,该路径所能承受的最大逻辑级数为2.5/0.5=5。如果逻辑级数大于5,则该路径为长路径。

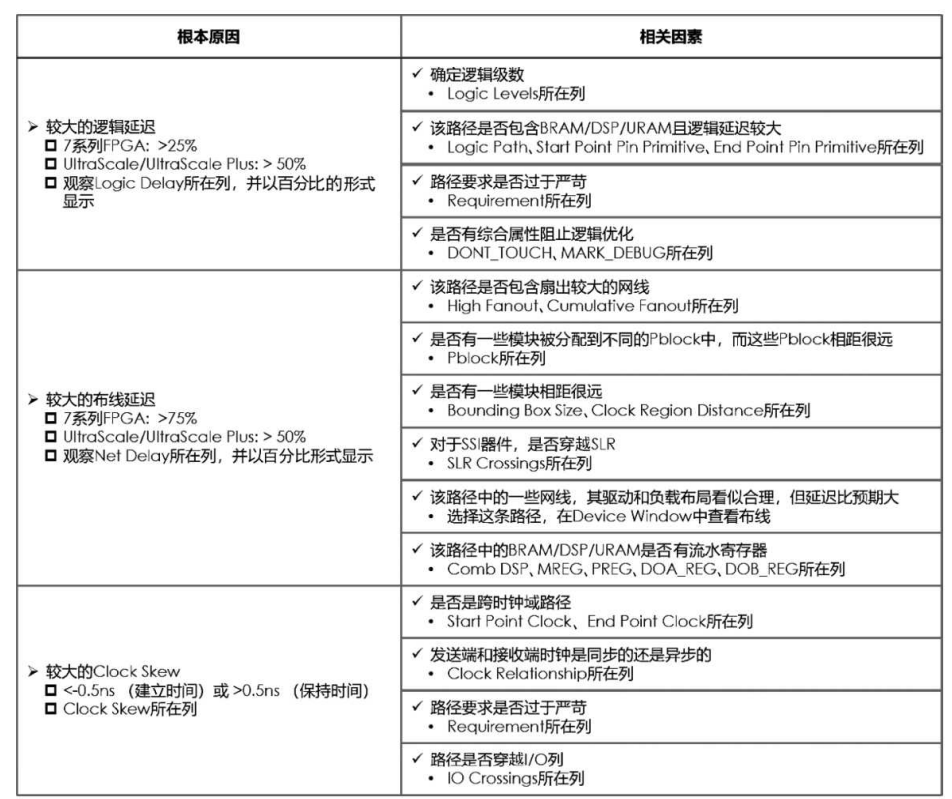

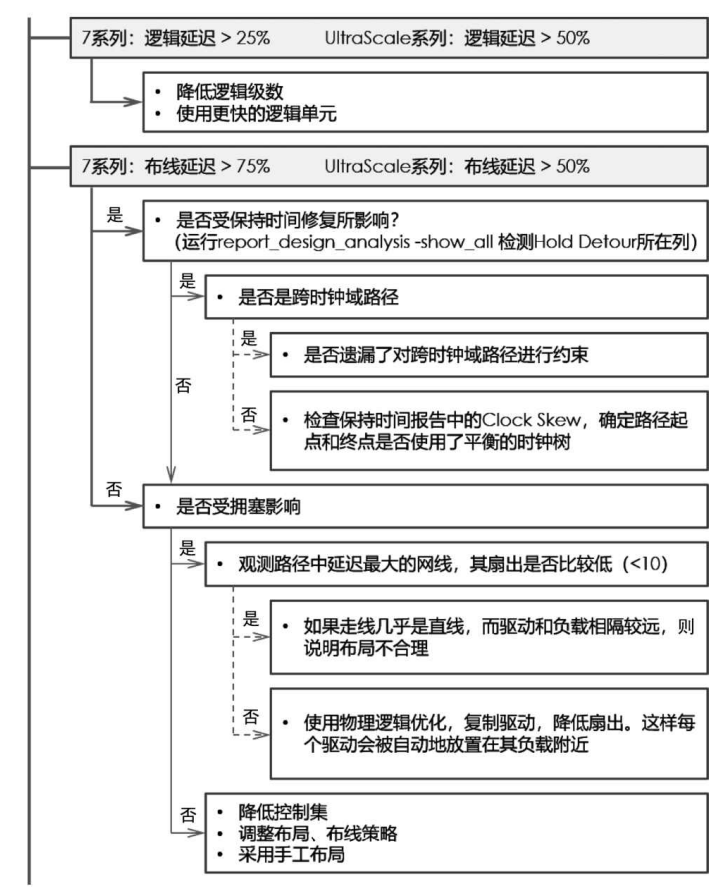

2.4 分析数据路径延迟

2.5 分析时钟歪斜

在高速设计中,例如,时钟频率大于300MHz,则Clock Skew应该小于500ps。毕竟,300MHz对应的时钟周期为3.33ns,500ps几乎是其15%。从逻辑级数的角度而言,500ps就是一级逻辑。在跨时钟域路径(尤其是异步跨时钟域路径)上,Clock Skew可能会更大。这是因为发送时钟和接收时钟来自不同的时钟源。

3788

3788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?