更多知识参考:详解建立时间和保持时间

时序优化

解决时序收敛的问题也是静态时序分析中的主要任务。静态时序分析中可以通过自动和手动两种方式完成物理上和时序上的优化工作,其优化时序的类型主要分为建立时间、保持时间和时序设计规则3种。

解决建立时间不满足的方法:

- 加强约束,重新进行综合,对违规的路径进行进一步的优化,但是一般效果可能不是很明显

- 降低时钟频率,但是这个一般是在项目最初的时候决定的,这个时候很难再改变

- 拆分组合逻辑,插入寄存器,增加流水线,这个是常用方法

- 优化布局布线,减小传输的延时

解决保持时间不满足的方法:

- 增加组合逻辑的处理时间,一般就是在后端的时候插入buffer

- 减少时钟的延时

1.优化建立时间和时序设计规则

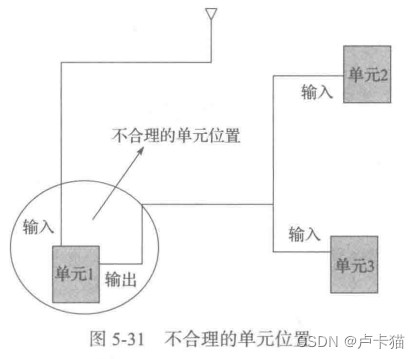

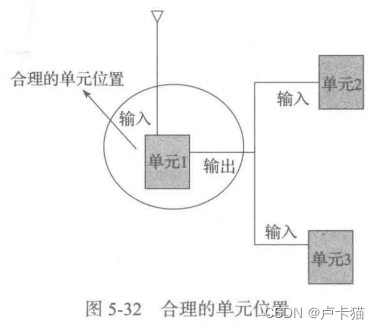

1.1 改变单元位置

不合理的单元物理位置会使信号线过长而导致线负载和线延时变大,从而影响时序收敛。

可以通过优化单元的物理位置来达到提高时序性能的目的

1.2 改变单元的大小

通常标准单元库提供了多种驱动能力的单元。延时随驱动能力增大而递减,因此把由于负载过大导致延时恶化的单元调整为驱动能力更大的同类型单元,可以改变时序性能。

同样,驱动能力小的同类型单元对前级驱动单元所表现的负载电容也较小,将驱动能力大的负载单元换成驱动力小的负载单元,可以减小前级驱动单元的输出负载,从而改善前级驱动单元的时序性能。

总而言之,前级驱动单元可以换成驱动能力大的单元,负载可以换成驱动能力小的单元。

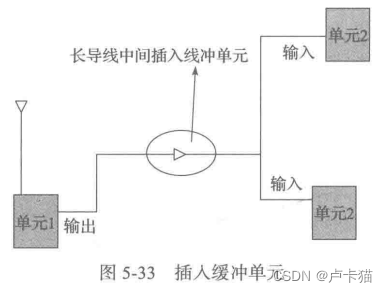

1.3 插入缓冲单元

随着工艺尺寸的不断缩小,其线延时增加与线长近似成正比指数性关系,而增加缓冲单元个数与延时近似成正比线性关系。

在单元位置比较合理,同时单元驱动力已经达到最大时的情况下,如果单元驱动信号线负载仍然过大而导致延时过大的情况,可以通过在长距离信号线中间增加合适的缓冲单元来提高延时性能。

1.4删除缓冲单元

如果设计中存在插入缓冲器单元不合理的情况,那么可以通过删除导致降低时序性能的缓冲单元,来达到优化时序性能的目的。

1.5 重分配负载

在设计中存在扇出(fanout)负载不合理的情况。

可以通过插入缓冲单元重新分配扇出负载来优化时序的目的。

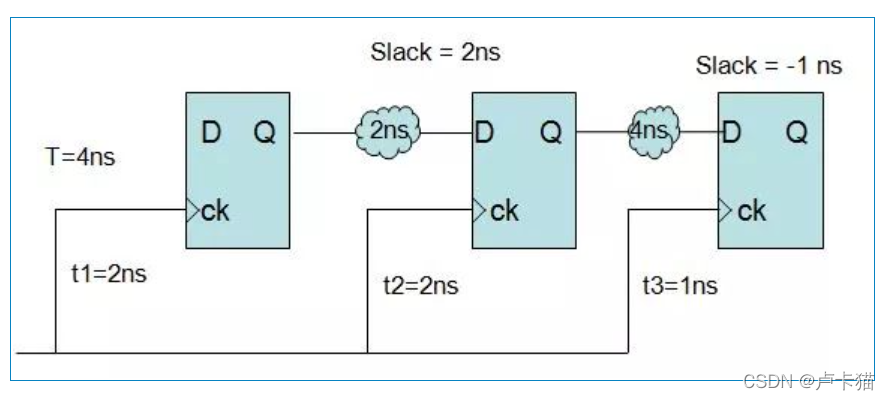

1.6 时钟有用偏斜

现如今用的较多的useful skew,称为有用偏差。skew会恶化timing结果,但如果合理使用,那skew也可以起到修复timing的作用,从而提高设计的频率。

其工作原理就是在两个串行的时序路径中,通过借用其中一条时序路径的延时余量的方法来修复另一条时序路径上时序违反的问题。

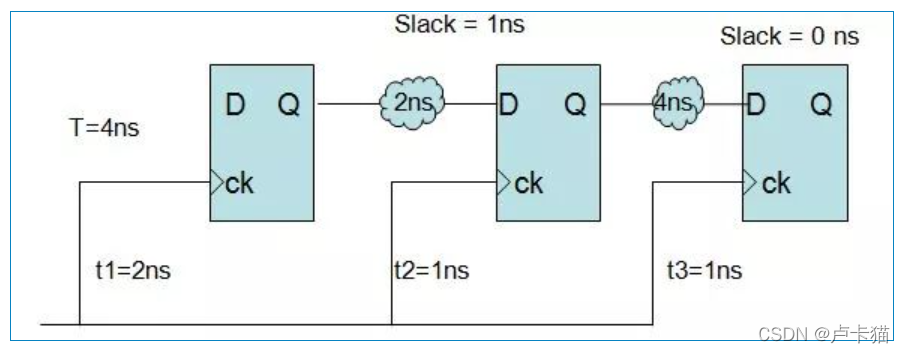

如下图:时钟周期为4ns,各时钟路径延迟如下:可以看到有一条路径的slack为-1ns,说明路径违规。可以看到与这条路径相关的skew是t3-t2=-1ns。

下面我们利用useful skew向前面一个slack比较充裕的路径(slack=2ns)借用1ns的时间,这两条path都meet了时序要求。如下图:

这就是useful skew的作用,可以向前或者向后借time来修正violation

在Aguda工具中,需要设置以下参数:

2.优化保持时间

优化保持时间的方法相对简单。主要通过插入延时单元(delay cell)来显著增加时序路径整体延时来达到满足保持时间要求的目的

参考:

https://blog.csdn.net/qq_39507748/article/details/122071160

集成电路静态时序分析与建模——刘峰

1002

1002

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?