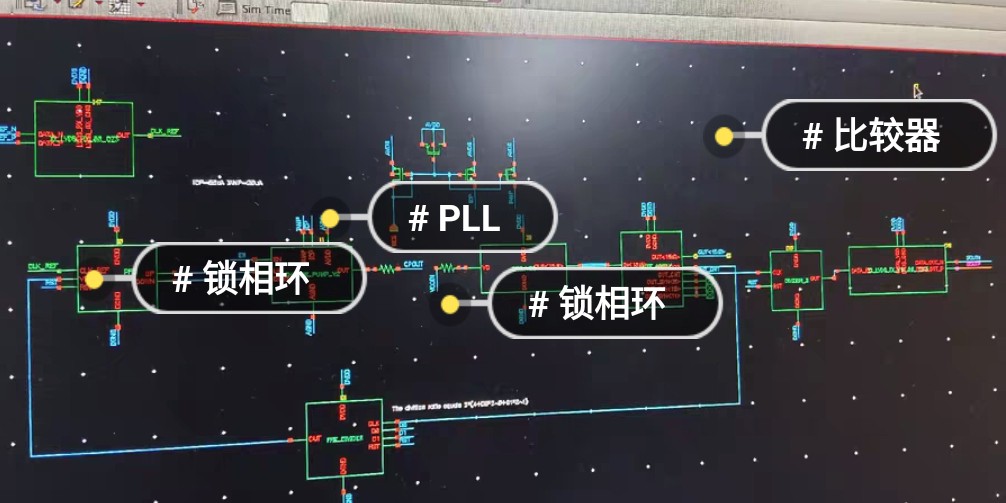

锁相环CPPLL,有版图,已流片片完整,有仿真文件,输入参考时钟100M,可编程分频器,可倍频,相差1ps左右,图展示的输出时钟频率为1G,有各个指标testbench,已流片完整,可靠性保障,版图完整,有芯片型号已经投产,送相关资料文献和相位噪声模型代码框架和测试方法,从入门到实践,均为自己学习和实验时候用到的,分阶段清晰完整。

该锁相环非线性较好,可用于TDC时钟内插技术。

ID:18399729418844231

ic小博已读不回拉黑

锁相环(Phase-Locked Loop,简称PLL)是一种在电子系统中广泛应用的时钟同步技术。它可以将输出时钟与输入参考时钟保持相位恒定,从而实现时钟的稳定和精确控制。在现代高速通信和数据处理领域中,PLL的应用越来越广泛,尤其在时钟内插技术中发挥着重要作用。

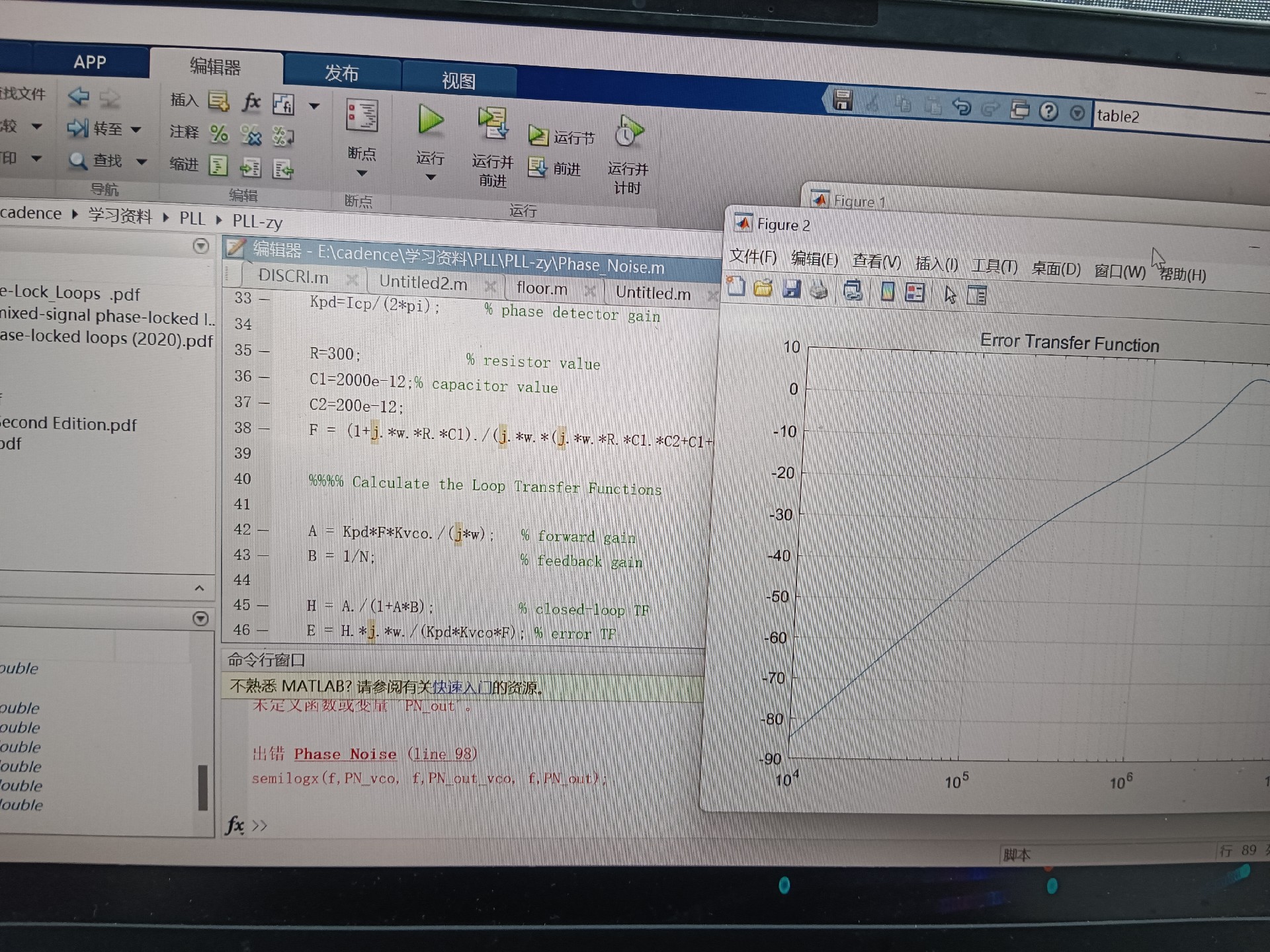

在本文中,我们将介绍一种具有优良非线性特性的锁相环CPPLL。该CPPLL已经完成了版图设计,并且已经流片完整,具备了可靠性保障。同时,我们还提供了相应的仿真文件和各项指标的测试样本,以及相关的资料文献和相位噪声模型代码框架和测试方法,帮助读者从入门到实践。

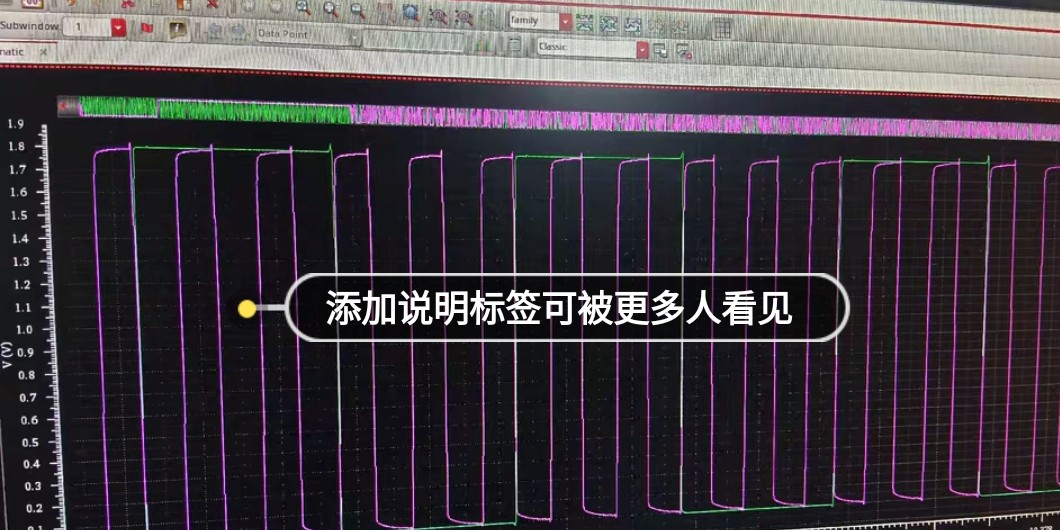

首先,让我们来了解一下CPPLL的基本原理。该锁相环采用了可编程分频器和倍频器,可以将输入参考时钟进行分频和倍频,以实现对输出时钟频率的精确控制。通过精心设计的反馈回路,CPPLL能够保持输出时钟与输入参考时钟的相位差在1ps左右,实现高精度的时钟同步。

另外,CPPLL的非线性特性在TDC时钟内插技术中具有重要意义。TDC时钟内插技术是一种将输入时钟信号分割成更高精度的时钟信号的方法,常用于时钟精密测量和数据同步等应用场景。CPPLL的优良非线性特性使其成为TDC时钟内插技术中的理想选择。通过锁相环的稳定输出时钟信号,可以有效地提高TDC的测量精度和数据同步性能。

图展示的输出时钟频率为1G,这个频率是根据具体应用场景的需求进行选择的。CPPLL的可编程特性使得输出时钟频率可以根据实际需求进行调整,具备了较高的灵活性。

最后,我们需要强调的是CPPLL的可靠性保障。已经完成的版图设计和流片过程确保了锁相环的稳定性和可靠性。经过严格的测试和验证,CPPLL已经具备了工业投产的条件,可以放心使用。

综上所述,锁相环CPPLL是一种具有优良非线性特性的时钟同步技术。它通过可编程分频器和倍频器实现对输出时钟频率的精确控制,可用于TDC时钟内插技术。我们提供的相关资料和测试方法将帮助读者深入了解CPPLL的原理和应用,并能够在实践中得到有效应用。无论是对于学习者还是在工程应用中,CPPLL都是一项非常有价值的技术。

【相关代码,程序地址】:http://fansik.cn/729418844231.html

2218

2218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?