1 简介

许多压控晶体振荡器是低带宽锁相环中的关键部件。此类锁相环通常用于电信、视频、音频、网络和仪器应用中的同步和/或抖动清理。本应用说明描述了关键VCXO特定性能参数的关系及其在PLL设计中的权衡。

2 基本PLL架构

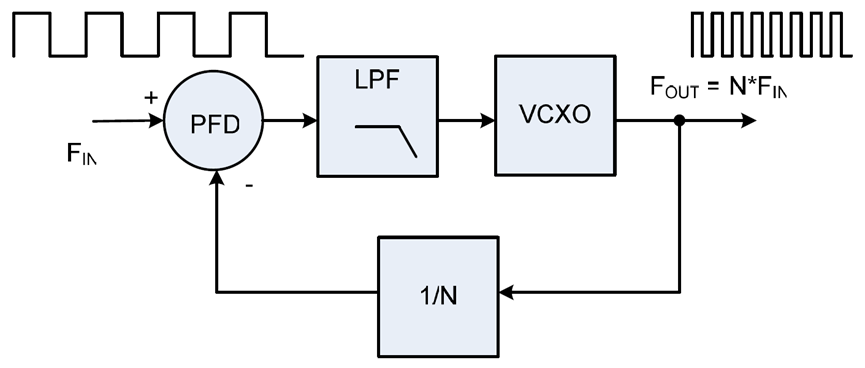

图1:典型PLL框图

图1:典型PLL框图

图1显示了一个简单的PLL框图。参考时钟提供输入频率FIN。相位频率检测器(PFD)比较输入时钟和输出时钟的相位,并基于相位差生成周期误差信号。该周期信号通过环路滤波器(LF)进行低通滤波,并作为模拟控制电压传递给VCXO输入。

VCXO输出频率由控制输入电压控制,并大致与控制输入电压成比例。输出频率将随控制电压的变化而变化,直到产生的相位误差能量被驱动为零。在上述常见情况下,VCXO产生的输出频率和反馈给PFD的频率之间存在一个除以N的值。这将导致参考频率的有效乘以N。

2.1 PLL作为频率跟踪器/滤波器

只要变化的速度在PLL环路滤波器的总带宽内,PLL输出跟踪参考频率的变化。它还平滑或过滤输入参考频率中的高频变化或抖动。这是一个使用锁相环作为“抖动清洁器”的示例,即跟踪参考时钟中的低频变化,例如在网络同步应用中,同时过滤掉高频抖动。只要变化的速度在PLL环路滤波器的总带宽内,PLL输出跟踪参考频率的变化。它还平滑或过滤输入参考频率中的高频变化或抖动。这是一个使用锁相环作为“抖动清洁器”的示例,即跟踪参考时钟中的低频变化,例如在网络同步应用中,同时过滤掉高频抖动。

这里的权衡是,VCXO本身中的低频偏移相位噪声也被衰减,高频偏移VCXO相位噪声被传递到输出。因此,用作参考输入噪声低通滤波器的同一环路用作VCXO噪声的高通滤波器。在这种设计中,在为几个相互冲突的目标选择环路带宽时存在权衡:

- 衰减参考输入噪声(带宽越低越好)

- 跟踪高达所需带宽的参考变化(更高的跟踪速度要求意味着更高的带宽)

- 衰减VCXO产生的噪声(带宽越高越好)

前两个目标相当于低通滤波器中的常见权衡:跟踪性能与噪声滤波性能。一般来说,使用低噪声压控晶体振荡器可以简化这两个参数的权衡,因为衰减压控晶体振荡器产生的噪声不太重要。

PLL系统中的VCXO通常可以建模为简单的增益Kv。与任何反馈系统一样,闭环动态将是该增益的函数,并且可能由于Kv选择不当而变得不稳定。因此,Kv是回路设计中更关键的选择之一。Kv的合适范围通常由应用要求决定,并且受到限制,通过VCXO零件的可用性,可以满足这些要求。

3 压控振荡器参数对锁相环性能的影响

在锁相环设计中,需要最小Kv和最大APR。然而,使用石英基压控晶体很难同时获得两者。本节描述了APR和Kv之间的权衡,并解释了SiTime VCXO如何使设计者免于进行此类权衡。

3.1 绝对牵引范围

由于锁相环设计人员通常关心在所有条件下跟踪指定的输入频率范围,绝对牵引范围(APR)是锁相环设计的更相关规范。

图1显示了典型石英压控晶体振荡器和SiTime压控晶体振荡器的频率-电压(FV)特性。灰色带说明了FV特性随条件变化的程度,并证明了标称或总拉力范围与APR之间的差异。APR必须大于最大预期参考频率变化。否则,锁相环可能无法跟踪参考输入频率。

对于石英压控晶体,为了获得更高的APR,通常需要使用较低Q值的晶体,以使晶体更“可拉伸”然而,这也会降低频率稳定性。因此,必须在应用程序所需的最小APR和该APR可用的最小频率稳定性之间进行权衡。通常,最好选择满足应用程序要求的最低APR。

3.1.1 SiTime VCXO对绝对牵引范围的好处

由于更高牵引范围的压控晶体振荡器通常意味着更大(更差)的频率稳定性,因此选择标称牵引范围明显大于其他要求的压控晶体振荡器并不罕见,只是为了提供足够高的APR以满足最低应用要求。这通常会带来设计上的损失,因为要求VCXO具有更陡的FV特性,这可能会对PLL设计中的噪声和稳定裕度产生不利影响。

SiTime的VCXO系列不受此影响。由于响应于控制电压变化的频率变化是通过VCXO设备内的PLL产生的,因此SiTime使频率稳定性独立于牵引范围本身。这允许设计者准确地选择应用程序所需的APR,而不是更多。

图2:典型VCXO-FV特性:

(a) 典型石英VCXO特性 (b)典型SiTime VCXO特性

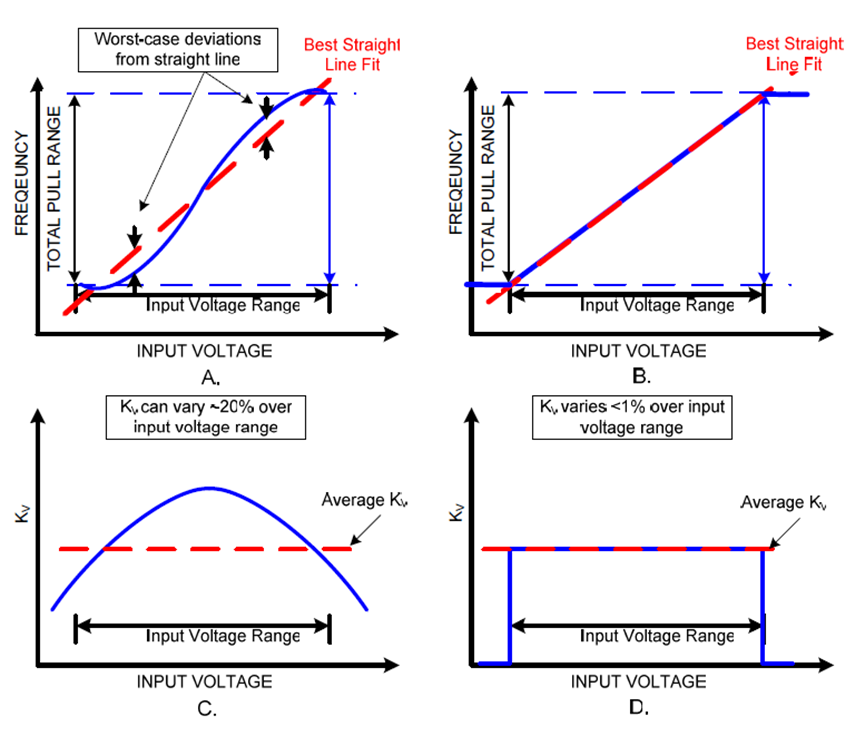

3.2 Kv线性

标准石英压控晶体振荡器的Kv可能在输入控制电压范围内发生显著变化,通常在10%到20%之间。通常,具有更好线性规范的零件的Kv变化较低,但即使在具有良好线性规范的零件中,也可能存在显著的Kv变化。

一些数据表可能会指定“平均”Kv,但由于Kv会影响重要的PLL性能参数,如带宽和相位裕度(稳定性),因此在成功的设计中必须理解并考虑整个Kv变化。

3.3 Kv对锁相环设计的影响

对于大多数低带宽PLL,VCXO的FV特性建模为简单增益Kv。与任何控制系统一样,调整增益将改变闭环动态。在绝大多数情况下,增加Kv将提高环路速度(更好的跟踪),但也会增加超调量和峰值,并可能使闭环系统更接近不稳定。更高的Kv也会使系统对控制输入处的电压噪声更敏感,从而增加整体系统抖动。

典型的石英基压控晶体通过变容二极管实现其电压控制功能,从而产生弯曲的FV特性,如图3(a)所示。这些器件的线性规格通常在5%到10%的范围内。该弯曲特性可导致Kv特性在输入电压控制范围内发生显著变化,如图3(c)所示。为了成功使用这种压控晶体振荡器,锁相环设计者必须考虑限制锁相环带宽和跟踪能力的最小千伏,以及决定最坏情况下抖动和噪声性能的最大千伏,以及最坏情况下的系统稳定性。

更为复杂的是,线性和Kv曲线本身可能会随着温度和Vdd等条件的变化而变化,迫使设计师考虑这些条件对Kv的最坏影响。这些依赖关系可能在给定的数据表上没有很好的记录,但可能只在保守的“最小”和“最大”Kv规范中记录。

最后,设计者可以在最小APR的基础上最初选择VCXO系列。由于VCXO的频率稳定性随着APR的升高而变差,因此需要更高的Kv以在相同的电压控制范围内实现相同的APR。这意味着可能需要选择远高于系统性能和回路稳定性所需的Kv,只需满足APR规范!

3.3.1 SiTime VCXO对Kv变化的好处

为了进行比较,图3(b)和图3(d)显示了SiTime的380X系列压控晶体振荡器的线性度和千伏变化。FV特性极为线性,通常远小于1%,在整个控制范围内,Kv将保持极为恒定。

此外,在SiTime设计中,频率稳定性和Kv被指定为完全独立的量。这意味着设计者可以自由地独立选择适合其应用的频率稳定性、APR和Kv。此外,由于Kv在整个控制电压范围内保持恒定,因此几乎不需要考虑条件下较大Kv变化的最坏情况分析。所有这些优点一起大大减轻了锁相环设计者的负担。

图3:VCXO线性和Kv特性:

(a)典型石英VCXO FV特性 (b)典型SiTime VCXO FV特性

(c)典型石英VCXO Kv变化 (d)典型SiTime VCXO Kv变化

4 结论

本文阐述了一些最重要的压控晶体振荡器性能规范及其在最重要的压控晶体振荡器应用之一PLL设计中的应用。它还说明了传统石英压控晶体振荡器和SiTime压控晶体振荡器在这些规范中的一些重要差异,以及SiTime压控晶体振荡器可以为PLL设计人员提供的好处,减少了权衡APR、Kv和频率稳定性等关键参数的需要。

1411

1411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?