一 实验过程

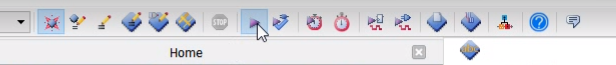

第一步:打开Quartus II新建一个工程文件路径如图(新建一个与项目名称相同的文件)

第二步:点击file 新建,对话框中选择 Verilog HDL File

第三步:输入代码

module fulladd(sum,c_cut,a,b,c_in);

output sum,c_cut;

input a,b,c_in;

wire s1,c1,c2;

xor (s1,a,b);

and (c1,a,b);

xor (sum,s1,c_in);

and (c2,s1,c_in);

or (c_out,c2,c1);

endmodule

module test;

wire sum,c_out;

reg a,b,c_in;

fulladd fadd(sum,c_out,a,b,c_in);

initial

begin

a=0;b=0;c_in=0;

#10 a=0;b=0;c_in=1;

#10 a=0;b=1;c_in=1;

#10 a=0;b=1;c_in=1;

#10 a=1;b=0;c_in=0;

#10 a=1;b=0;c_in=1;

#10 a=1;b=1;c_in=0;

#10 a=1;b=1;c_in=1;

#10 $stop;

end

endmodule

运行并保存

第四步:

点settings,再点击Compile text bench

第五步:跳转到Modelsim显示出波形图,改一下数据

得到波形图

二 过程链接

https://v.qq.com/x/page/a3247i0mnmo.html

3088

3088

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?