关注+星标公众号,及时获取更多技术分享~

作者 | 冰茶奥利奥

微信公众号 | 嵌入式电子创客街

原理图绘制好后,如果需要做DRC检查或者需要写FPGA程序,批量做引脚约束,倒是可以手动输入,但是大项目动辄几百个引脚,一个个手输就得残废。

需要完成两个步骤,一是把原理图里的网络信息导出来,二是将网络信息导入到vivado。

步骤一:

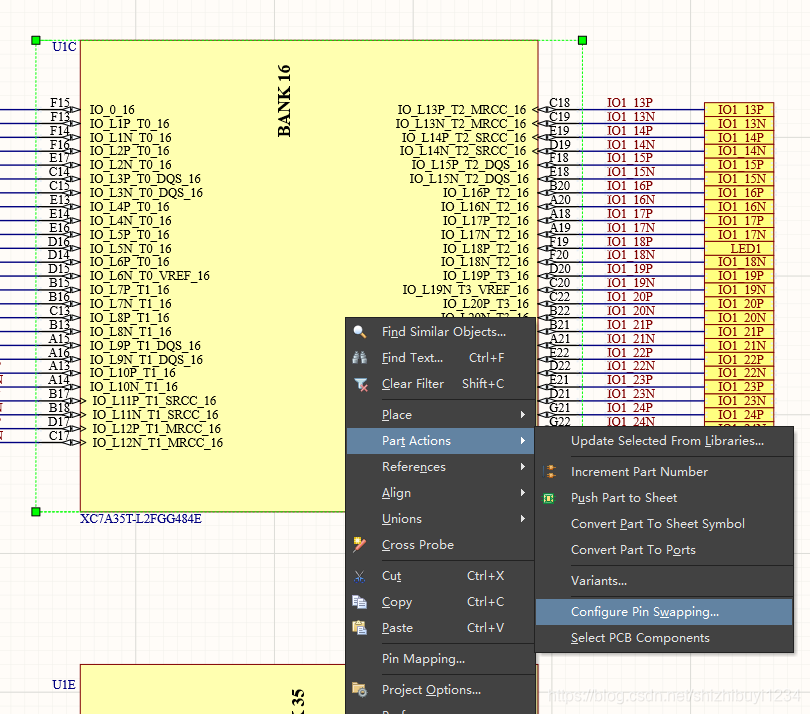

在原理图上选中任一part后右键,选择Part Actions-->Configure Pin Swapping。(这个步骤要求原理图必须是在一个PCB工程下,如果你是一个单独的sch文件,那么就建一个工程把文件拖进去)

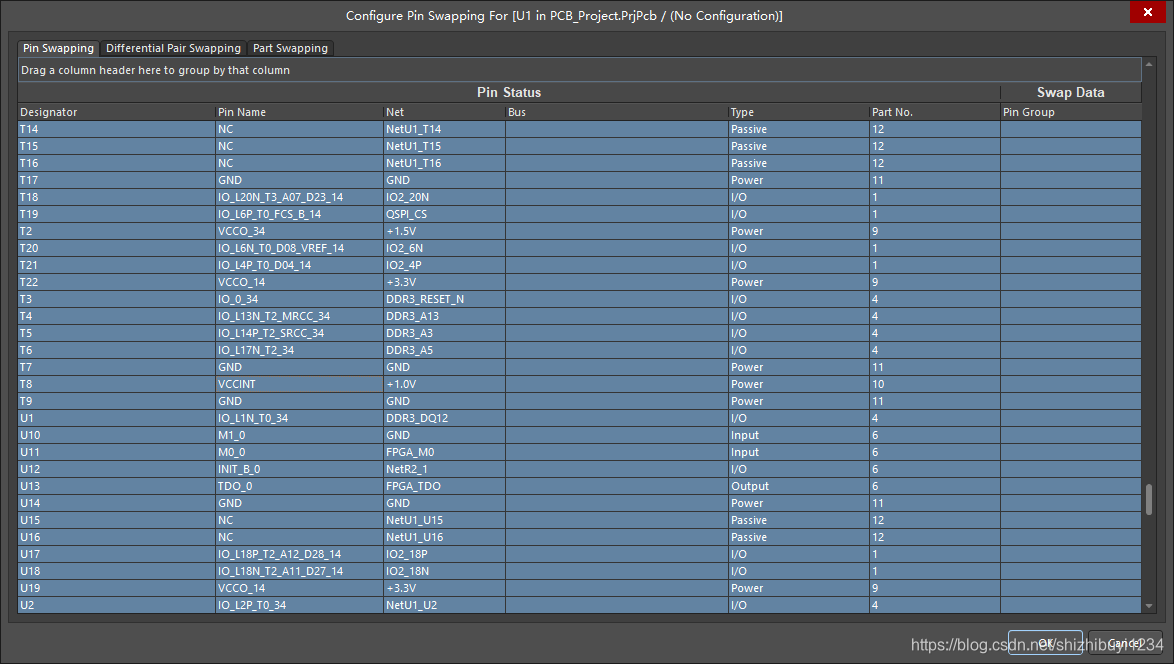

在弹出的窗口里Ctrl + A 全选中然后 Ctrl + C ,新建一个excel文件粘贴进去。

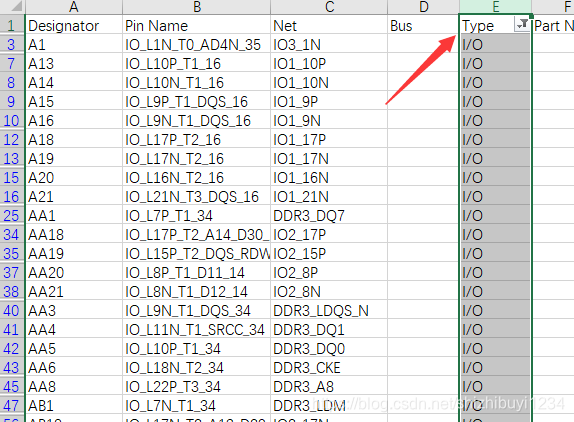

我们把信号类型筛选一下,只选择IO。

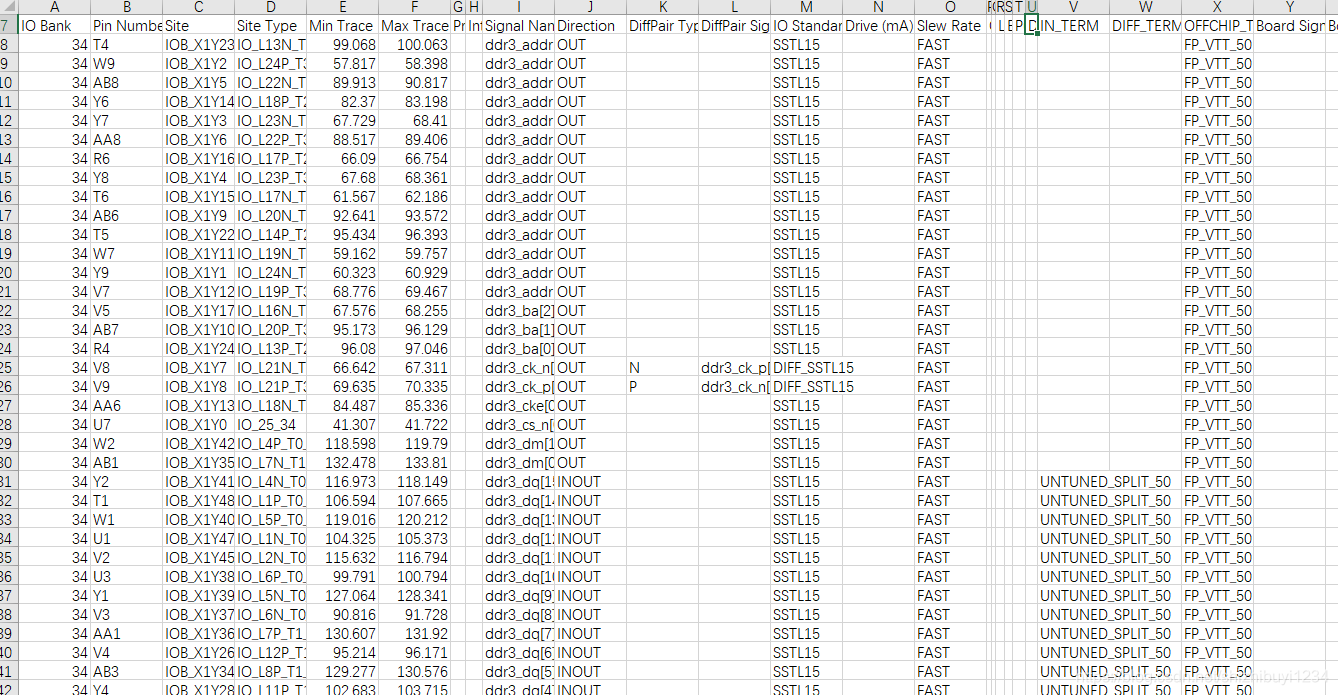

打开xilinx 的引脚约束csv文件模板(模板文件获取可以从旧工程导出获取到,这里不再赘述),如图为引脚分配csv文件示例。

然后我们把AD 导出的excel文件 对应的填到引脚约束文件模板里。可以只填signal Name 和Pin Name。

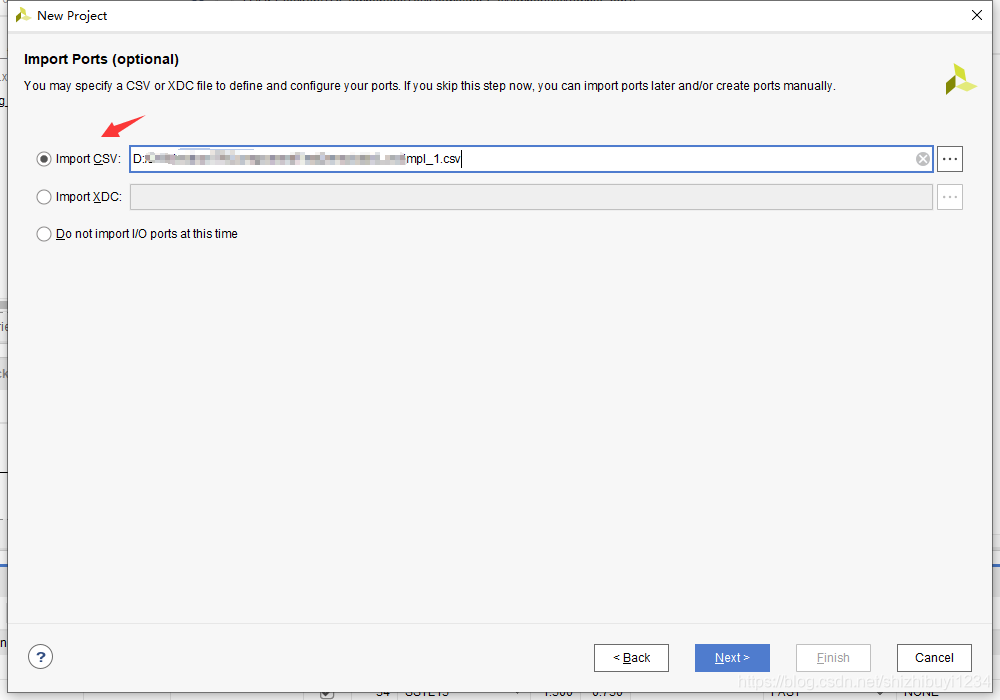

填好后打开vivado导入,即可自动生成约束信息。

如果您觉得这篇文章帮到了你,请点赞或者留下您的评论,您的鼓励是我前进的动力~

关注博主公众号 “嵌入式电子创客街” 获取更多及时技术分享~

5785

5785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?