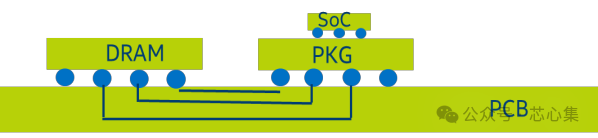

在LPDDR4之后,引入了 LPDDR4x,其IO电压比LPDDR4低45%,从1.1V至0.6V。整体功耗的降低带来了满足信号和电源完整性要求的多重挑战。LPDDR4x DRAM的传统SI问题主要包括串扰噪声、反射噪声和损耗效应。串扰噪声主要来源于紧密间隔的互连信号之间的相互耦合而产生的NEXT和FEXT。弯曲、过孔过渡、封装结构和电源接地分裂平面等不连续性可能导致最差的插入损耗。在较高的数据速率下,传输线的频率相关损耗对信号质量和时序也有显著影响,从而导致眼图的恶化。图1是本文中评估LPDDR4x系统,颗粒采用外接分立器件然后通过PCB、PKG、SOC连接成一个完整的系统。

图1 LPDDR4x内存下降配置

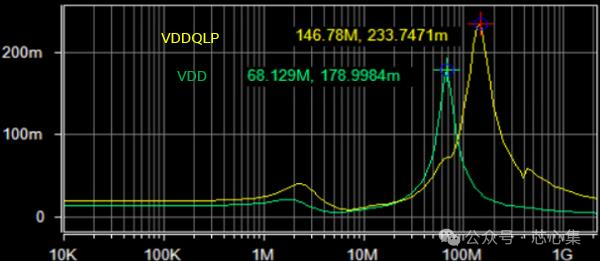

电源PI仿真评估

主要LPDDR4x PHY 主要有两个电源供电, IO 电源 VDDQLP(0.6V)和数字Core电源VDD(0.8V)。对信号抖动贡献最大的电源是Core电源VDD。VDD和VDDQLP的纹波规格公差分别为±2%和±5%,要求很严格。从电源完整性的角度来看,控制VDD和VDDQLP电源PDN的环路电感是非常重要的。从球栅阵列(BGA)焊盘到芯片bump的环路电感可以通过将相应轨道的凸块正好放置在BGA焊盘上方并提供到相应平面的连接而最小化。每个电源bump应具有附近的VSS bump,V SS bump具有稳定的连接,这提供了最低的返回电流路径,从而使环路电感最小化。从DSC(芯片侧电容器)到bump的环路电感也应最小。DSC的放置方式应使得来自每个bump的环路电感梯度最小。从bump到封装衬底上半部分的DSC焊盘的平面布线将降低环路电感值。VDD\VDDQLP bump在整个PHY区域的分布对于将电流负载均匀分布在每个bump上非常重要,这有助于降低单个bump上的峰值噪声。通过上述物理设计,所有VDDQLP和VDD bump的环路电感分别可以在250pH和350pH范围内实现。为了实现4267Mbps的速度,将电压纹波限制在规范内是非常重要的。对于给出PDN网络阻抗分布的AC仿真,使用组合封装和板s参数模型进行仿真。一般在调整PDN阻抗的是会将其分成三个大的频率范围:一个是较高频率,大于10MHz,为了控制这个较高频率下的阻抗,可使用VDDQLP为10nF,VDD为20nF,也可以增加一些DSC,DSC可以选取的范围可以从100nF、 220nF到1uF,用于获得具有较低谐振频率的优化阻抗分布,这将直接影响电源的峰峰噪声;第二个范围是1M~10MHz之间,主要为对PCB板上的去耦电容器进行优化;第三个是从10KHz到1MHz的阻抗则必须通过VRM输出电容器的最佳数量来控制。基于这三个频率范围,LPDDR4X的VDDQLP和VDD电源的PDN网络阻抗曲线,如下图2所示。

图2 VDDQLP和VDD导轨的PDN阻抗分布

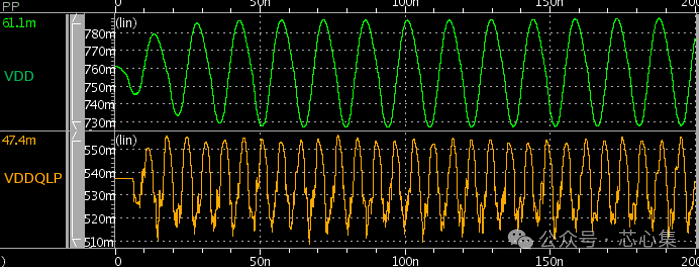

而下图则是基于上述PDN进行的VDDQLP和VDD电源的噪声仿真。图3显示了 VDD和VDDQLP的瞬态噪声结果。

图3 VDDQLP和VDD导轨的瞬态噪声分布

可以看到噪声值VDDQLP的在0.6V的±5%和0.8V的VDD±2%的SPEC范围内。

PI-SI 联合仿真

PCB/PKG信号布局优化

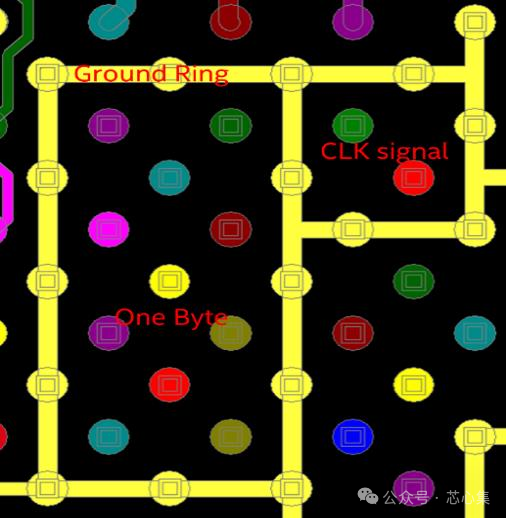

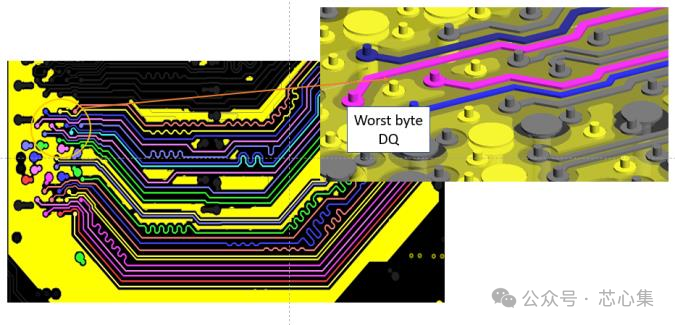

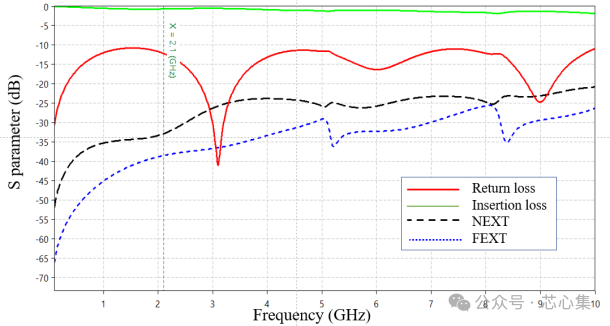

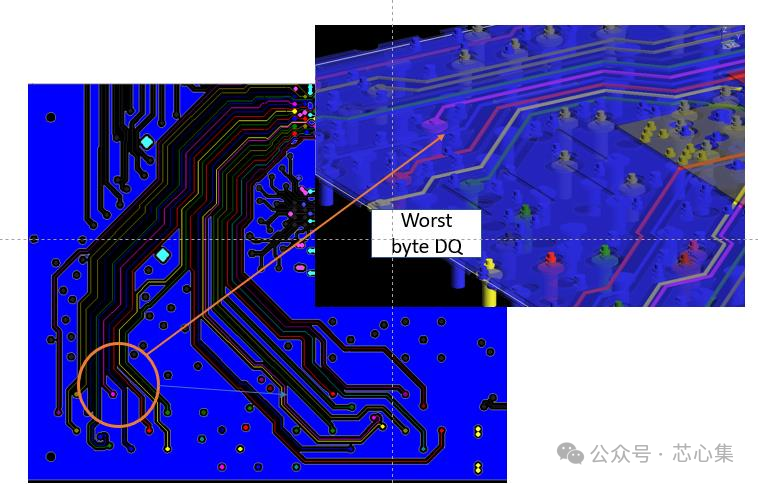

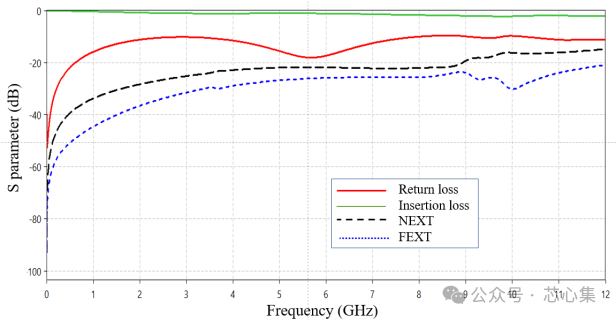

为了限制封装和电路板的插入损耗,布线长度一直保持在尽可能低的水平。为了实现这一点,bump和ball使用via on pad的方式放置,这样就不会出现交叉。之所以使用焊盘上过孔,是因为所有数据字节都已作为带状线布线,以减少板和封装中的串扰。由于与封装相比,板路由长度更高,因此需要特别注意优化PCB。为了优化返回路径,信号bump和VSS bump的比例可保持在2:1,ball的比例为1:1。将接地球环放置在PCB上有助于改善返回路径,从而改善串扰,如图4所示。将 DQS放一个byte组的中心有助于减少DQ到DQ的串扰。信号过孔附近的接地过孔也改善了返回路径,整个设计过程都遵循了这一准则。图5和图6分别表示板布局和封装布局对应最差的仿真结果。

图4 VSS ball包围着一个byte信号

图5(a)隔离度比较少的PCB设计

图5(b)回波损耗、插入损耗、NEXT和FEXT的S参数

最终通道性能分析

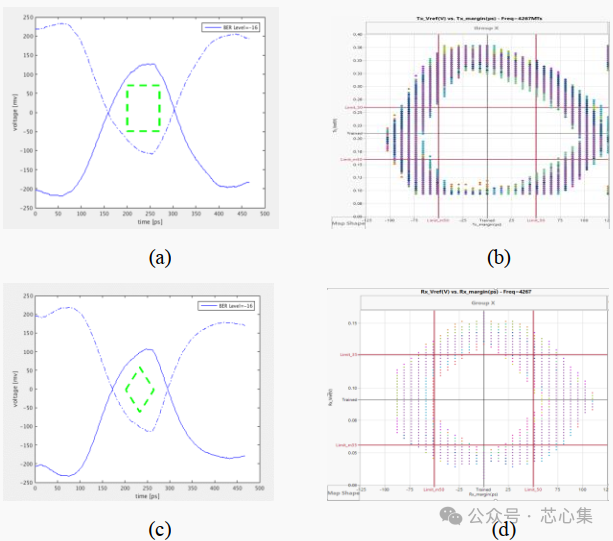

在优化完信号信道布局出线后,接下来就对整个系统进行时域分析。选取设计最差的一个byte进行分析讨论。同时SI仿真带入了电源的PDN网络影响,可以看到PSIJ的影响,也对不同PVT条件下的眼图性能进行了分析。

图6(a)具有分裂的接地平面和电源平面的封装设计示意

图6(b) 最差数据的RL、IL、NEXT和FEXT的S参数

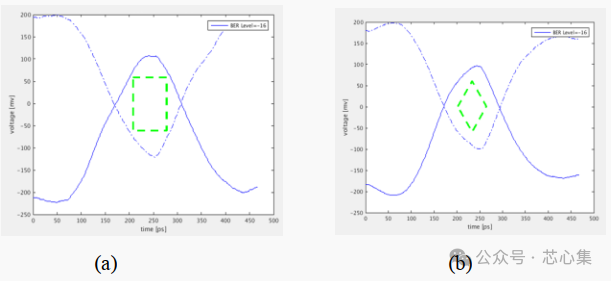

图7 SS corner下的写入(a)和读取(b)眼图

图8 TT corner下的写方向(a\b)和读方向(c/d)的仿真和测试的数字眼图

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?