前面有很多文章都介绍了PI性能的影响,也介绍了PSIJ对信号或时钟性能的影响,对于SOC设计,为了更好的理解电源完整性在芯片设计中的重要作用,对芯片的时钟树设计需要足够理解才能更好的明白电源完整性的影响。

时钟分布网络设计一直是高性能芯片物理实现过程中的重要环节,随着芯片制造工艺与设计技术的飞速发展,芯片设计所要求的性能和频率也大幅增长,时序收敛以及低功耗需求就使得时钟树综合面临更为严格的挑战。因此,一个满足时序要求的低功耗时钟树综合成为集成电路物理设计中的重点。

时钟信号

同步时序电路是当下集成电路设计的主流,大部分数字集成电路设计都普遍采用同步电路,同步电路中的数据传输由一个或多个时钟脉冲信号统一进行控制。时钟信号通过距离最长、有最大扇出并以最高速度运行。时钟信号控制着各功能元件的数据传输,作为数据传输的基准,它对于同步数字设计的性能、功能和稳定性等方面起决定性作用。

1、时钟信号的产生

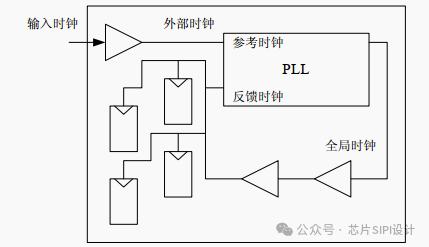

时钟的生成有多种方法,在VLSI设计中,外部晶振输入是最常用的方法。对于高频时钟,则采用专用的锁相环 PLL 电路通过调整倍频参数进行倍频。时钟也可通过电路生成,例如含有奇数个反相器的振荡环电路,在每个节点都产生振荡信号,其周期由反相器的级数以及每级的延迟所决定,不过,这种电路产生的时钟稳定性较差,不适用于性能要求较高的设计,下图为一个是使用 PLL 生成全局时钟的示意图。

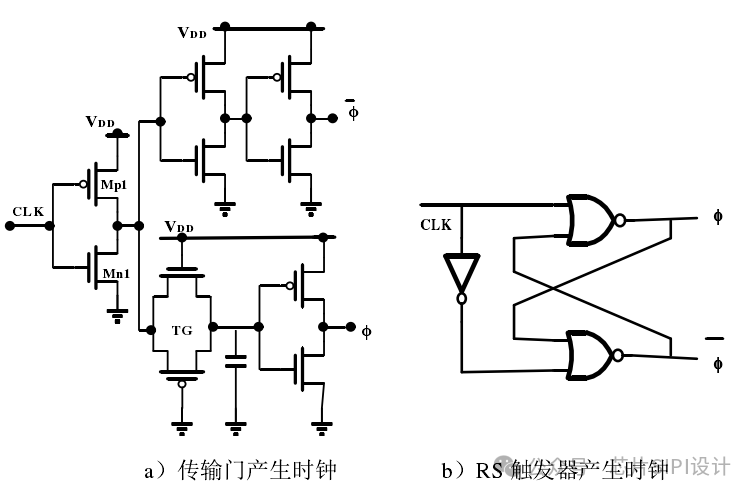

当芯片采用外部输入时钟信号作为信号时,为了实现内部时钟的要求,就可以用传输门将外部输入的时钟转变成设计需要的主时钟和辅时钟。下图为常用的产生两个相位相反时钟的电路。传输门产生时钟电路中,外部时钟通过 Mp1、Mp2 后,一路通过传输门和一个反相器生成时钟,一路连续通过两个反相器生成一个与其相位相反的时钟。该种电路通过多级传输,提高了驱动能力的同时也减小了两个反相时钟间的时钟偏差。还有一种简单的电路为 RS 触发器产生时钟电路,它被更多的用于产生系统所需要的分频时钟。

在数字电路的设计中,时钟是最重要的组成部分,数据必须通过时钟信号才能准确的传输,尤其对于同步数字系统的功能、稳定性等起决定性作用。

芯片设计中主要时钟

在集成电路的设计中一般来说主要有以下几种时钟:

1)系统时钟:系统时钟是指控制多个芯片之间的时钟结构网络并控制相互之间时序关系的时钟结构,常用的有 RC 时钟,晶体振荡时钟、锁相环倍频时钟等。每个芯片的时钟信号都是通过 I/O 单元与系统时钟相连的。一般来说,系统时钟也被叫做“全局时钟(global clock)”,在某些情况下也叫做主时钟(master clock)。

2)自定义时钟(generate clock):自定义时钟是从主时钟导出的时钟,主时钟是使用指令 create_clock 规范定义的时钟。当在基于主时钟的设计中生成新时钟时,新时钟可以被定义为生成时钟。例如,如果存在用于时钟的 3 分频电路,则可以在该电路的输出端定义生成的时钟定义。由于静态时序分析不知道时钟周期在分频逻辑的输出端发生了变化,并且更重要的是新时钟周期的变化,所以需要此定义。自定义时钟在做时钟树综合时,同样将自定义时钟作为对时钟点进行时钟树的生成,并对时钟树进行优化。

3)虚拟时钟:虚拟时钟是存在但不与设计的任何引脚或端口相关联的时钟,可以认为是逻辑意义上的时钟,是由人为定义出来的时钟信号。它在静态时序分析中用作参考,用于指定相对于时钟的输入和输出延迟。

相对于子芯片而言,各个子芯片中的时钟,都是由一个个是主时钟延伸出来的,很多时候这些子芯片中的主时钟,在整个芯片的层面上来看,很可能只是其他子芯片中的自定义时钟,然后通过 port 传输到这个子芯片中,作为主时钟使用的。

时钟信号性能参数

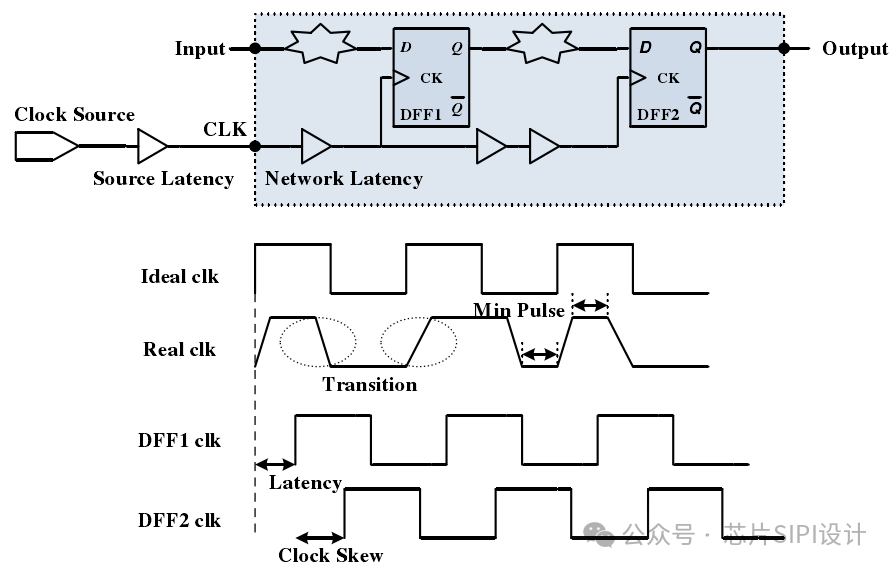

在 RTL 设计阶段一般认为时钟是理想的,但当具体到物理设计时,时钟是通过物理方式实现的,因受多重因素的影响,时钟只能是接近但无法达到理想状态。评估时钟信号性能的参数有很多,主要包括时钟不确定性、时钟转换时间、时钟传播时间、时钟最小脉冲宽度、时钟偏差等。下图给出了时钟信号性能参数示意图。

1、时钟不确定性

时钟不确定性(Clock Uncertainty)也称时钟信号抖动(Jitter),为信号时间与理想时间的偏差。如上图所示,因存在时钟抖动,真实时钟的时钟沿要比理想时钟或早或晚到达。时钟信号抖动是由时钟源本身引起的,它取决于时钟发生器内部结构,在基于标准单元的物理设计中,一般时钟产生电路会作为 IP 集成在 SOC 中,因此时钟抖动作为时钟信号的重要属性是时钟树综合阶段必须的信息之一。一般在时钟树综合之前会将时钟不确定性设置的比时钟信号抖动参数大一些,以此来给时钟综合的偏差值留下余量。

2、时钟转换时间

时钟转换时间(Clock Transition)即不同电平间转换所需要的时间。理想情况下时钟电平转换是瞬间完成的,但实际受工艺、供电电压、互连线负载和扇出负载等因素影响,电平转换是需要时间的。一般时钟转换时间为时钟信号高电压从电源电压的10%变化到90%的时间间隔。转换时间分为上升时间和下降时间,一般应使上升转换时间和下降转换时间保持对称性,通常会选用具有高对称性的缓冲单元来做时钟树。时钟转换时间的长短也是影响时钟树质量的重要指标,时钟转换时间过大会导致缓冲单元延时增大进而引起时序违例,同时也因延长了 NMOS 和 PMOS 管同时导通时间而造成晶体管短路功耗迅速增大;而时钟转换时间过小,则可能会因使用了过大驱动能力的缓冲器造成浪费不必要的功耗和面积。因此,在时钟树综合阶段需要设置合适的转换时间。

3、时钟传播时间

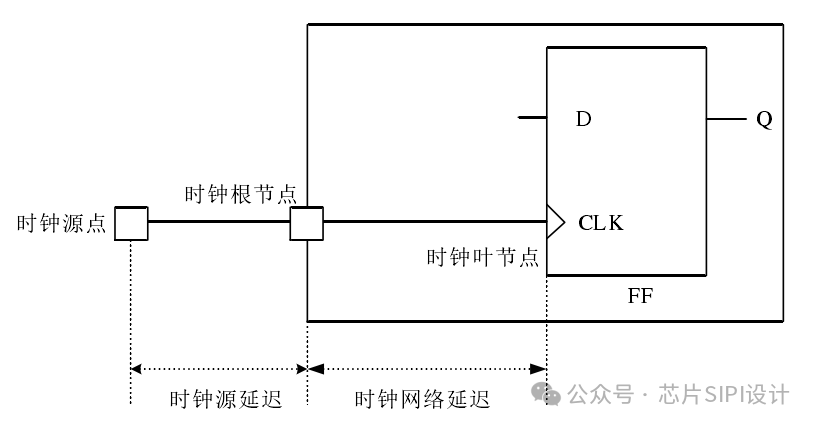

时钟传播时间(Clock Latency)为时钟信号从时钟源传输到时钟树叶节点的时序单元所需要的时间。时钟传播时间分为源时钟输入时间(Source Insertion Delay)和网络时钟输入时间(Network Insertion Delay)。源时钟输入时间指时钟信号从时钟源到设计时钟输入端口的时间,时钟源一般指的是锁相环(PLL)的输出端,但也可根据设计需求利用约束文件定义到 PLL 外的任何节点。网络时钟输入时间指时钟输入端口到时钟树叶节点时序单元 CK 端的时间。时钟传播时间也是衡量时钟树质量的一个重要指标,时钟传播时间越短,时钟树性能就越好,同时,外在因素对时钟树的影响也会越小。

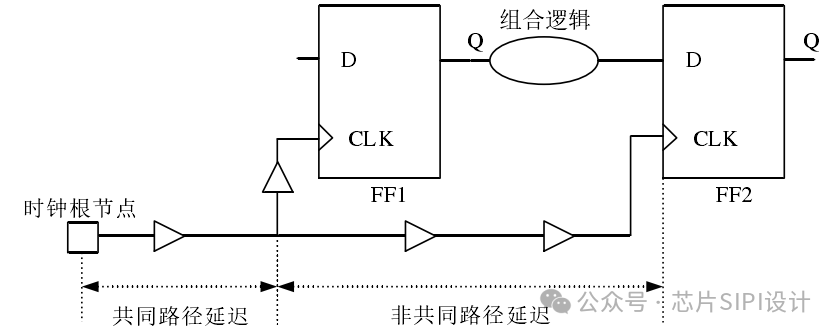

时钟网络延迟可分为共同路径(common path)延迟和非共同路径(non-common path)延迟,如下图所示,优化触发器 FF1 与 FF2 的共同路径延时不会引发时序违例,但影响时钟网络的功耗及所消耗的设计资源。优化触发器 FF1 与 FF2的非共同路径延时,对触发器 FF1 和 FF2 的建立时间及保持时间时序、片上偏差和时钟偏差均会有影响。时钟延迟是评价时钟树的重要指标,是满足时序收敛的关键因素,在时序优化过程中,尽量减少共同路径延迟,以降低功耗和节约设计资源;尽量优化非共同路径,以满足时序收敛要求。通常设计者所言的时钟延迟为时钟网络延迟。

4、最小脉冲宽度

最小脉冲宽度(Min Pulse Width)指脉冲波形的开始到结束之间的最小时间间隔。若时序器件时钟端口处的时钟脉冲宽度过窄,则有可能造成时序器件无法正确传递数据,甚至使时钟不会再继续传递。因此,集成电路物理设计过程中会对时钟脉冲的宽度做约束,通常最小脉冲宽度约设为时钟周期的40%。

5、时钟偏差

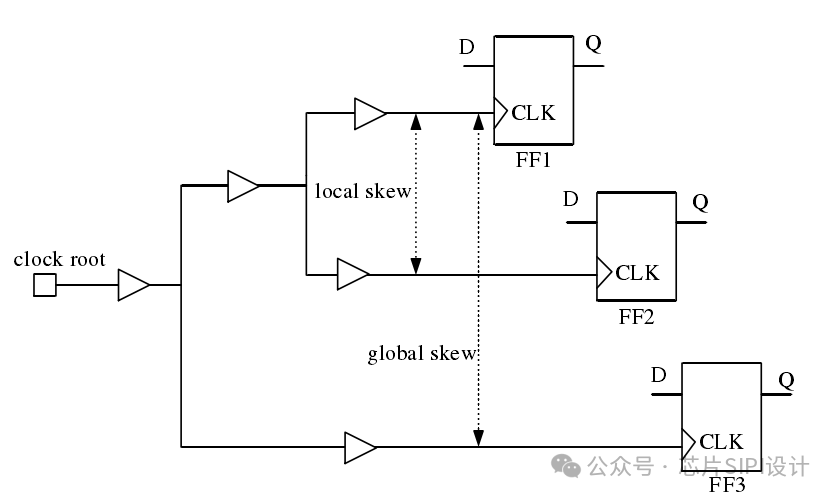

时钟偏差(Clock Skew)指时钟信号从时钟源到时钟树叶节点时序单元的时钟端口的延时差。理想状态下,时钟到达各个寄存器 CK 端的时间是一致的,但实际因时序单元尺寸或物理位置的不同导致时钟线长短、负载不同,从而使得时钟信号到达时序单元的时钟端口存在偏差。时钟偏差可以分为全局偏差和局部偏差,全局偏差(Global Skew)指时钟信号到设计中所有时序单元的时钟端口的最长路径时间与最短路径时间之差,局部偏差是指存在数据通信的任意两个时序单元间的延时差。通常在物理设计阶段主要将局部偏差作为衡量时钟树质量的指标。时钟偏差的存在会导致时钟树不平衡,严重影响到整个设计的时序收敛,因此,减小时钟偏差对提高芯片性能和稳定性有非常重要的作用。

如上图所示,全局时钟偏差即为最大时钟网络延迟和最小时钟网络延迟的差值,即触发器 FF3 与触发器 FF1 之间的时钟网络延迟之差。局部时钟偏差是指拥有数据交互的各时钟叶节点之间的时钟偏差,即触发器 FF2 与触发器 FF1 之间的时钟网络延迟之差。时钟偏差是衡量时钟树质量的重要指标,时钟偏差的产生原因主要为以下两点:

a.时钟负载不平衡,主要由时钟根节点到时钟叶节点的金属互连线长度不同,所插入的缓冲器驱动强度和级数不同而引起;

b.片上工艺偏差引起,温度变化、电压波动和工艺制造过程中的不确定性都会引起时钟偏差。

6、片上偏差

数字集成电路的性能受到工艺(process)、温度(temperature)、电压(voltage)的影响,工艺、温度和电压简称 PVT 条件,PVT 条件相对理想值的变动就称为偏差(variation)。根据偏差的来源,可以将偏差分为工艺偏差(process variation),电压偏差(voltage variation)和温度偏差(temperature variation)。工艺偏差是指工艺制造过程产生的偏差,在生产制造过程中,因光刻、刻蚀、淀积、离子注入、扩散、退火等工艺,引起的芯片单元物理结构(如器件和金属互连线尺寸、掺杂情况和材料等)的偏差。温度偏差是芯片在工作过程中,因为外界环境温度和散热条件变化,以及芯片内部的局部热点等因素引起的偏差。电压偏差是在芯片工作过程中因外部供电电压变化,和芯片内部供电网络电压降等因素引起的偏差。偏差不可避免且具有随机性,根据偏差的作用范围,可以将偏差分为片间偏差和片上偏差(On

Chip Variation,简称 OCV)。片间偏差指生产制造的不同芯片在同一区域的偏差,对同一芯片所有区域而言,片间偏差的影响是同步的。片上偏差是指同一芯片在不同区域的偏差,即同一芯片在不同区域的 PVT 条件不同。片上偏差和片间偏差都包含工艺、电压和温度三种偏差。其中片上工艺偏差与片间工艺偏差不同,对于因空间距离引起的片上工艺偏差,其偏差具有一定的空间距离相关性,即空间距离越远,片上工艺偏差出现的可能性和偏差值越大;对于因逻辑深度和单元数量引起的片上工艺偏差,其偏差具有随机性,即随着逻辑级数的加深和单元数量的增多,片上工艺偏差可能会相互抵消,但也可能加大。

5005

5005

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?