DDR总线是典型的高速数据并行总线,随着DDR的发展,其数据速率越来越高,工作电压越来越低。数据速率提高和工作电压降低导致DDR总线系统的SIPI问题更加严重,而对SIPI问题的设计裕量却越来越小,最终提高了SIPI仿真的精度要求。

当前的DDR总线仿真模型已经无法满足越来越高的SIPI仿真精度要求,SIPI仿真需要更加精确的、能全面体现SIPI问题的模型才能进行。并且常规激励作为SIPI仿真输入已经无法验证极端工作环境下DDR总线的SIPI性能,仿真使用的激励同样需要改进。

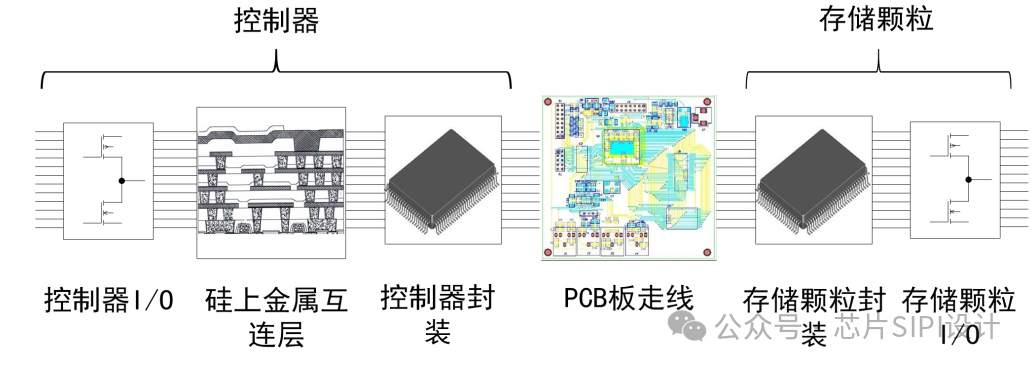

在SIPI仿真中,DDR总线结构在横向上分为DDR的数据DQ线、数据控制DQS线、地址与命令CA线和时钟线等部分。总线纵向由Controller(控制芯片)I/O部分、Controller硅上金属互连层、Controller封装、PCB走线、Memory(存储颗粒)封装、MemoryI/O组成,如下图所示。

一般进行系统仿真环境的搭建包括以下几步:

5155

5155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?