想要正确执行HLS C代码的C synthesis,需要先添加Top function,否则则会报错,添加方法为点击Project→Project Setting

选择top function

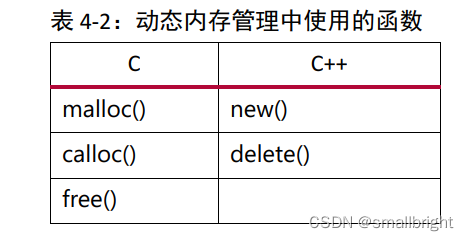

Vivado HLS 可编译几乎任何C/C++程序。Vivado HLS 的唯一编码限制在于含单一内存空间的处理器中常见的动态语言结构。使用Vivado HLS时,需要考量的主要动态结构是内存分配和指针。

代码中不要使用动态分配内存

指针不能说不能用,但是也是需要谨慎使用,这个具体再研究研究。

Vivado HLS对所有程序都进行如下方面的分析

运算、

HLS 数学函数由 hls_math.h 库实现为可综合的位近似函数。位近似 HLS 数学库函数无法提供与标准 C 语言函数相同的精度。为了获得期望的结果, 位近似的实现可能使用与标准 C 语言数学库版本不同的底层算法。该函数的精度以ULP(最小精度单位) 的形式指定。精度上的差异对 C 语言仿真和 C/RTL 协同仿真都有影响。

ULP 差异通常在 1-4 ULP 范围内。

• 如果在 C 语言源代码中使用标准 C 语言数学库, 则由于某些函数与标准 C 语言数学库表现出 ULP 差异, 因此 C 语言仿真与 C/RTL 协同仿真之间可能会有差异。

• 如果在 C 语言源代码中使用 HLS 数学库, 则 C 语言仿真与 C/RTL 协同仿真之间不会有任何差异。但是, 使用 HLS数学库的 C 语言仿真可能与使用标准 C 语言数学库的 C 语言仿真之间存在差异。

如果在 C 语言源代码中使用标准 C 语言数学库, C 语言仿真结果与 C/RTL 协同仿真结果可能产生差异: 如果源代码中

的任一数学函数与标准 C 语言数学库存在 ULP 差异, 则可能导致 RTL 仿真结果不同。

如果在 C 语言源代码中使用 hls_math.h 库, 那么 C 语言仿真与 C/RTL 协同仿真结果可能不同。

使用hls_math.h 时, C 语言仿真结果与使用标准 C 语言库时的结果不同。 hls_math.h 库只确保 C 语言仿真与 C/RTL

协同仿真结果不同。在上述 2 种情况下, 创建的 RTL 实现是相同的。以下解释了使用数学函数时用于执行验证的每一

种可能的选项。

条件语句

在FPGA中,条件语句对性能并不存在与处理器相同的潜在影响。Vivado HLS会创建条件语句的每个分支所描述的所有电路。因此,条件软件语句运行时间执行设计在2个可能的结果之间进行选择而不是上下文切换。

循环

函数

根据Vivado HLS的使用指南, 我们将对我们的输入程序作出以下规范:

1.不使用动态内存分配(不使用malloc(),free(),new和delete())

2.减少使用指针对指针的操作

3.不使用系统调用(例如abort(),exit(),printf()) , 我们可以在其他代码例如测试平台上使用这些指令, 但是综合的时候这些指令会被无视(或直接删掉)

4.减少使用其他标准库里的内容(支持math.h里常用的内容, 但还是有一些不兼容)

5.减少使用C++中的函数指针和虚拟函数

6.不使用递归方程

7.精准的表达我们的交互接口

优化策略

1.展开循环

2.循环流水

3.带宽优化

4.函数内嵌

5.分层

6.数组优化

7.任务流水

8.测试平台

9.一同仿真

10.接口交互

协同仿真

使用协同仿真时请谨记,这是处理器上执行的并行硬件仿真。它比C/C++仿真慢约10000倍。此外,还需谨记协同仿真的目的并不是验证算法的功能正确性。而是检查确认用户给予HLS编译器的指导信息并未破坏算法。

建议:仅在算法功能验证期间使用一小部分测试矢量上运行协同仿真。

一些约束

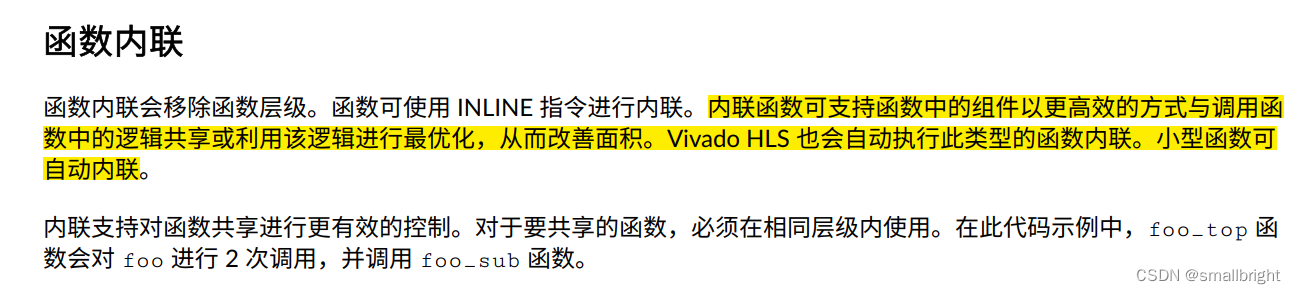

1.INLINE指令是大幅修改代码结构而不对源代码执行任何实际修改的强大方法,并可提供强大的架构探索方法。

2.ARRAY_MAP指令支持通过2种方式将多个小型数组映射到单一大型数据:

水平映射:这对应于通过并置原始数组创建新阵列。实际上,这作为含更多元素的单一数组来实现。

垂直映射:这对应于通过并置数组中的字词来创建新阵列。实际上,作为含较大位宽的单一数组来实现。

3.ARRAY_RESHAPE 指令将 ARRAY_PARTITIONING 与 ARRAY_MAP 的垂直模式相结合, 用于减少块 RAM 数量, 同时仍支持分区的有利特性: 并行访问数据。

4.ALLOCATION 指令允许您限制设计中使用的运算符、核或函数数量。例如, 名为 foo 的设计包含 317 次乘法, 但FPGA 仅有 256 项乘法器资源 (DSP48)。以下所示 ALLOCATION 指令可指示 Vivado HLS 创建含最多 256 个乘法 (mul)运算符的设计

参考文献:

UG998_采用Vivado高层次综合开展FPGA设计的简介(中文版)

UG902_Vivado设计套件用户指南:高层次综合(中文版)

540

540

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?