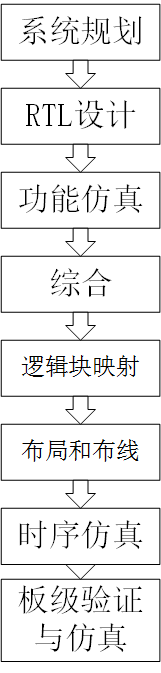

ASIC设计流程

前端流程

1.需求分析

2.功能架构设计

包括处理器架构的选择,总线接口的选择,软硬件功能的划分

3.RTL编码

使用硬件描述语言将模块功能以代码来描述实现。

4.功能仿真验证(前仿)

功能仿真,对 RTL 级的代码进行设计验证,检验设计功能的正确性,是否满足规格中的

所有要求。

仿真工具:Modelsim、VCS

5.逻辑综合

基于特定的工艺库,设定电路的面积、时序等目标参数的约束条件,将设计的 RTL 级代

码映射为门级网表 netlist。

综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真) 。

逻辑综合工具:Design Compiler

6.STA 静态时序分析

在 时序上对电路进行验证,检查电路是否存在 建立时间(setup time )和保持时间(hold

time )的违例。

STA 工具:Synopsys 的 Prime Time。 (PT)

7.形式验证Formality

从功能上对综合后的网表进行验证,将综合后的网表与验证后的 HDL 设计对比,看他们

是否在功能上存在等价性,保证逻辑综合过程中没有改变 HDL 描述的电路功能。

形式验证工具:Synopsys 的 Formality

后端流程

1.DFT

可测性设计,在设计中插入扫描链。他是一种集成电路设计技术,他将一些特殊结构在设计阶段植入电路,以便设计完成后进行测试。电路测试并不容易,这是因为电路的许多内部节点信号在外部难以控制和观测。通过添加可测试性设计结构,内部信号可以暴露给电路外部。测试目标为生产过程中的Dedect。对于Std Cell,Mem,I/O有不同的测试手段。

包括边界扫描测试Boundary Scan Test:测试封装与 IO、芯片间互联,主要逻辑有 TAP Controller 和 Boundary Scanchain)、JTAG(JTAG 是boundary scan design中用到的一个基本结构)。

内建自测试BIST:测试芯片中存储资源, rom 和 ram,在设计中插入内建自测试逻辑;

扫描测试(ATPG)

Scan Chain(扫描链),针对时序电路,测试寄存器(Flip-Flop)和组合逻辑;

DC/AC mode

ATPG(Automatic Test Pattern Generation,自动测试向量生成,基于扫描链,根据算法推算出应该加载到扫描链上的激励序列和期望序列,这样的序列称为测试向量);

DFT 构建硬件结构,ATPG 生成测试向量。

2.布局规划

放置芯片的宏单元模块, 在总体上确定各种功能电路的摆放位置, 能影响芯片的最终面积。

如 IP 模块、RAM、I/O 引脚等摆放位置。

工具:IC Compiler

3.时钟树综合

时钟的布线,时钟分布 H 型或树形,使时钟从同一个时钟源到达各个寄存器时,时钟延迟

差异最小。

工具:PC

4.布线

将前端提供的网表实现成版图,包括各种标准单元之间的走线。

5.寄存器参数提取

由于导线本身存在的电阻,相邻导线之间的互感、耦合电容在芯片内部会产生信号噪声、

串扰和反射。提取寄生参数进行再次分析验证,分析信号完整性问题。

6.物理版图验证

对布线完成的版图进行功能和时序上的验证

L VS:版图和逻辑综合后的门级电路图对比验证

DRC:设计规则检查,检查连线间距,连线宽度。

ERC:电气规则检查,检查短路开路。

实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的 DFM(可制造

性设计)问题。物理版图以 GDS II 的文件格式交给芯片代工厂(称为 Foundry)在晶圆硅片上

做出实际的电路,再进行封装和测试,就得到了可使用的芯片。

FPGA与ASIC的区别

ASIC是专用集成电路设计,设计具有专用性,优点:具有高性能,低功耗的优势。缺点:开发周期长,灵活性差。

FPGA时现场可编程逻辑阵列,优点:具有开发周期短,可编程性,可重构性强。缺点:功耗及性能不及ASIC。

FPGA流程

静态、动态时序模拟的优缺点

静态时序模拟:静态时序分析技术是一种穷尽分析方法,用以衡量电路性能。它提取整个电路的所有时序路径,通过计算信号在路径上的延迟传播找出违背时序约束的错误,主要是检查建立时间和保持时间是否满足要求,而它们又分别通过对最大路径延迟和最小路径延迟的分析得到。

它不需要输入向量就能穷尽所有的路径,分析速度快,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电路。

动态时序模拟:动态时序模拟是在验证功能的同时验证时序,需要输入向量作为激励。随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,且这种方法难以保证足够的覆盖率。

动态时序模拟的优点是比较精确,而且同静态时序模拟相比较,它适用于更多的设计类型。

但是它也存在着比较明显的缺点:首先是分析的速度比较慢;其次是它需要使用输入矢量,这使得它在分析的过程中有可能会遗漏一些关键路径,因为输入矢量未必是对所有相关的路径都敏感的。

1525

1525

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?