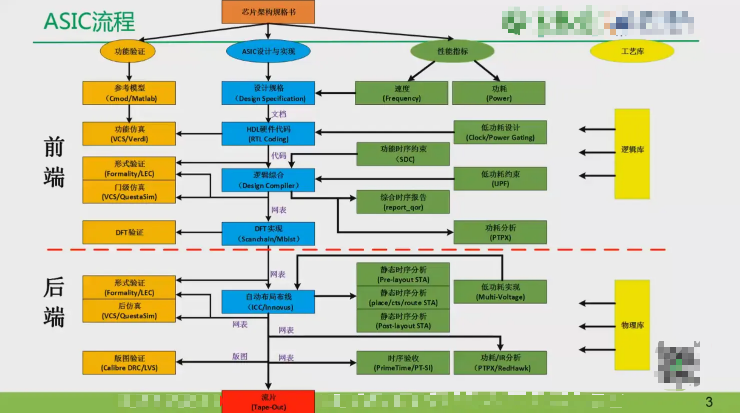

第一课:ASIC设计基本流程

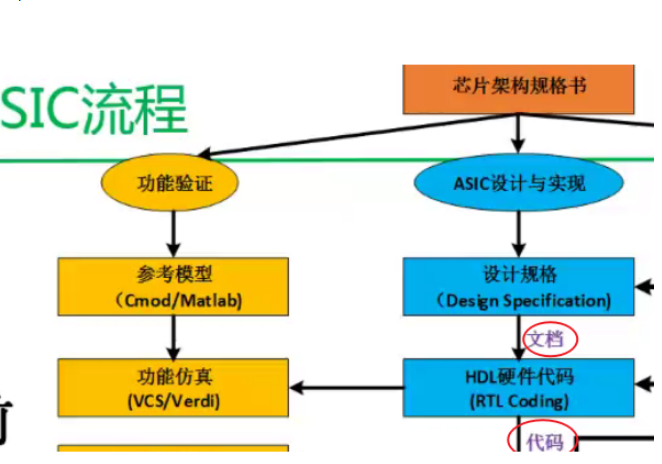

ASIC(Application Specific Integrated Circuit)设计概要图

注:ASIC与FPGA的优缺点对比:FPGA可看作为一种较通用芯片,可以通过代码来实现不同的功能,问题是芯片的面积利用率较低,导致成本增大,同时利用的性能不高;而ASIC为专用芯片,面积充分利用,且性能通过专门设计优化大幅提升。

以上为ASIC芯片设计的大致流程,中间蓝色部分为功能实现,左侧部分为功能验证,验证中间设计的转换过程有没有出错;右侧为对应所需的性能指标,因为你芯片设计出来,不仅要实现相应的功能,同时还要达到性能指标,才能商业化。人在芯片设计流程中,除了前端设计外,主要做的是左右侧的验证内容,中间的内容都有专门的工具做;下面分别讲述每个模块对应的内容:

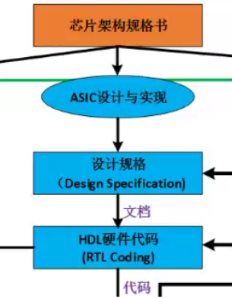

1:芯片架构书是是市场经理结合客户及市场需求后,交给架构师,架构师再设计出架构书,架构书内部含有一些大体的Spec,如芯片要实现的功能、用什么算法等;而作为前端设计师,首先要做的就是从硬件层面考虑,把架构书中的大方面Spec转化为很多具体的小Spec,得到具体的Spec文档,然后再编写为Verilog代码,这其中写代码是后一步,前一步一定要把具体的Spec做好做细致,后面写代码才会少出问题,一般定Spec文档和写代码的时间为1:1。

2: Verilog语言描述硬件行为一般有三个层次:行为级/寄存器传输级/门级,其中一般用寄存器传输级效率最高,即RTL Coding(Register Transfer Level);

So,为什么选择寄存器传输级来描述呢?/为什么寄存器传输效率最高?

答:根据寄存器的特性:①寄存器可以存储数据,只有时钟沿来了才会改变数据,其他时候数据保持不变,故只需要描述在时钟沿来的那一刻的变化行为即可,其他时刻无需描述;②寄存器变化受时钟沿同步控制,便于描述功能,如某时刻将寄存器A的值给到B;设想一下,十几万个寄存器,大家必须听从统一的命令,不然无法正常运行;

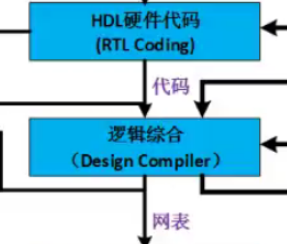

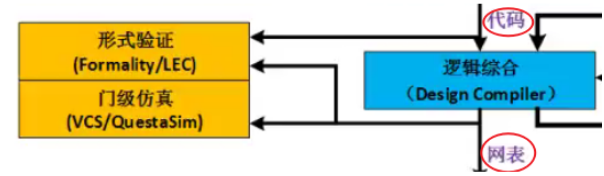

逻辑综合:从RTL Coding,经过EDA工具,EDA工具根据一些规则,得到门级网表,这整个一步就叫逻辑综合;以前没有EDA工具时,是直接写门级网表的,即对应上述的Verilog语言描述硬件行为的第三个层次;EDA厂商:Synopsys/Cadence/Mentor;

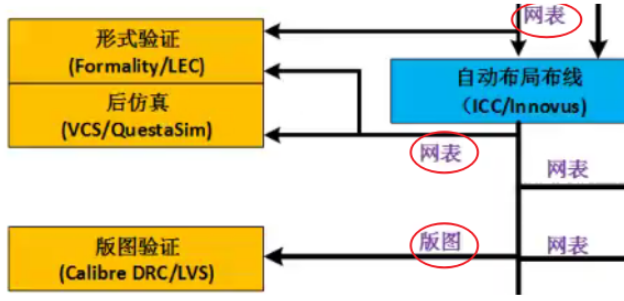

门级网表经过EDA工具自动布局布线APR (Auto Place and Route)后,得到版图,最后将版图交给代工厂流片;

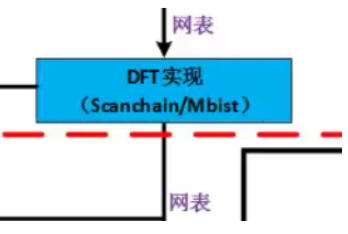

DFT(Design For Test):可测性设计,用于芯片在流片回来后,测试芯片在制造过程中有没有出现问题,先进性DFT测试,确保无问题后在进行功能测试; 为了实现 此功能,需要在网表中加一点内容进去,即Scanchain,通俗讲即将所有寄存器用一根链连起来,通过一个引脚灌入测试pattern,根据输出是否符合预期进行判断,

验证方面,同样根据架构书得到验证Spec而不参考设计Spec(后面再看二者的结果,一致则表明设计无问题),再利用高级语言建立参考模型,利用参考模型对RTL Coding进行功能验证--即功能仿真,通过参考模型检验RTL代码是否符合参考模型的行为,或者说,将一个激励同时灌给参考模型和RTL代码,观察输出,若每个case的输出都是相等的,则认为RTL代码等价于参考模型;功能仿真是一种动态仿真,即给激励,观察输出,只有动起来的地方才能仿真到,没有擦写的部分是无法仿真到的,故要尽可能的给出多的case,以致将更多的地方动起来,都仿真到;功能仿真完成后,证明设计Spec文档到RTL代码的转换是OK的;

RTL代码经过逻辑综合后,得到门级网表,那么怎么保证这个过程没有出bug呢?形式验证和门级仿真。门级仿真和功能仿真类似,是一种动态仿真,将case在网表代码中跑一边,观察输出是否符合预期,这一过程叫门级仿真,但门级仿真较慢,无法把所有case都跑一边,故只是一种辅助验证方法,不可取;形式验证是一种静态功能仿真,是可取的;形式验证将代码和网表全部拆分成一小块一小块,将每一小块进行对比,若每一小块都是相等的,则认为RTL代码和网表代码完全等同,对功能进行Signoff。

网表经过APR后得到版图的同时,也会得到另一份网表,则APR前后的网表可通过形式验证和后仿来判断是否等价;后仿真时(动态仿真),由于已经完成布线了,则连线延时可以算出来了,则可以进行带延时的仿真,目的一是为了功能,二是为了时序,但后仿也是无法跑完所有case,只能作为一种辅助方法。 版图验证即物理验证,是将APR后的网表和版图进行验证,保证二者等价,最后版图Signoff,常用Calibre 的DRC/Layout Verify Schematic;

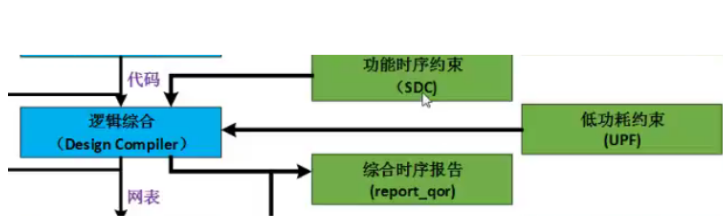

在进行逻辑综合转换时,还会加入功能时序约束条件,即决定电路运行速度的快慢;转换得到网表后,要看是否达到我们的时序要求,即得到综合时序报告,在对时序进行分析;

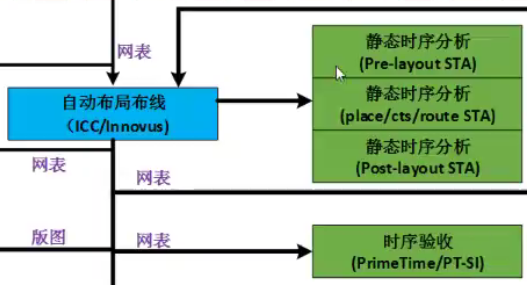

在综合逻辑和自动布局布线时,工具自身也会对时序进行分析,但精度可能有限--APR之前的网表需要进行静态时序分析(Static Timing Anlysis),布局Place/时钟树CTS/布线Route每一步,及APR完成后得到的网表都需要进行STA分析; 最后,人为分析时序,进行时序验收Signoff;

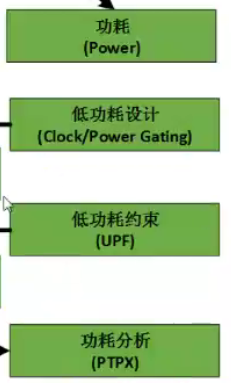

芯片功耗的产生,分为动态功耗和静态功耗,其中动态功耗占主要部分,动态功耗即晶体管开关产生的功耗;静态功耗即晶体管不工作时产生的线路功耗;

低功耗设计:①Clock Gating:芯片中的不同部分并不是同时都在工作的,将部分不工作的寄存器时钟关闭,需要工作时在打开;②Power Gating:将不工作的寄存器模块电源关闭,这样连线路功耗都没有了;

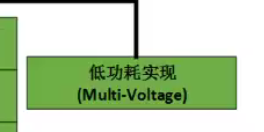

后端时,可能不同的电源域电压不同,二者产生信号交互时电压不同需要进行一些匹配处理;

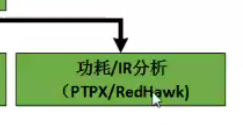

最后的IR分析,即线路压降分析,当一个power驱动一个门时,若线路过长,产生的压降较大,则一个power可能无法驱动该门的工作,需要考虑是否要再加一个power等;

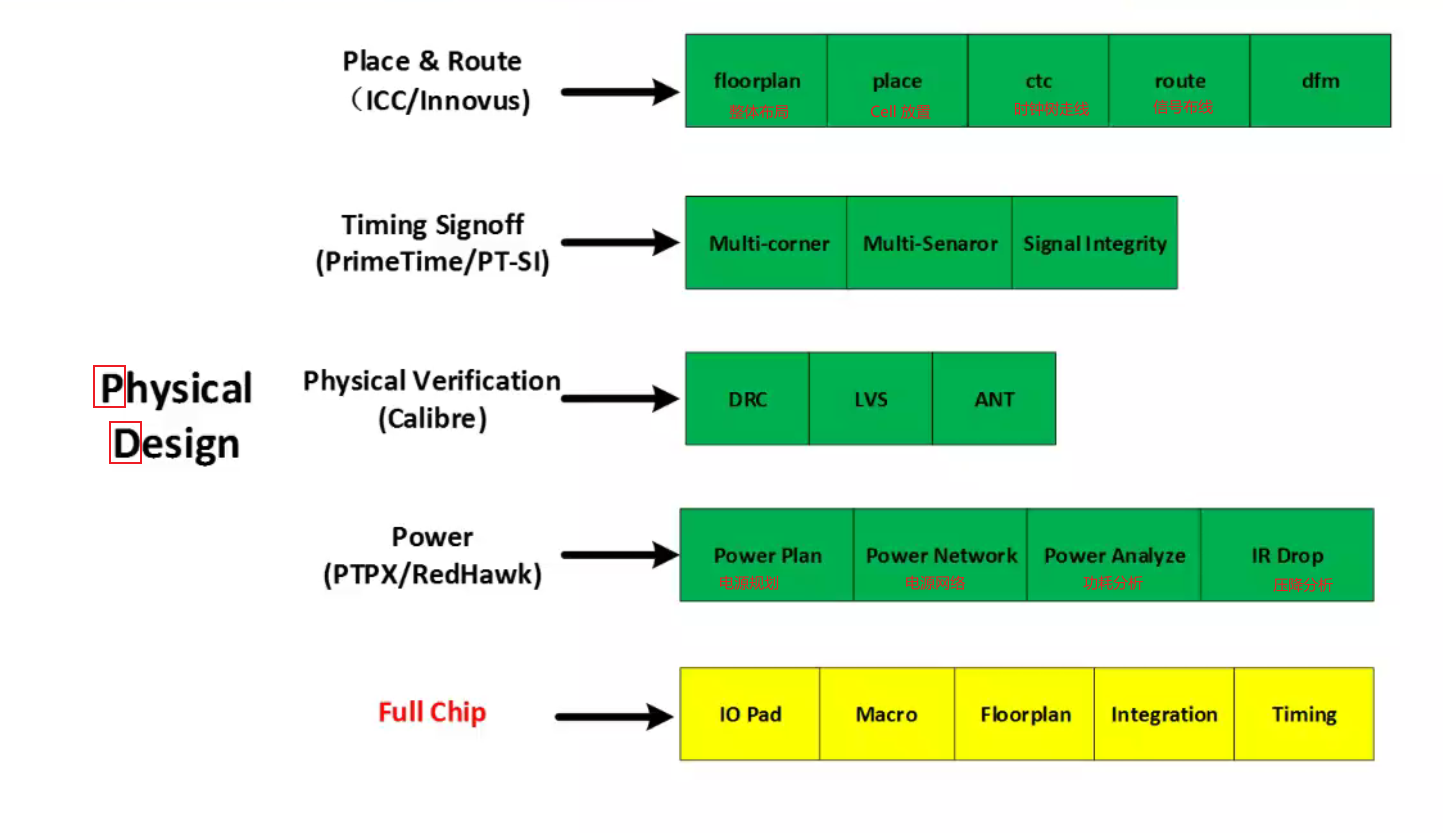

最后总结一下后端工程师PD的大致工作~

1308

1308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?