时钟偏移

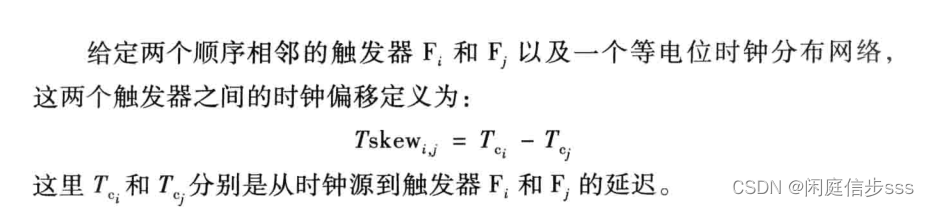

整个芯片中时钟信号到达时间的差异称为时钟偏移。时序必须满足寄存器建立和保持时间的要求是基本设计原则。数据传播延迟和时钟偏移都用于与之相关的计算。对于同一时钟边沿偏移较大的寄存器,如果顺序相邻,那么在向其提供时钟时,就会有违背时序的潜在风险,甚至使功能失效。这是ASIC设计失败最主要的原因。

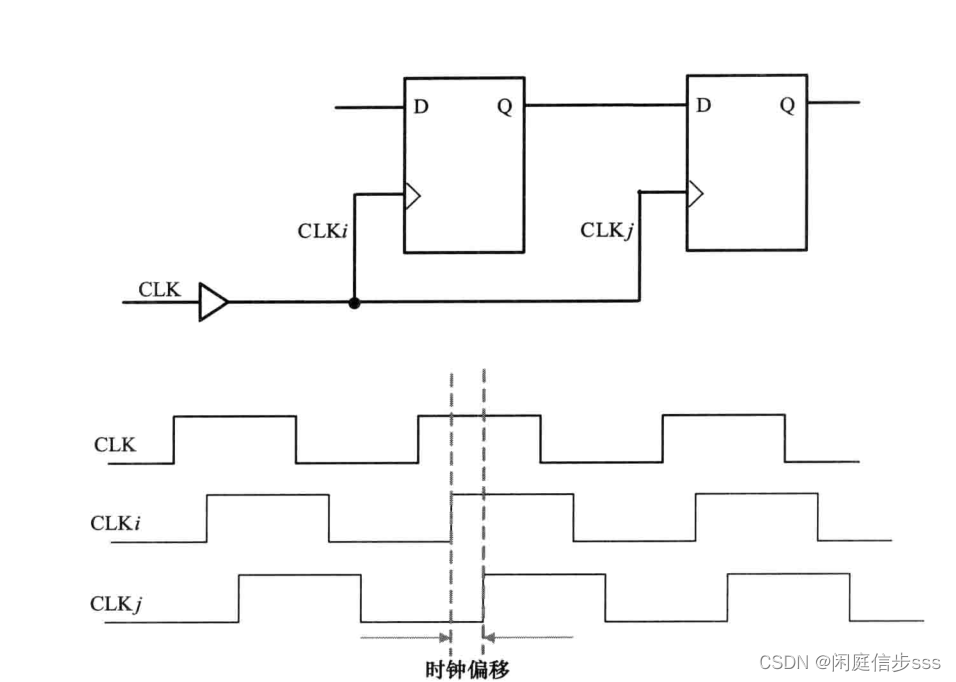

下图为两个顺序相邻触发器时钟偏移的例子。

短路径问题

时钟偏移中的短路径问题与触发器的保持时间违背很相似。在两个相邻触发器之间的数据传播延迟比时钟偏移还短时,就会出现该问题。

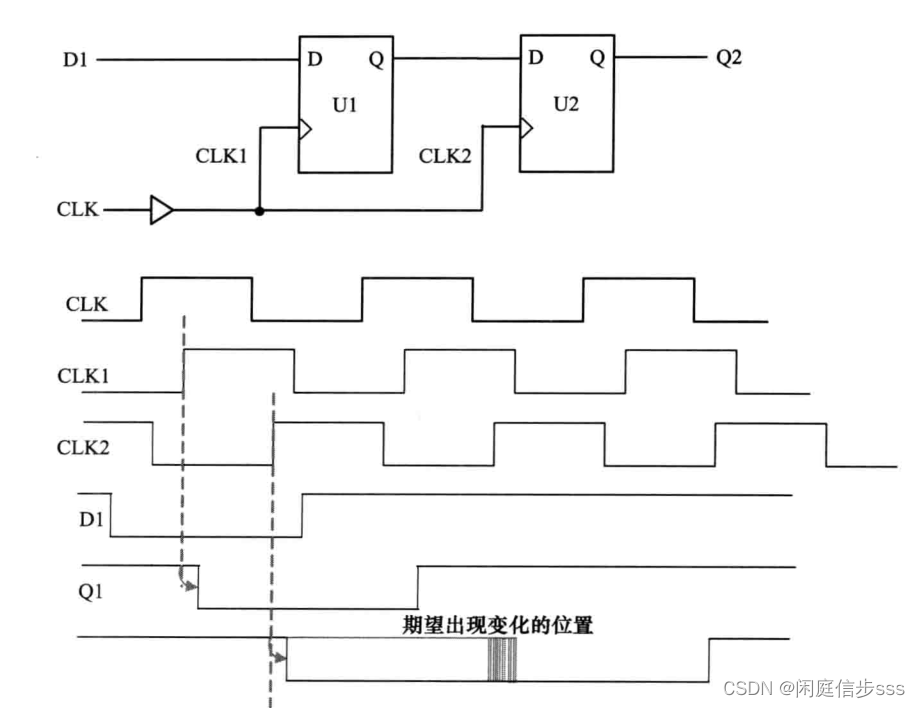

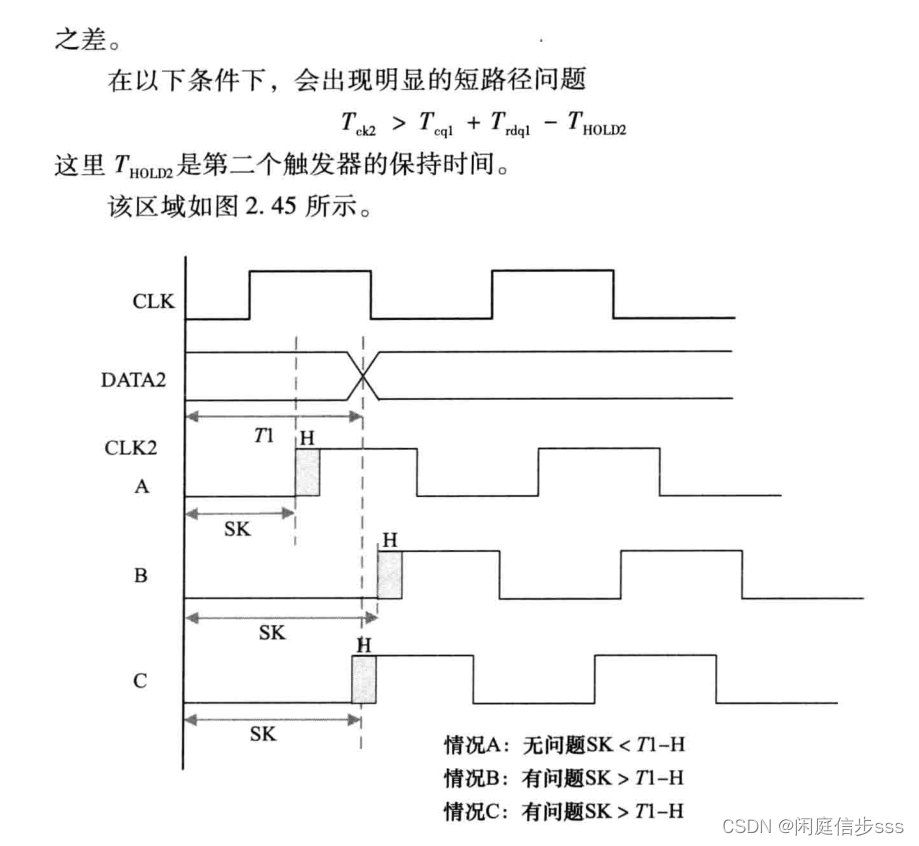

下图的电路图和时序图可以说明短路径问题

由于同一个时钟沿到达第二个触发器比新数据要慢,因此第二个触发器在与第一个触发器同样的边沿处,切换为与第一个触发器同样的值。这会使U2在与U1同一个边沿处移位同样的数据,最终导致功能错误。

时钟偏移和短路径分析

之前提到,在两个顺序上相邻的触发器之间的数据路径传播延迟比两者之间的时钟偏移小时,会出现时钟偏移和短路径问题

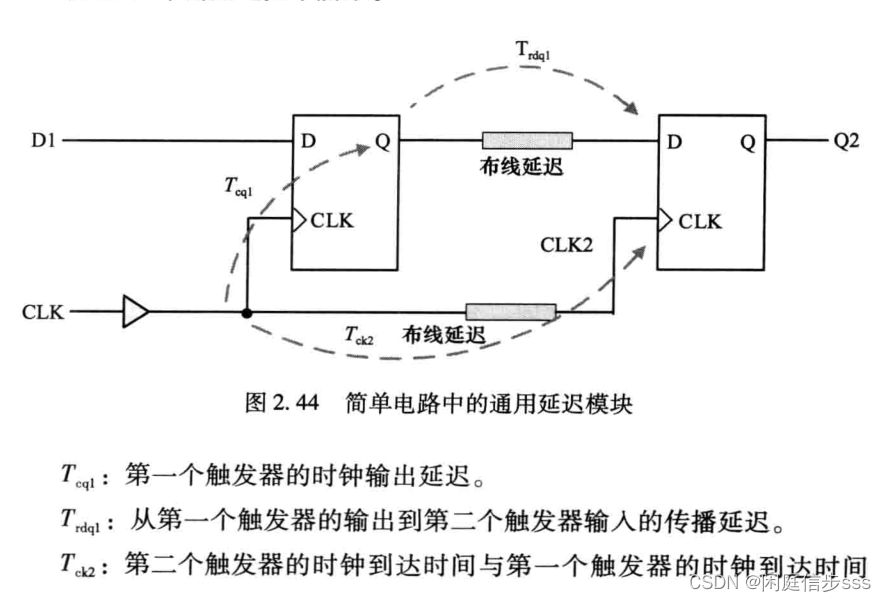

延迟如下图所示:

因此,为了识别带有该问题的路径,用户必须提取出时钟偏移(如Tck2)和短路径延迟(如Tcq1+Trdq1-Thold2)。

短路径问题解决方法

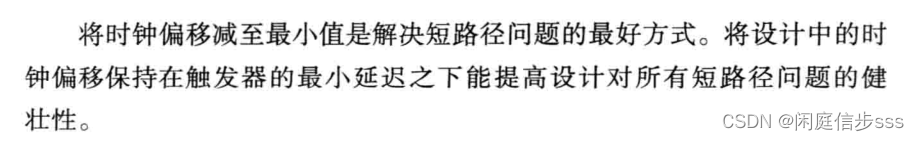

使时钟偏移最小化。

在数据路径上加入延迟

通过在数据路径上增加延迟(Trdq1)而最终使整个数据路径的延迟大于时钟偏移,可以消除短路径问题。

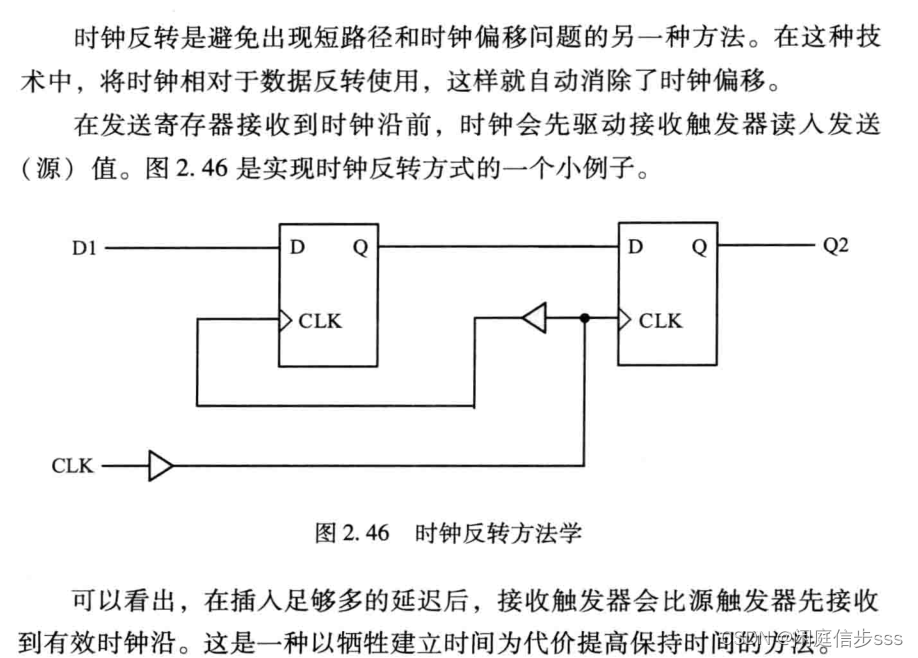

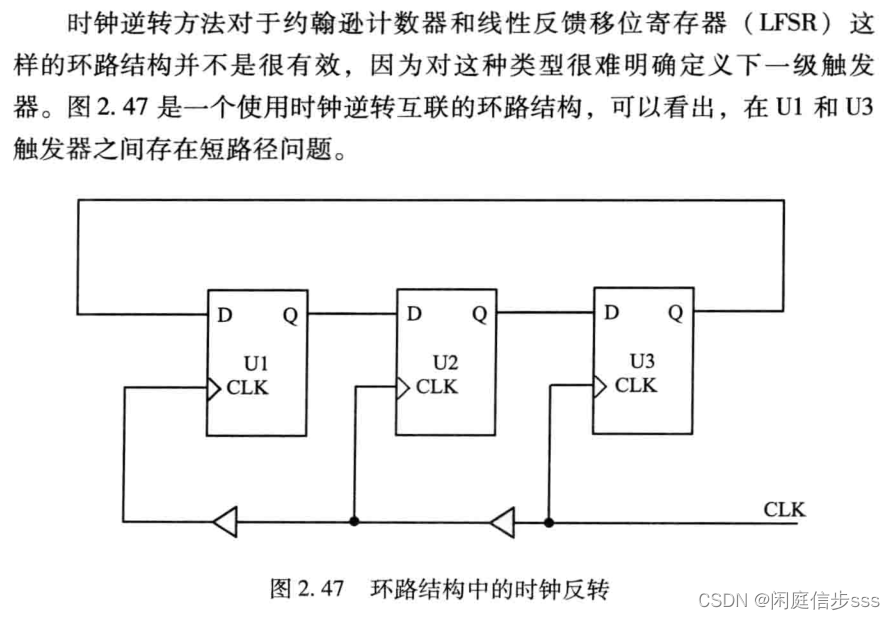

时钟反转

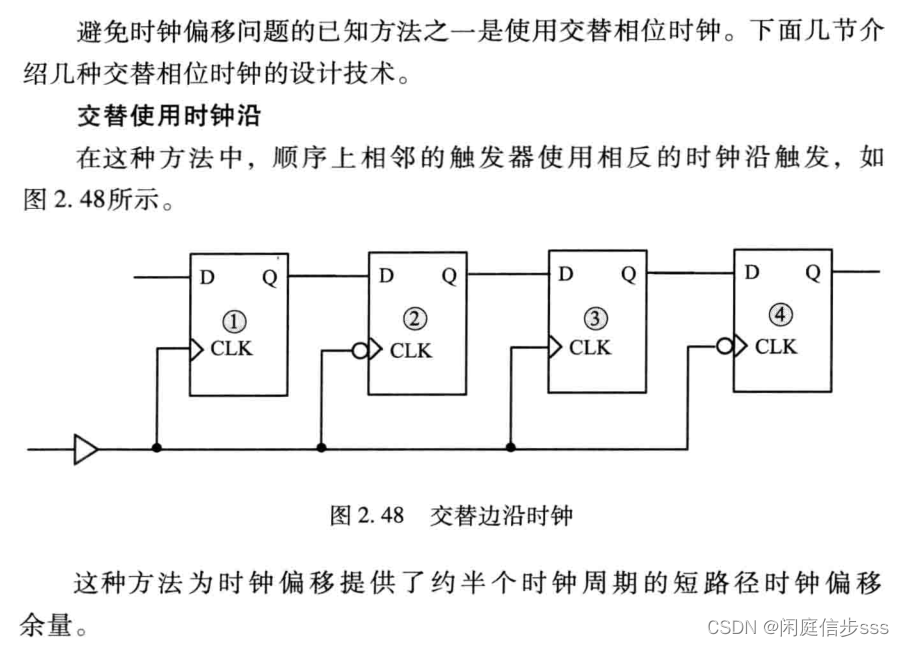

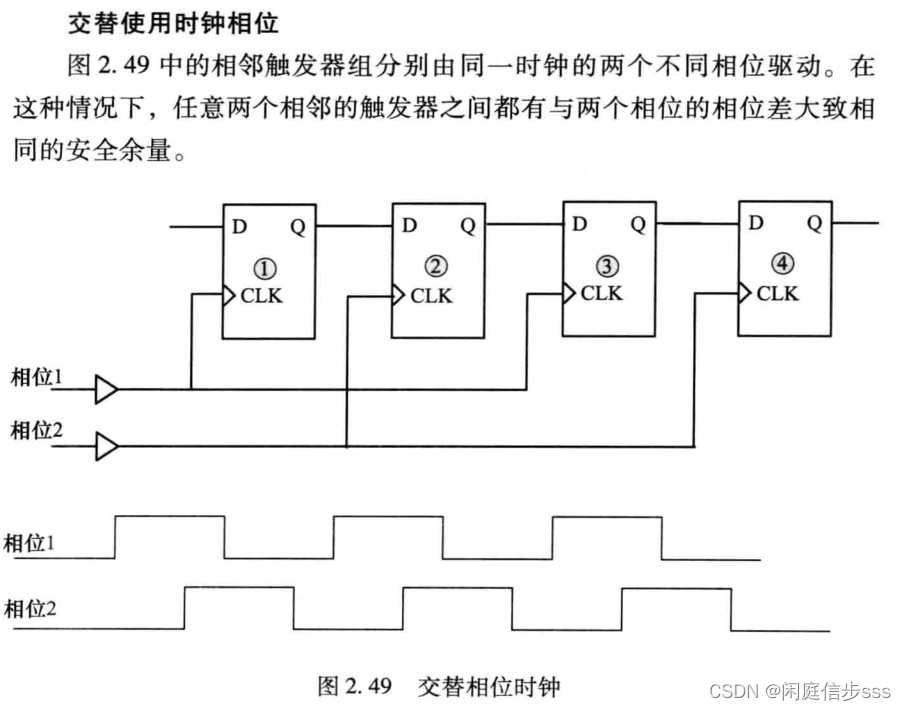

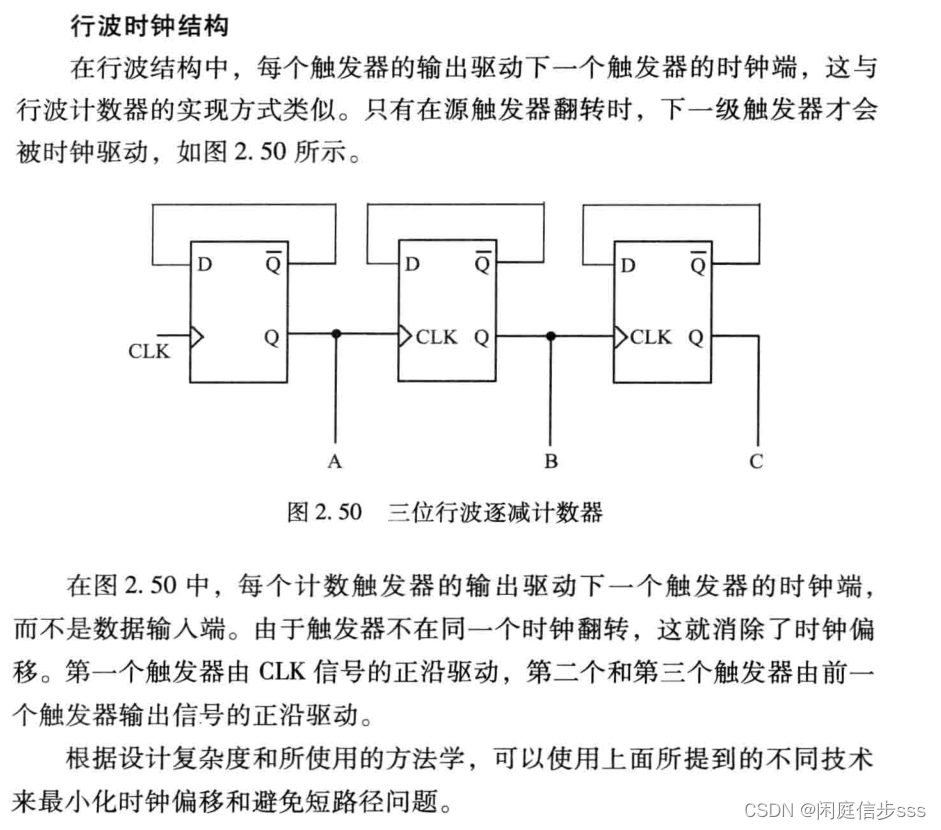

交替使用相位时钟

3142

3142

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?