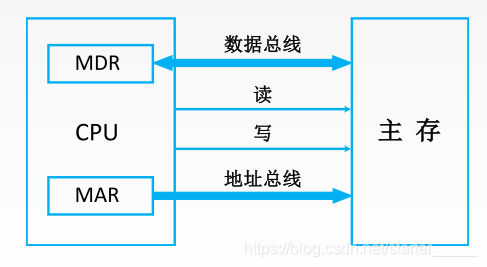

一、连接原理

- 主存储器通过数据总线、地址总线和控制总线与CPU连接

- 数据总线的位数与工作频率的乘积正比于数据传输率

- 地址总线的位数决定了可寻址的最大内存空间

- 控制总线(读/写)指出总线周期的类型和本次输入/输出操作完成的时刻

- 合理选择存储芯片:通常选用ROM存放系统程序、标准子程序和各类常数、RAM则是为用户编程而设置的

- 地址线的连接:CPU的地址线数往往比存储芯片的地址线数多。

CPU地址线的低位和存储芯片的地址线相连,以选择芯片中某一单元(字选),这部分的译码是由芯片的片内逻辑完成的。

CPU地址线的高位则在扩充存储芯片时使用,用来选择存储芯片(片选),这部分译码由外接译码器逻辑完成 - 数据线的连接:CPU的数据线数与存储芯片的数据线数不一定相等,在相等时可直接相连;在不等时必须对存储芯片扩位,使其数据位数与CPU的数据线数相等

- 读/写命令线的连接:CPU读/写命令线一般可直接与存储芯片的读/写控制端相连,通常高电平为读,低电平为写

- 片选有效信号:片选有效信号与CPU的访存控制信号(MREQ)’(低电平有效)有关,因为只有当CPU要求访存时,才要求选中存储芯片。若CPU访问i/O,则(MREQ)’ 为高,表示不要求存储器工作。

二、片选方式

- 线选法:当某地址线信息为”0’时,就选中与之对应的存储芯片。A15A14A13=110A_{15}A_{14}A_{13}=110A15A14A13=

本文详细介绍了主存储器如何通过数据总线、地址总线和控制总线与CPU连接,强调了地址线和数据线的连接方式以及片选的有效信号。在片选方式部分,讲解了线选法和译码片选法的工作原理,帮助理解存储器的选择机制。

本文详细介绍了主存储器如何通过数据总线、地址总线和控制总线与CPU连接,强调了地址线和数据线的连接方式以及片选的有效信号。在片选方式部分,讲解了线选法和译码片选法的工作原理,帮助理解存储器的选择机制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1065

1065

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?