普通双阱的缺点

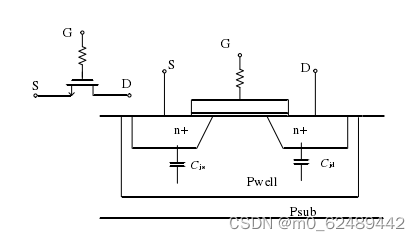

普通双阱NMOS横截面示意图

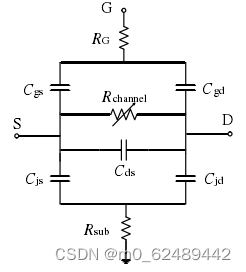

普通双阱NMOS小信号电路图

如图所示,为交叠寄生电容,

为寄生PN结电容,

为衬底连接电阻。

当MOS作为串联开关导通时,由于寄生电容的存在,信号容易通过电容耦合泄露至衬底。且由于

较小,信号又从P衬底泄露至地,导致插入损耗恶化。

同样,假设信号由漏极输入,因为较小,则漏极-

寄生支路上存在较大的信号摆幅,且该信号压降多数由

承担,限制MOS线性度。

假设衬底电阻过大。当MOS作为串联开关关断时,由于

耦合,且

过大,则信号容易从漏极耦合至源极,从而恶化开关的隔离度性能。

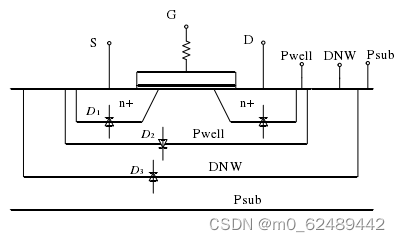

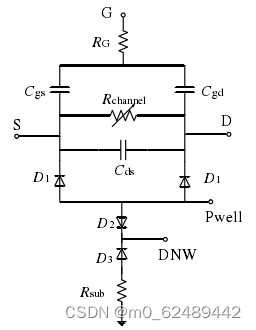

深N阱MOS优化

为寄生二极管。

何为深N阱MOS?

深N阱MOS在P阱与P衬底之间加入深N阱层。用以提高MOS在有源区与衬底之间的隔离度,减少信号耦合泄露。

将P阱、深N阱、P衬底偏置在合理的直流电压下,使处于反偏状态,就可以在不恶化

的情况下优化插入损耗。

为了提高隔离度,采用深N阱MOS开关设计,通常需要加入并联MOS管,构成串并联结构开关。

本文探讨了普通双阱NMOS中存在的寄生电容及电阻等问题,并介绍了如何通过使用深N阱MOS来改善信号耦合泄露和开关性能。深N阱MOS能够在不恶化插入损耗的情况下提高有源区与衬底之间的隔离度。

本文探讨了普通双阱NMOS中存在的寄生电容及电阻等问题,并介绍了如何通过使用深N阱MOS来改善信号耦合泄露和开关性能。深N阱MOS能够在不恶化插入损耗的情况下提高有源区与衬底之间的隔离度。

375

375

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?