本文对读到的两篇文章进行补充

文2:被文1引用,详细介绍了原理图和代码

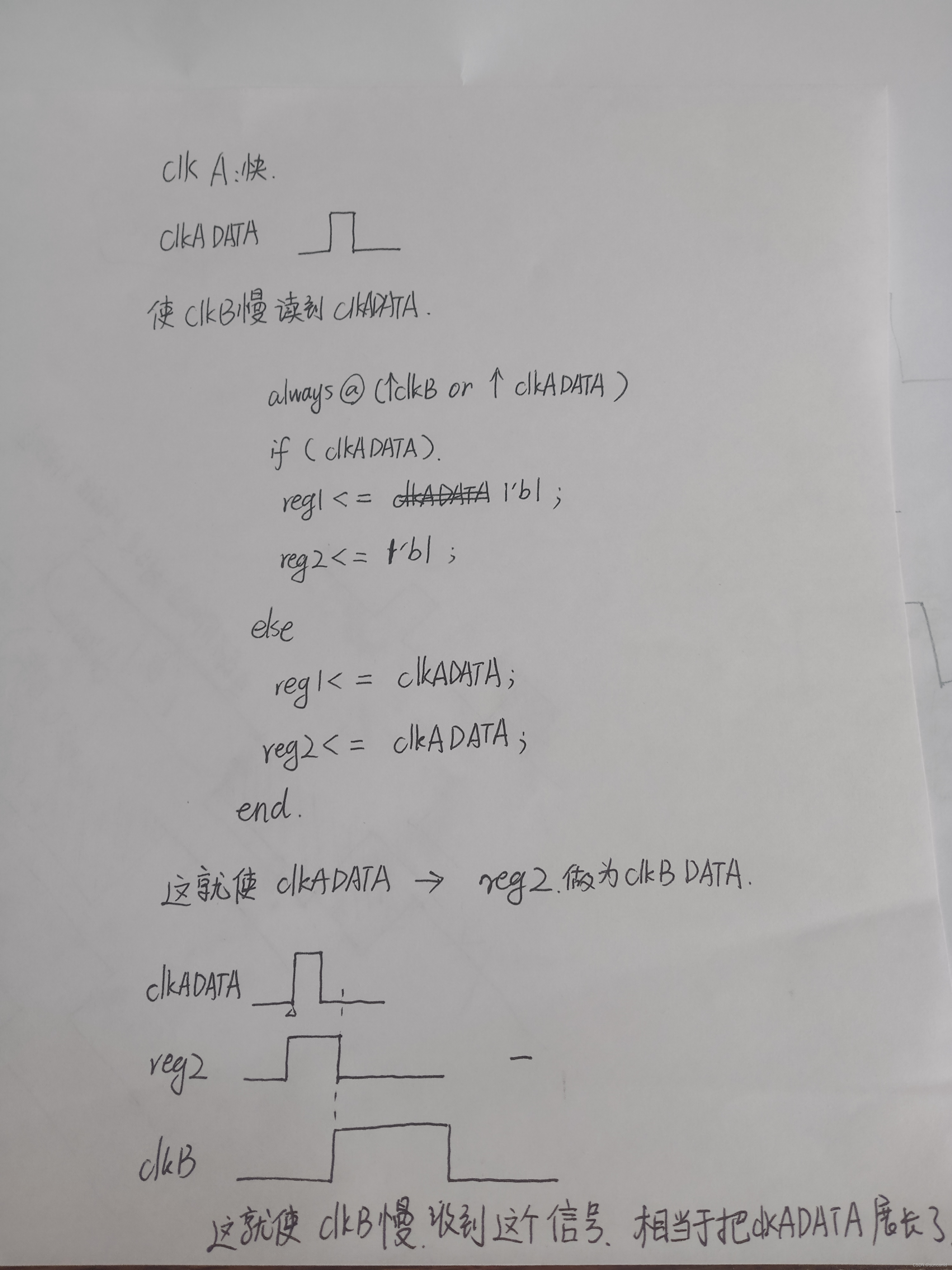

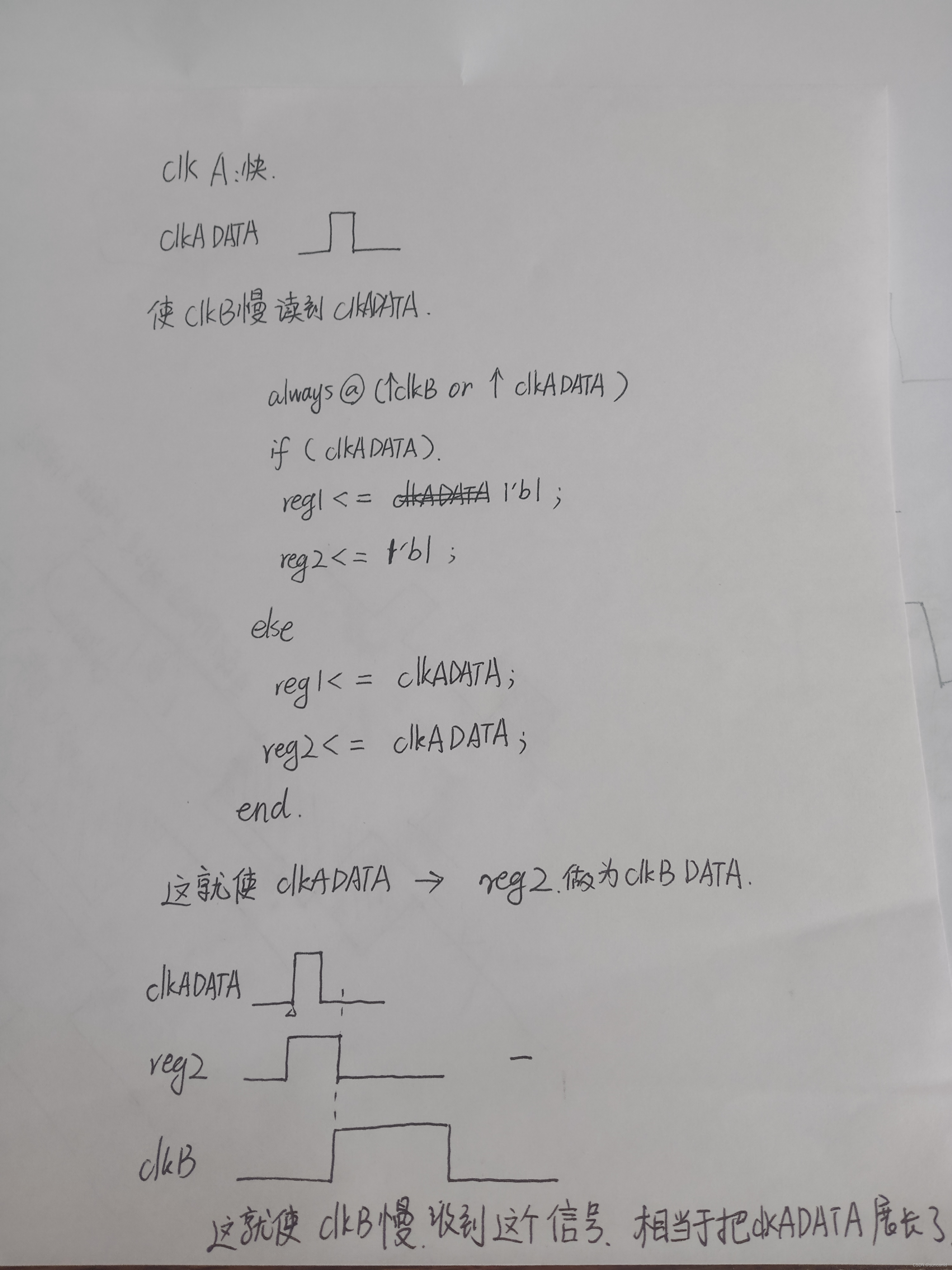

那个图,我认为是这么个意思

本文对读到的两篇文章进行补充

文2:被文1引用,详细介绍了原理图和代码

那个图,我认为是这么个意思

2922

2922

7253

7253

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?