目录

快时钟域到慢时钟域

如果 CDC 信号在时钟域之间传递时不能被跳过,则在时钟域之间传递时考虑信号的宽度和同步技术很重要。

与同步器相关的一个问题是,来自发送时钟域的信号可能会在采样之前更改两次值,或者可能过于接近较慢时钟域的采样边沿。这种可能性必须考虑到任何时间信号从一个时钟域发送到另一个时钟域,并且必须确定丢失的信号对于所讨论的设计是否存在问题。

当不允许丢失样本时,有两种解决问题的一般方法:

(1)一种开环解决方案,以确保在没有确认的情况下捕获信号。

(2)一个闭环解决方案,需要确认接收到的信号通过 CDC 采样边界。

本节将讨论这两种解决方案。

时钟域间可靠信号传递的要求

如果较快时钟域的频率是较慢时钟域的频率的 1.5 倍(或更多),则将较慢的控制信号同步到较快的时钟域通常不是问题,因为较快的时钟信号将对较慢的 CDC 信号进行一次或多次采样。将较慢的信号采样到较快的时钟域中比将较快的信号采样到较慢的时钟域中导致的潜在问题更少,设计人员可能会利用这一事实,通过使用简单的两个触发同步器在时钟域之间传递单个 CDC 信号。

“三边沿”要求

Mark Litterick 指出,当通过双触发同步器在时钟域之间传递一个 CDC 信号时,CDC 信号的宽度必须大于接收域时钟周期宽度的 1‑1/2 倍。 Litterick 将此要求描述为“输入数据值必须在三个目标时钟边沿保持稳定”。

对于非常长的源时钟和目标时钟频率,这个要求可能可以安全地放宽到接收时钟域周期时间的 1‑1/4 倍或更小,但是“三边沿”指南是最安全的初始设计条件,并且是通过使用 SystemVerilog 断言比在仿真期间动态测量 CDC 信号的分数宽度更容易证明。

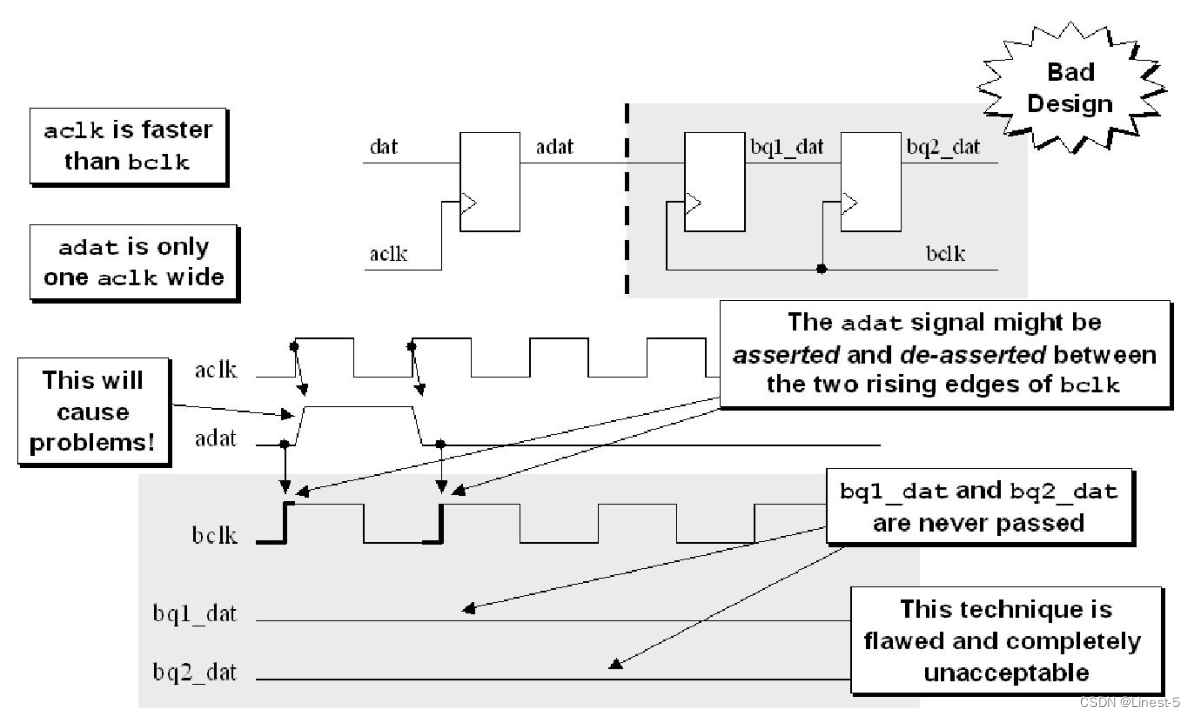

问题 ‑ 通过快速 CDC 脉冲

考虑发送时钟域的频率高于接收时钟域的严重缺陷情况,并且 CDC 脉冲在发送时钟域中只有一个周期宽。如果 CDC 信号仅在一个快速时钟周期内产生脉冲,则 CDC 信号可能会在较慢时钟的上升沿之间变为高电平和低电平,并且不会被捕获到较慢时钟域中,出现漏采的情况,造成数据丢失,如图所示。

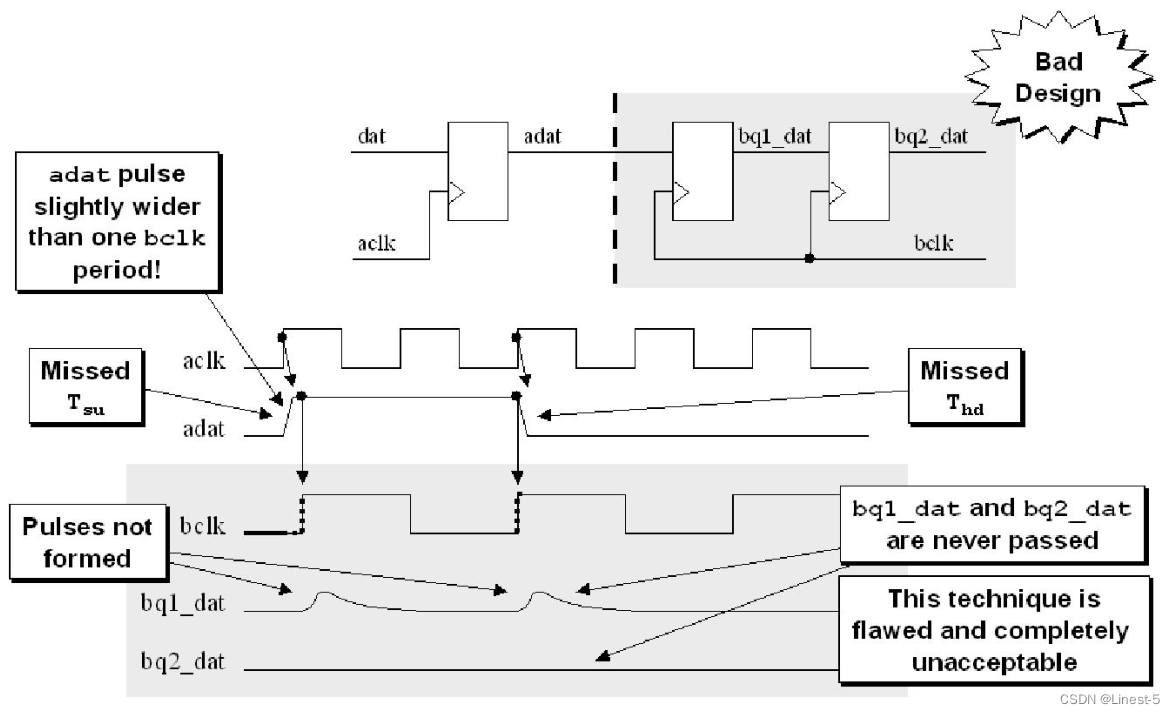

问题 ‑ 对长 CDC 脉冲进行采样 ‑ 但时间不够长

考虑有点不直观和有缺陷的情况,其中发送时钟域向接收时钟域发送一个脉冲,该脉冲比接收时钟频率的周期略宽。在大多数情况下,信号将被采样并通过,但 CDC 脉冲变化太接近接收时钟域的两个上升时钟沿,并因此违反第一个时钟沿的建立时间可能性很小,但违反了第二个时钟沿的保持时间而不形成预期的脉冲。这种可能的问题如图所示。

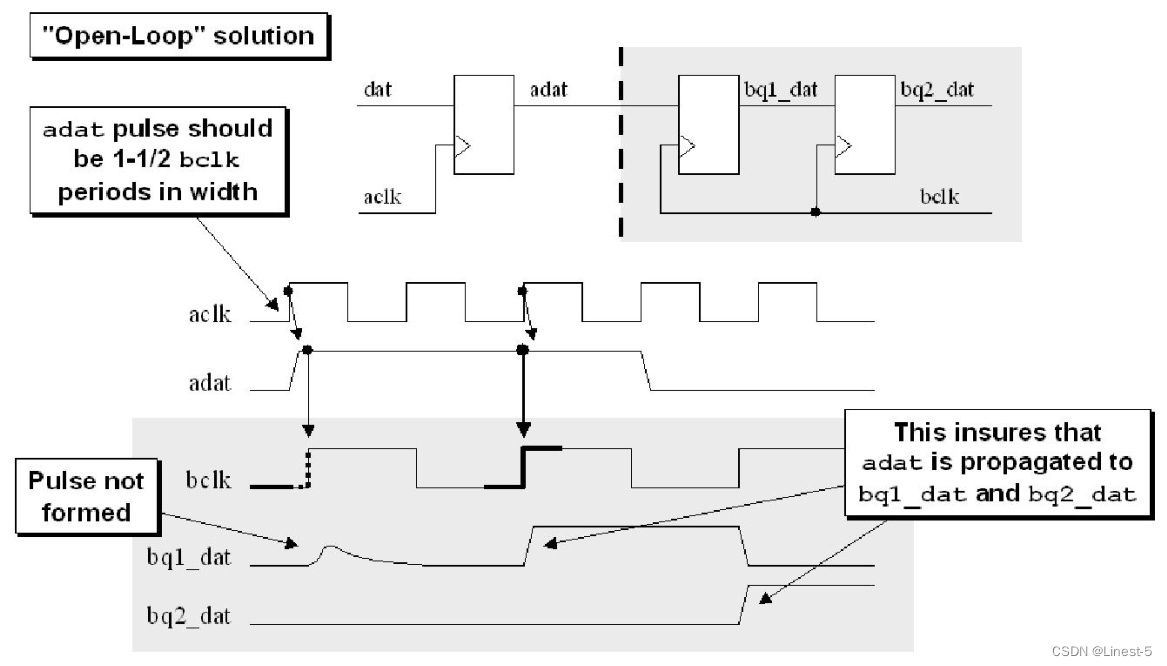

开环解决方案 ‑ 使用同步器采样信号

这个问题的一个潜在解决方案是在超过采样时钟周期的时间段内置位 CDC 信号,如下图所示。如前面所述,最小脉冲宽度是采样时钟周期的 1.5 倍。接收时钟频率。假设是 CDC 信号将被接收器时钟至少采样一次,并且可能采样两次。

当相对时钟频率固定并正确分析时,可以使用开环采样。

优点:开环解决方案是通过 CDC 边界传递信号的最快方式,无需确认接收信号。

缺点:与开环解决方案相关的最大潜在问题是其他工程师可能会将解决方案误认为是通用解决方案,或者设计要求可能会发生变化,并且工程师可能无法重新分析原始开环解决方案。这个问题可以通过向模型添加 SystemVerilog 断言来检测输入脉冲是否未能超过“三个边缘”设计要求来最小化。

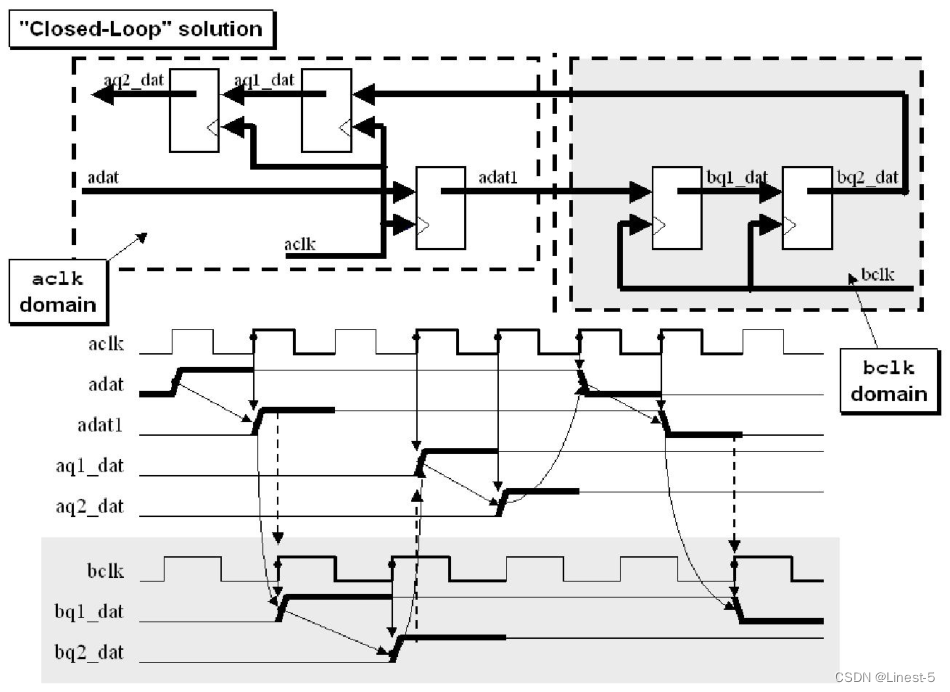

闭环解决方案 ‑ 使用同步器采样信号

该问题的第二个潜在解决方案是发送启用控制信号,将其同步到新的时钟域,然后将同步信号通过另一个同步器传递回发送时钟域作为确认信号。

更详细的说明,发送时钟域 aclk 对信号打一拍形成 adat1,然后给接收时钟域 bclk 打一拍形成 bq1_dat,在 bclk 中对 bq1_dat 再打一拍形成 bq2_dat,然后发送时钟域 aclk 对 bq2_dat 打一拍形成 aq1_dat 作为反馈信号,然后再 aclk 再打一拍形成 aq2_dat 作为二级反馈信号,发送时钟域 aclk 检测到aq2_dat 时将信号拉低,然后在 aclk 中打一拍作为接收端时钟域的采样信号,接收时钟域 bclk 对 adat1 进行打一拍形成最终的 bq1_dat 信号,然后 bq2_dat 对 bq1_dat 打一拍,最终实现将发送端时钟域 aclk 的信号同步到接收端时钟域 bclk 上。

优点:同步反馈信号是一种非常安全的技术,可以确认第一个控制信号已被识别并采样到新的时钟域。

缺点:在允许控制信号改变之前,在两个方向上同步控制信号可能存在相当大的延迟。

说明

本文是对《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》的文章的翻译及部分说明解释

往期系列博客

4848

4848

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?