3.1创建Vivado工程

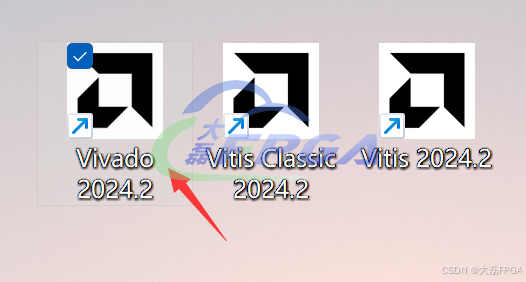

在本教程《ZYNQ视频图像处理》中使用的Vivado版本为Vivado 2024.2,Vitis版本为Vitis Classic 2024.2。其他版本的Vivado和Vitis同样可以使用,在某些操作界面或者流程上可能略有差异。

1、在双击下图中红色箭头所指示的图标打开Vivado 2024.2:

图 3.1.1 双击图标打开Vivado 2024.2

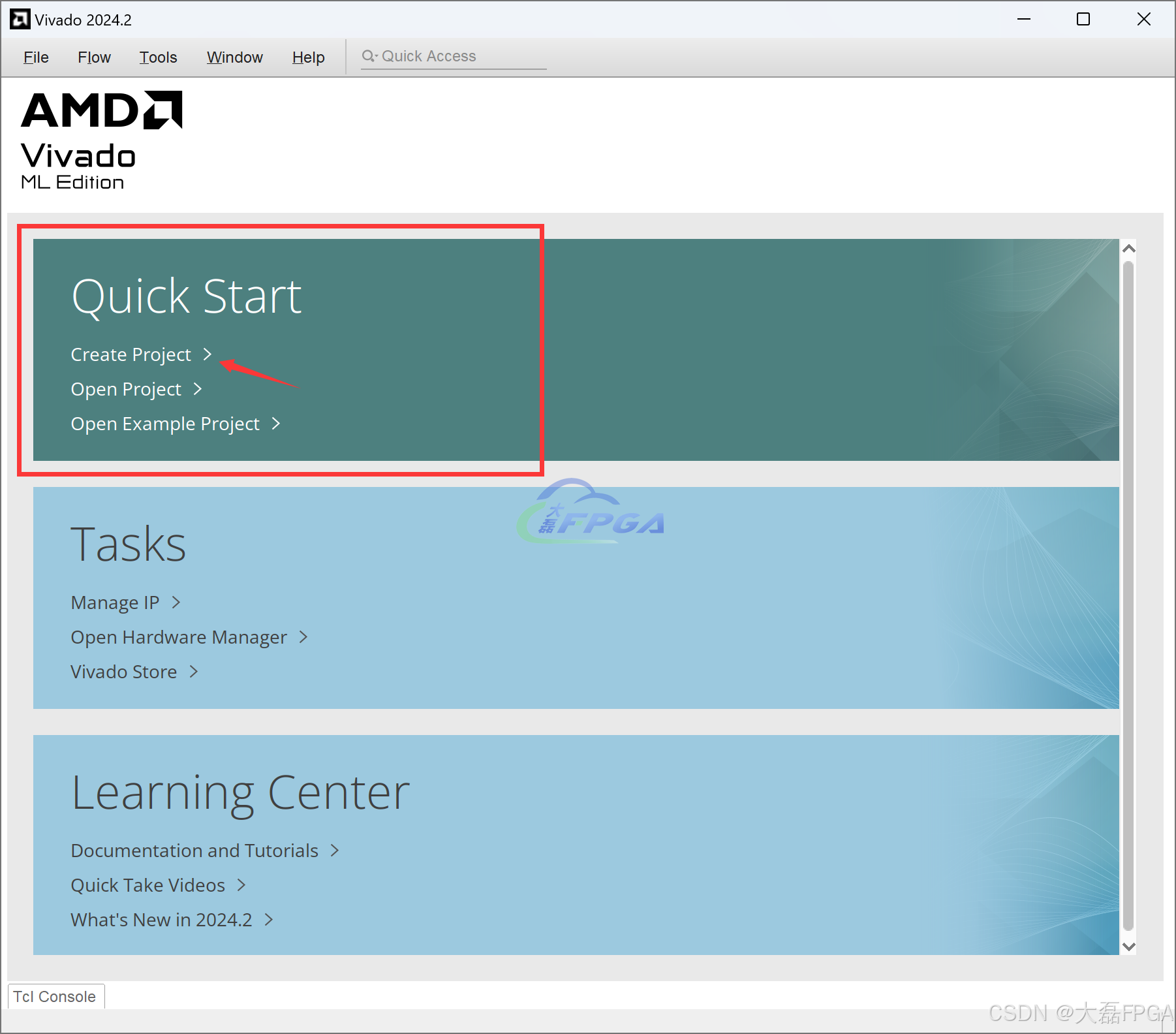

2、Vivado 2024.2启动后的界面如下图所示,点击Quick Start一栏中的Create Project创建工程:

图 3.1.2 Vivado 2024启动界面

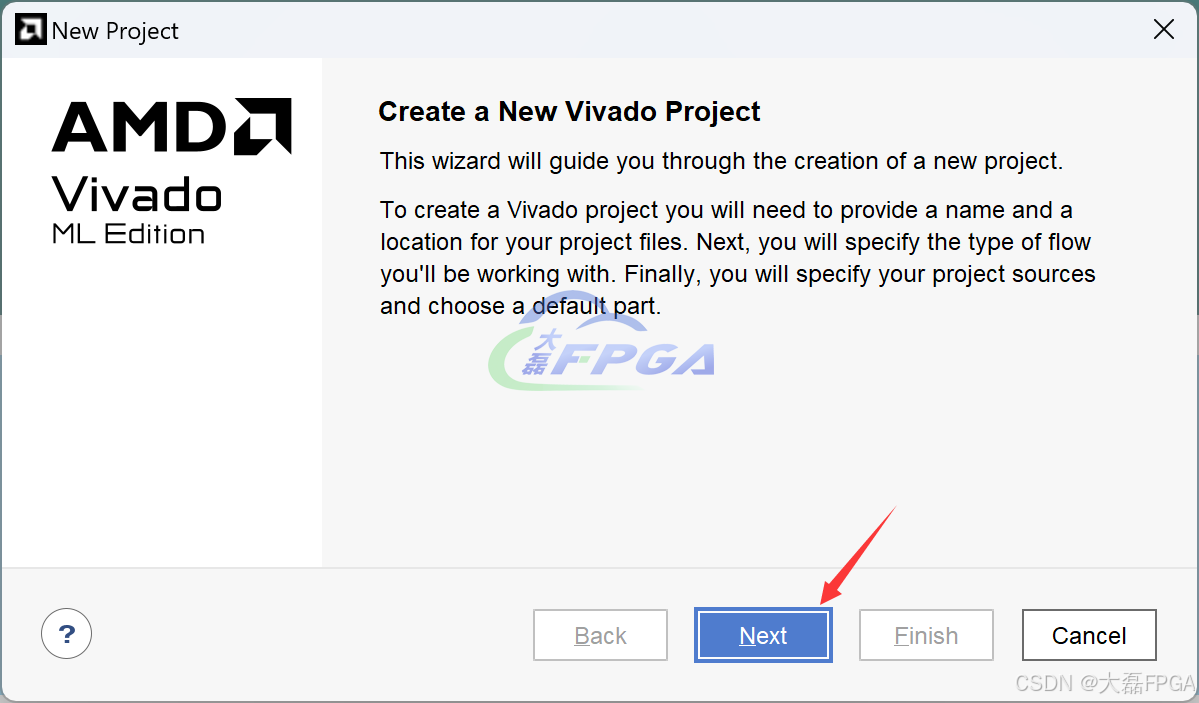

3、弹出新建工程向导,在界面中点击Next:

图 3.1.3 新建工程向导

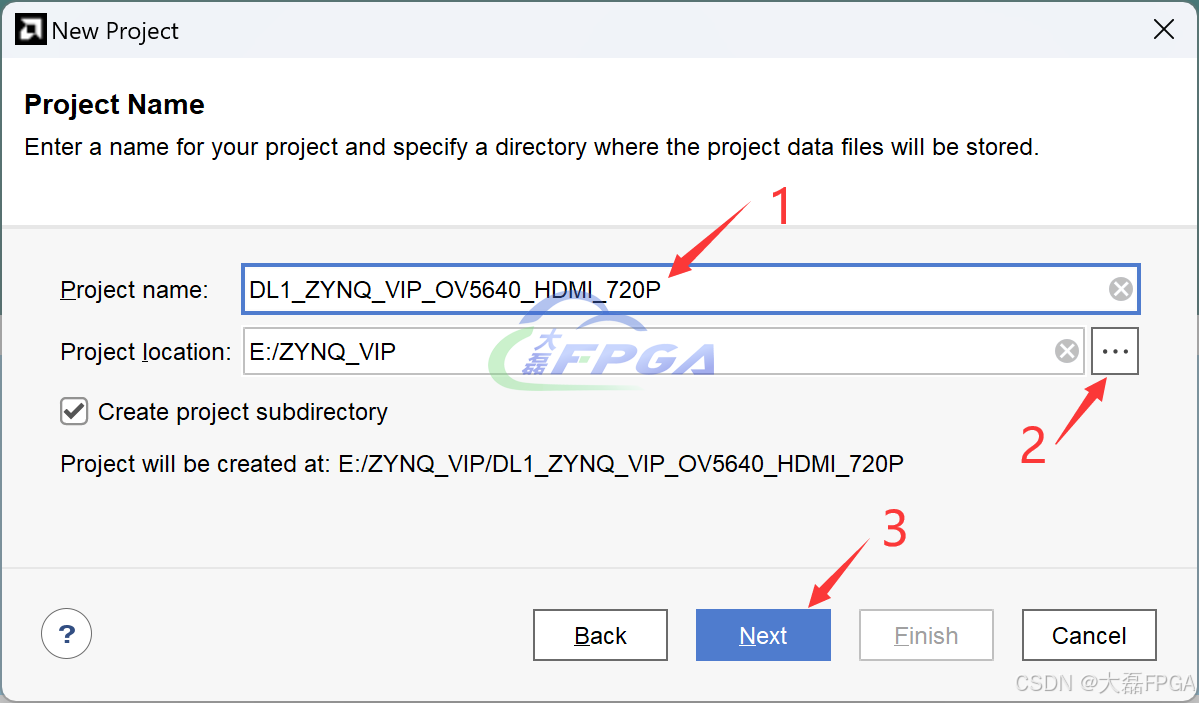

4、输入工程名,并指定工程路径,然后点击Next。注意工程名和路径只能由英文、数字和下划线组成,不能包含中文、空格以及特殊字符:

图 3.1.4 设置工程名和路径

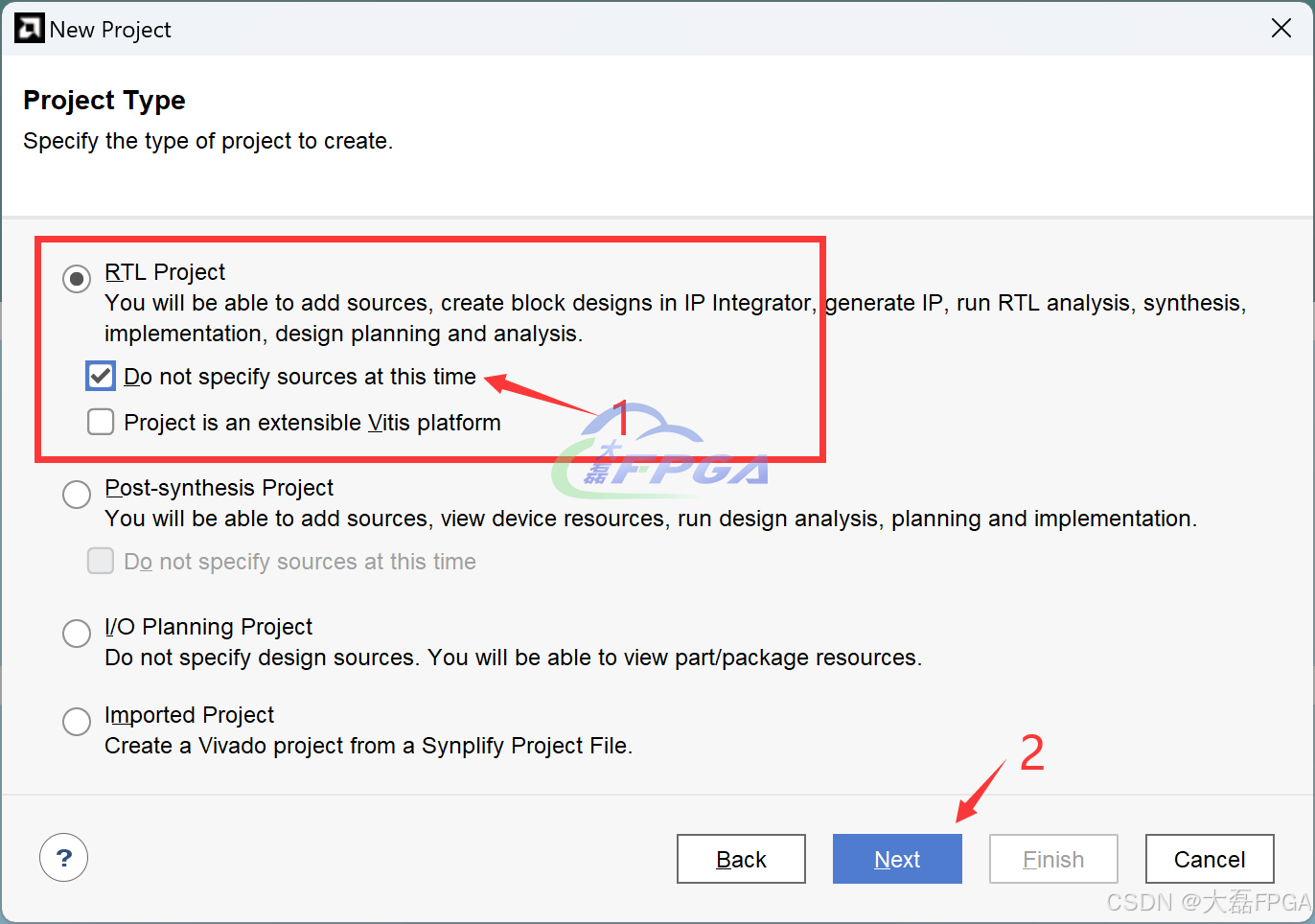

5、保持默认选项RTL Project,然后勾选Do not specify sources at this time(不指定源文件),如下图红色箭头所示。然后点击Next:

图 3.1.5 选择创建RTL工程

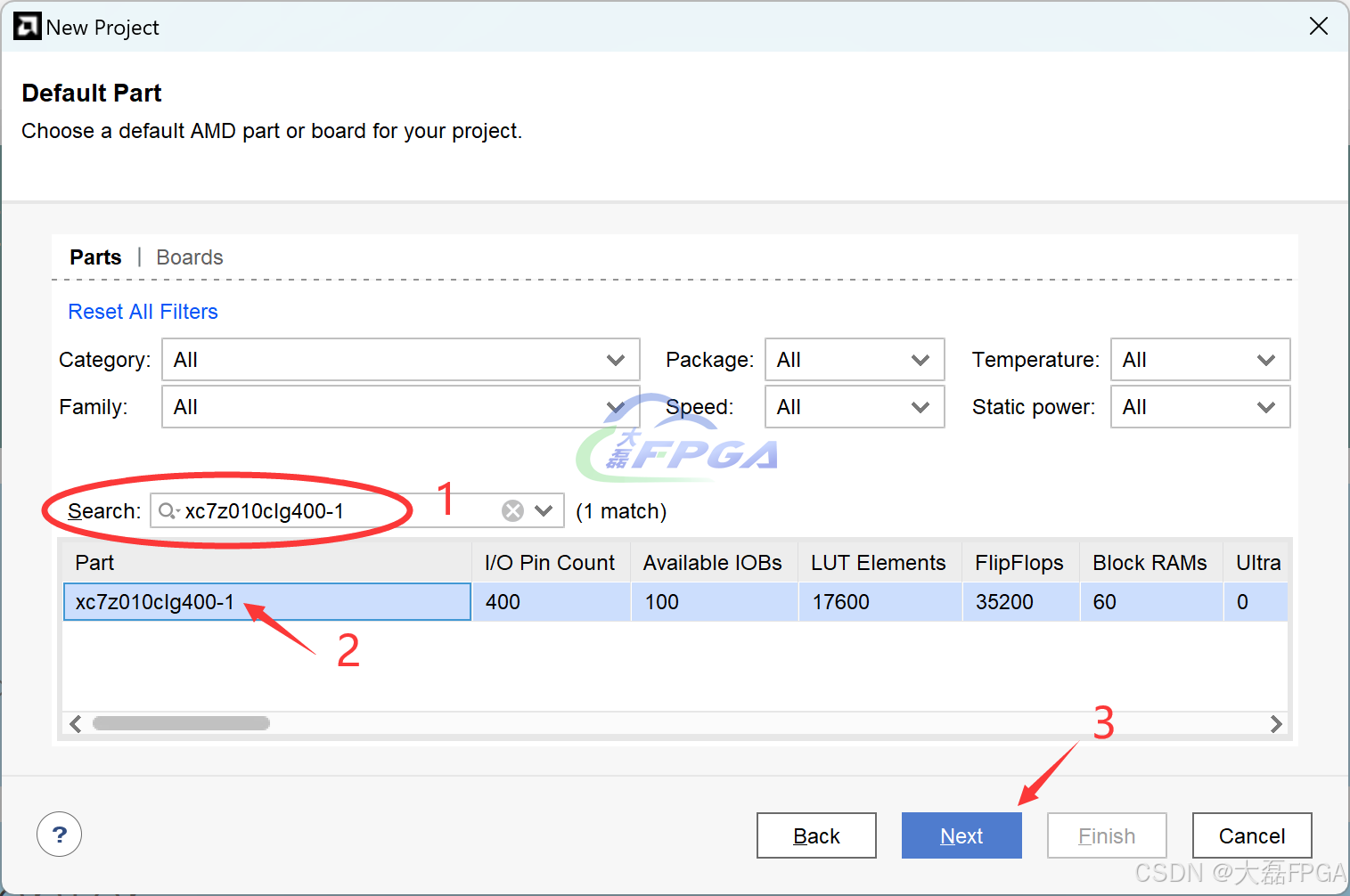

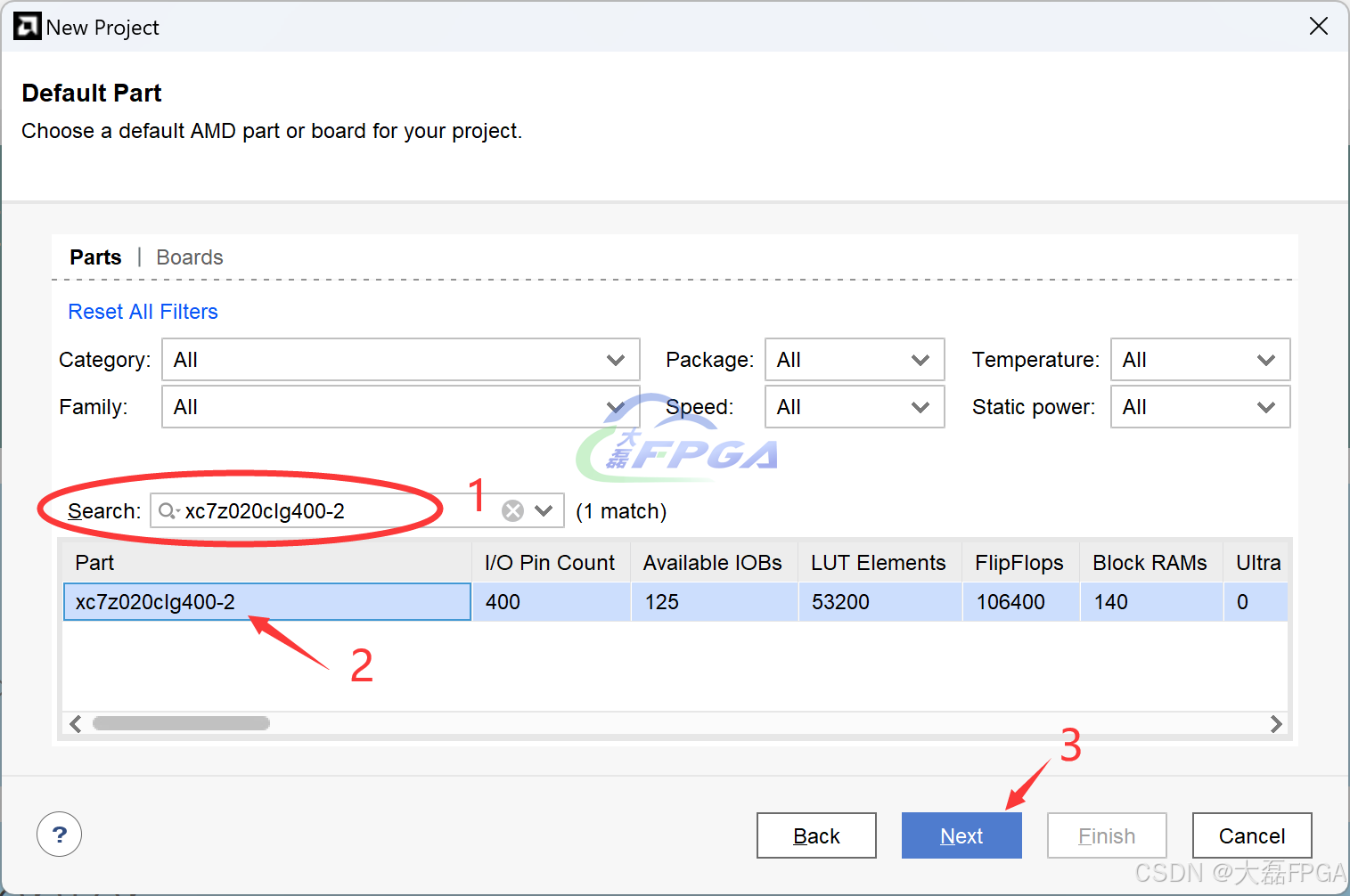

6、在搜索框中输入并查找开发板所使用的ZYNQ器件型号:7010版本输入xc7z010clg400-1,7020版本输入xc7z020clg400-2;然后在器件列表中选中对应型号,点击Next:

图 3.1.6 开发板7010版本器件型号

图 3.1.7 开发板7020版本器件型号

图 3.1.7 开发板7020版本器件型号

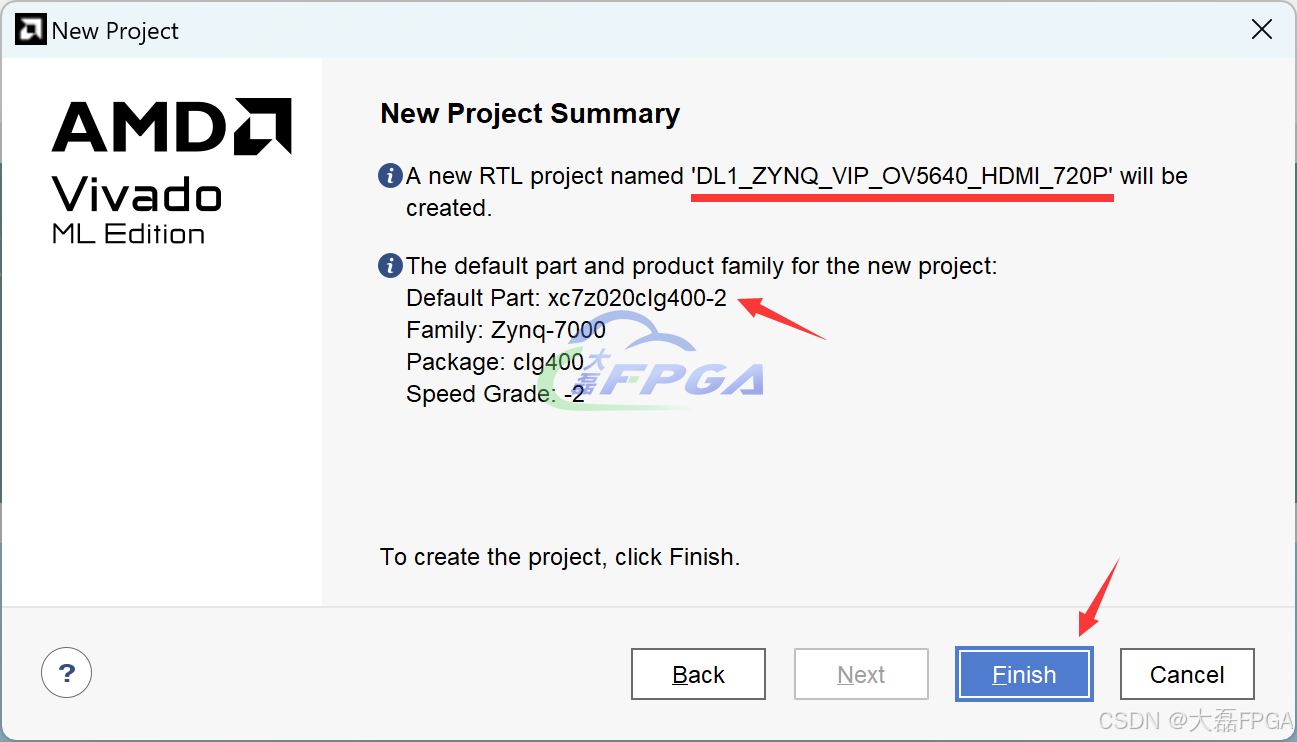

7、在Summary界面确认工程名,以及器件型号(这里以7020版本为例),最后点击Finish完成工程创建:

8、工程创建完成后的界面如下图所示:

3.2创建Block Design

在ZYNQ开发过程中,使用Vivado的模块化设计(Block Design)可以大大简化开发流程,《ZYNQ视频图像处理》中的例程均采用Block Design设计,这也是行业内较为普遍的开发方式。

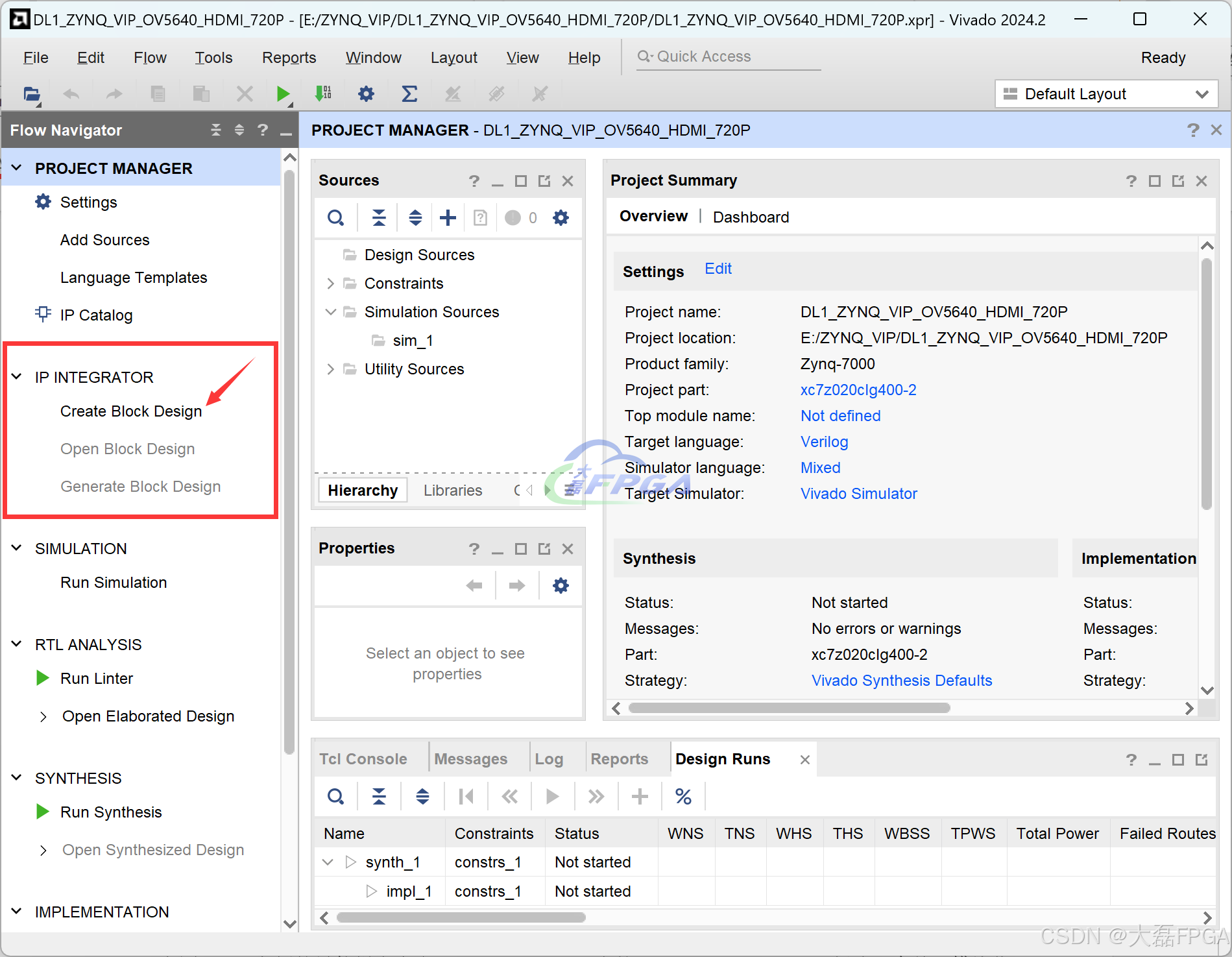

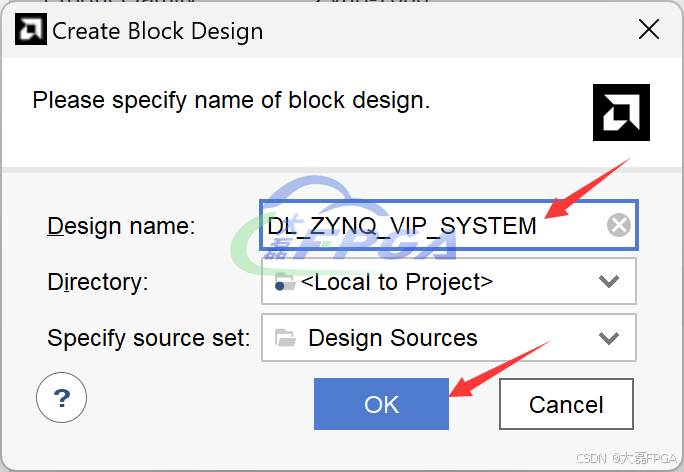

1、在图 3.1.8左侧的导航栏中点击IP INTEGRATOR中的Create Block Design,在弹出的对话框中输入设计名称,创建一个基于模块化设计的ZYNQ视频图像处理系统,然后点击OK:

图 3.2.1 创建ZYNQ视频图像处理系统

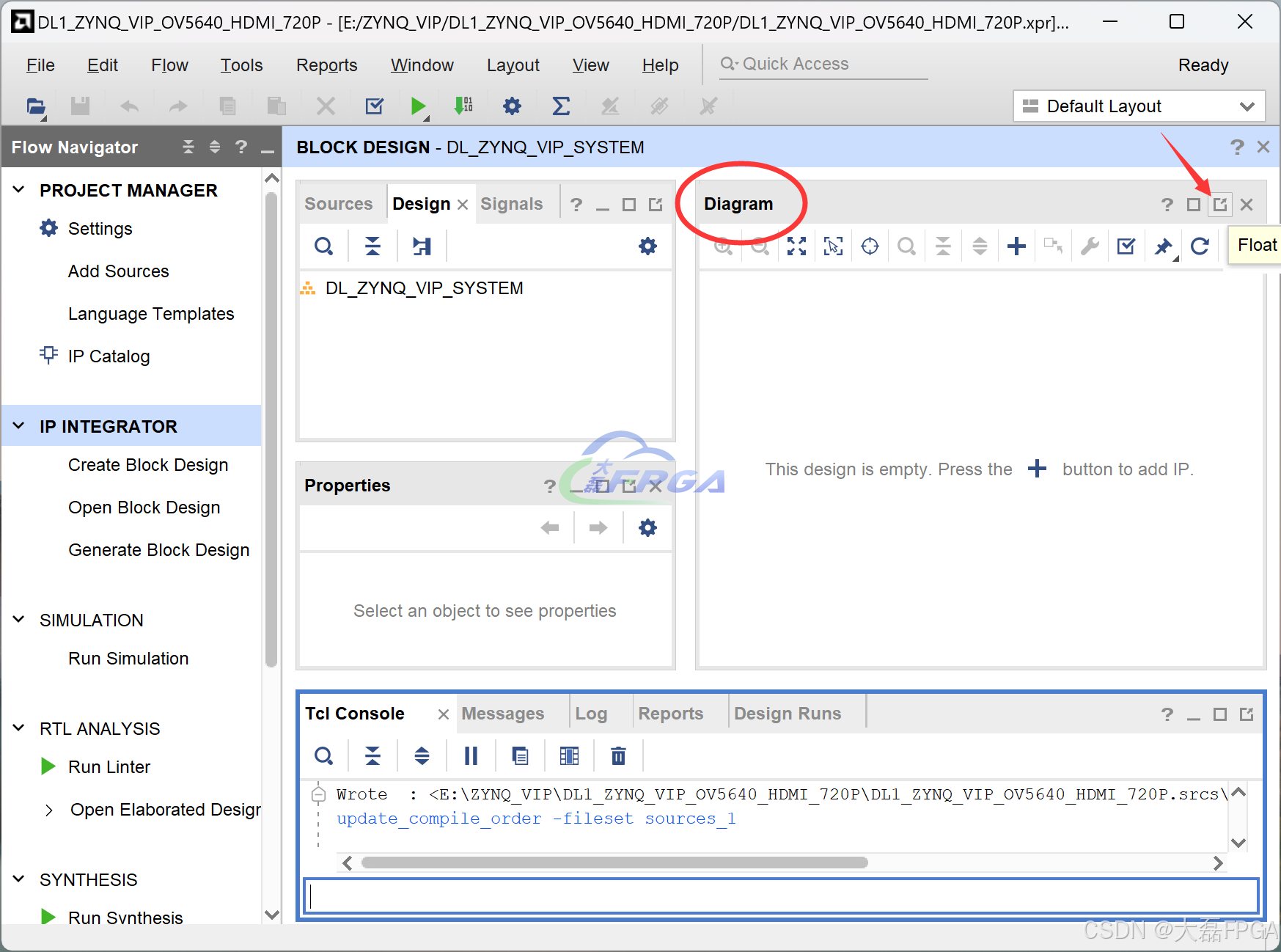

2、Block Design创建完成后的界面如下图所示,在Diagram窗口的右上角点击Float按钮(由红色箭头所指示)可以将其分离出来,方便在Diagram窗口中进行后续设计:

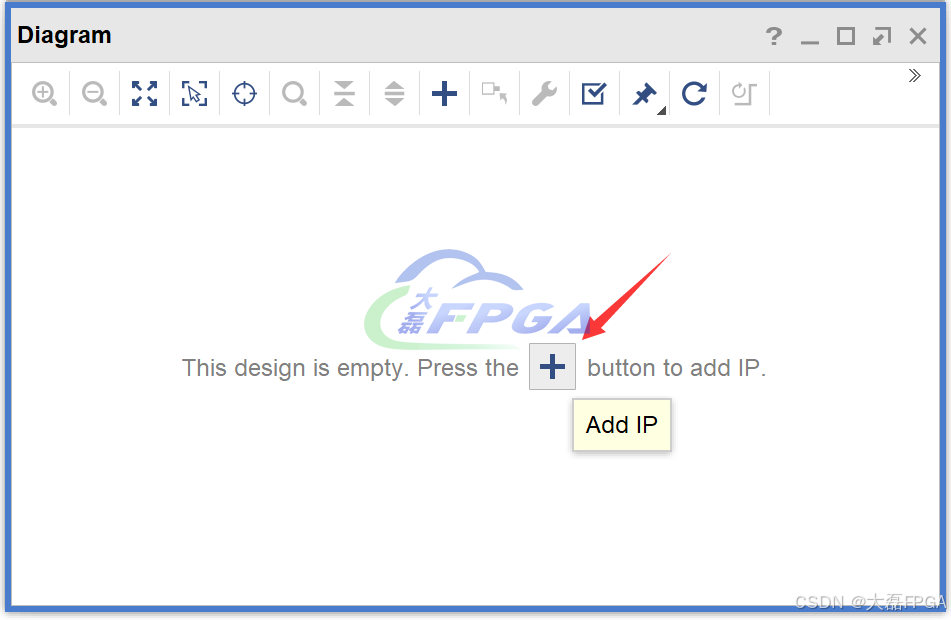

3、Vivado的Block Design采用了图形化的设计方式,此时的Diagram窗口就像是一个空白的画布,我们可以在上面添加各种功能模块(如IP核)。首先点击Diagram窗口中心的加号来添加ZYNQ处理系统:

图 3.2.2 开始在Block Design中添加IP

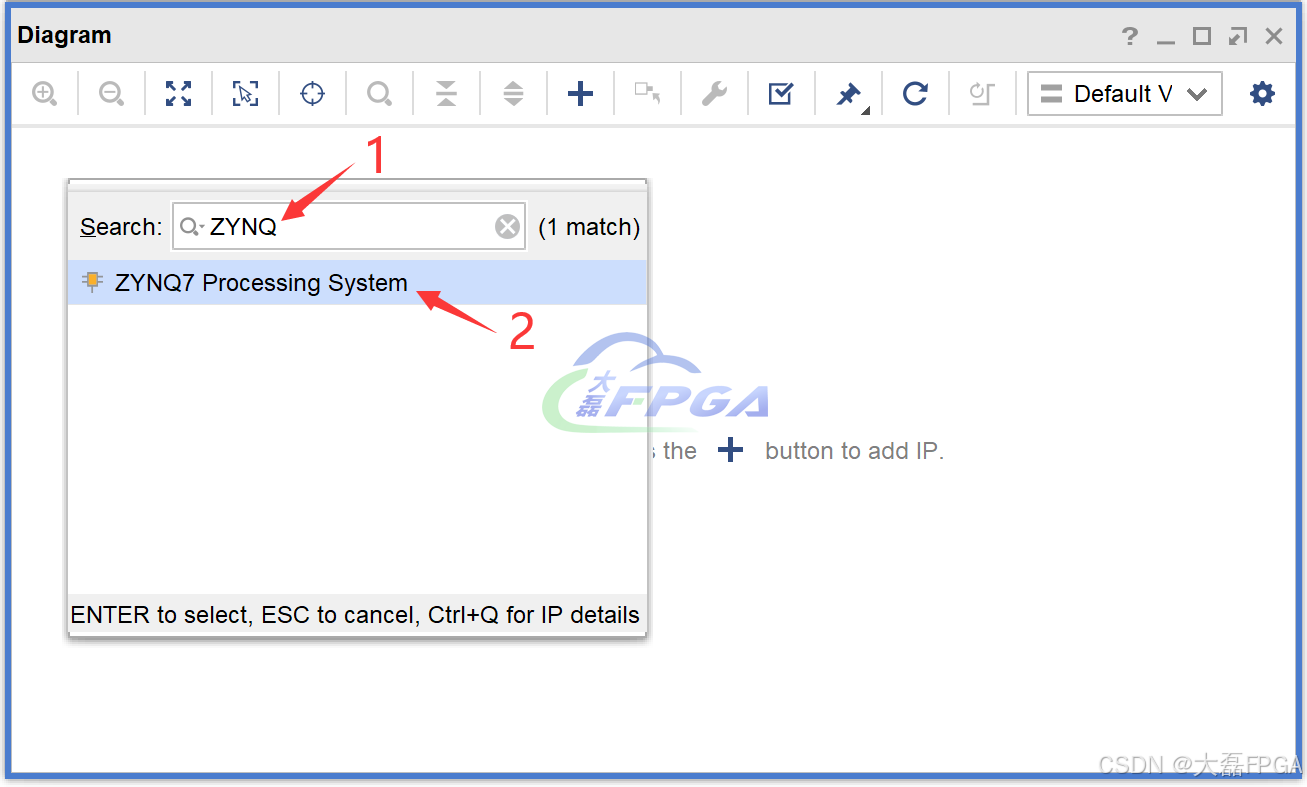

4、在弹出的IP列表中输入ZYNQ,在搜索结果中双击ZYNQ7 Processing System,将其添加到Diagram窗口中:

图 3.2.3 搜索并添加ZYNQ处理系统

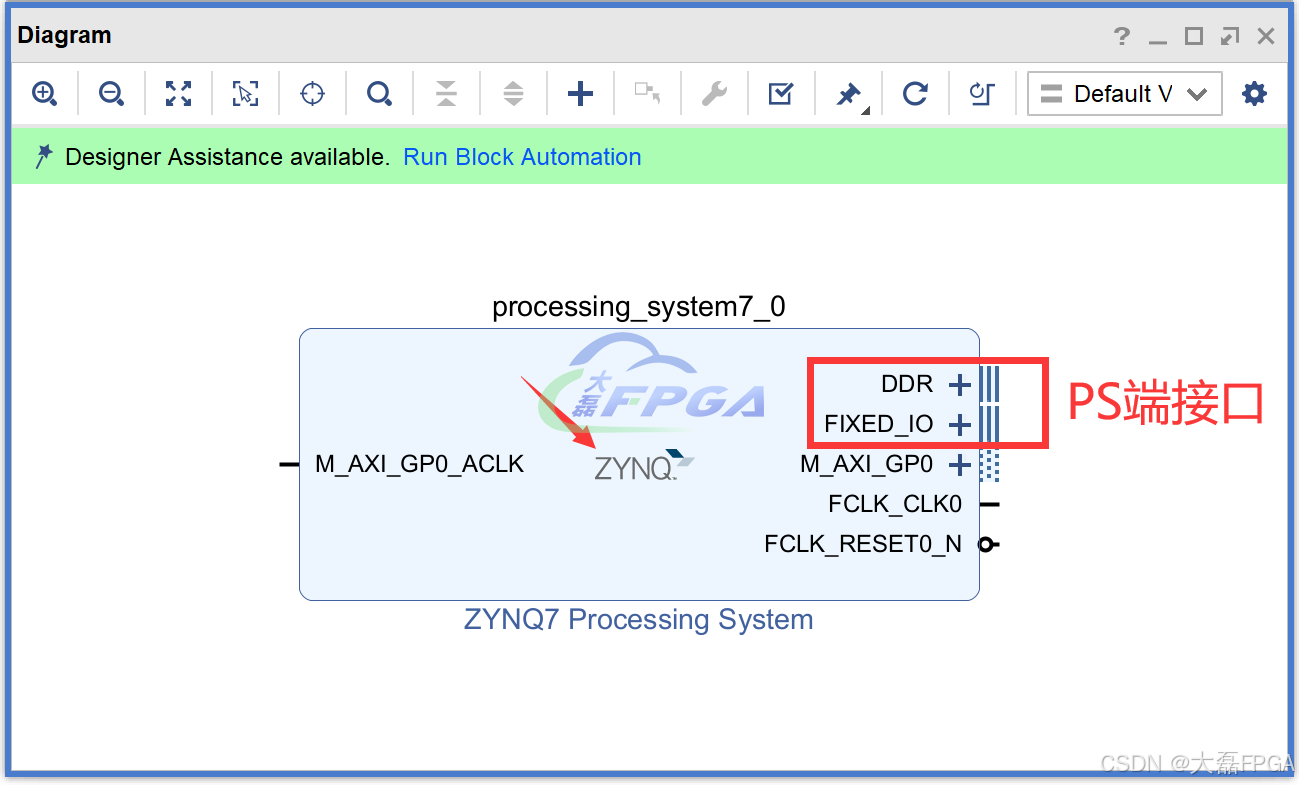

5、添加的ZYNQ处理系统(PS)如下图所示:

此时我们简单地看一下ZYNQ处理系统的接口信号,可以分成两大类:

第一类是PS端的接口,包括DDR接口,以及PS端的FIXED_IO(固有IO,如时钟、复位等),它们最终会连接到ZYNQ芯片PS端的引脚上;

第二类是用于PS与PL连接的接口信号,如GP接口(M_AXI_GP0)及其时钟(M_AXI_GP0_ACLK),以及PS输出给PL的时钟(FCLK_CLK0)和复位(FCLK_RESET0_N)信号。

3.3 配置ZYNQ PS端

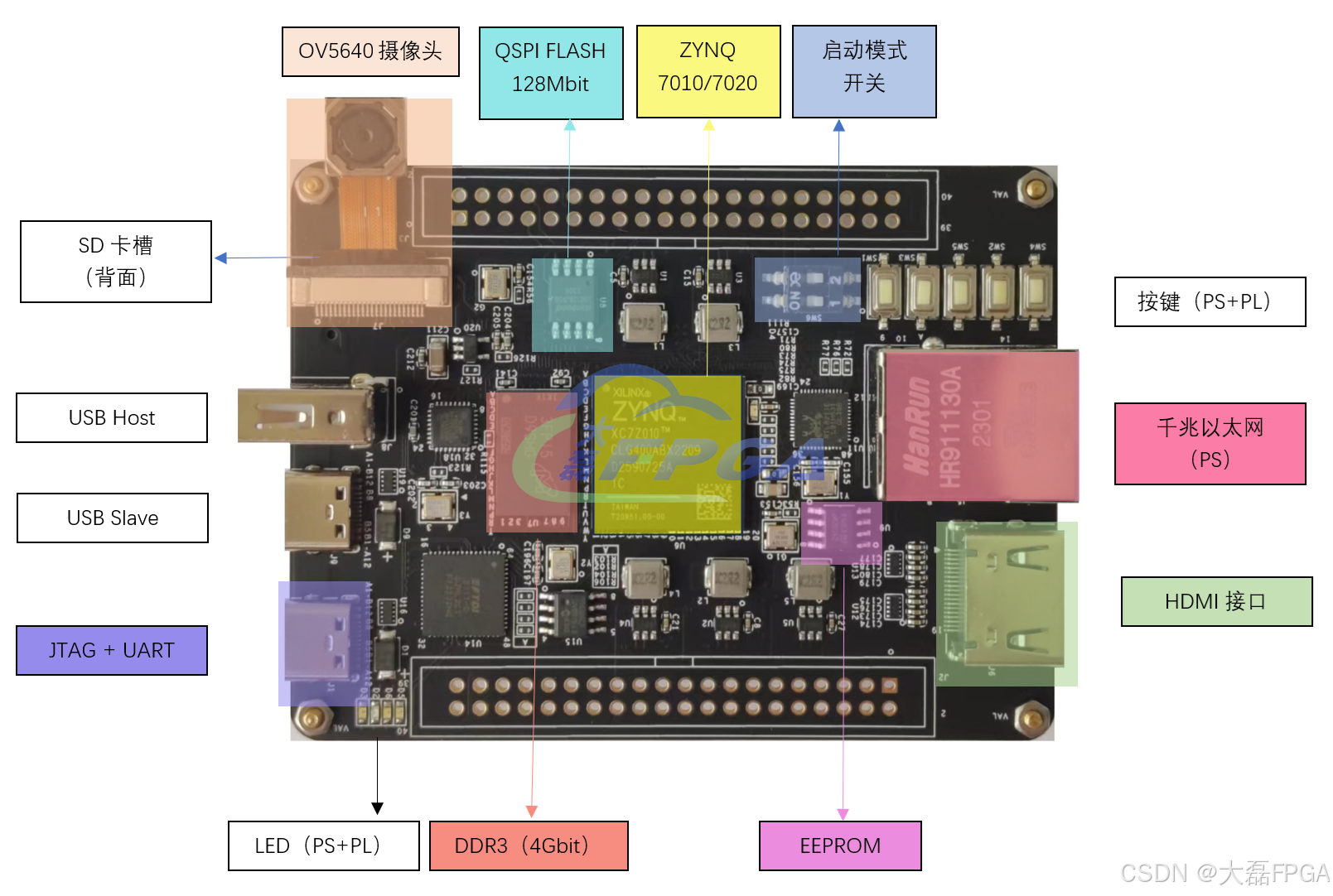

ZYNQ的PS端需要根据开发板的原理图来进行配置,如DDR3控制器,以及UART串口、SD卡等外设。这里我们以【征服者】ZYNQ 7010/7020图像处理板为例进行演示,其外设如下图所示:

图 3.3.1 征服者ZYNQ 7010/7020图像处理板

【征服者】是专门为《ZYNQ视频图像处理》教程设计的开发板:不需要额外购买下载器,不需要电源适配器,一根Type C线即可进行ZYNQ开发;购买开发板还赠送OV5640摄像头、SD卡和读卡器。征服者7010版本价格为498元,7020版本价格为698元,有需要的同学可以搜索淘宝店铺:大磊FPGA。

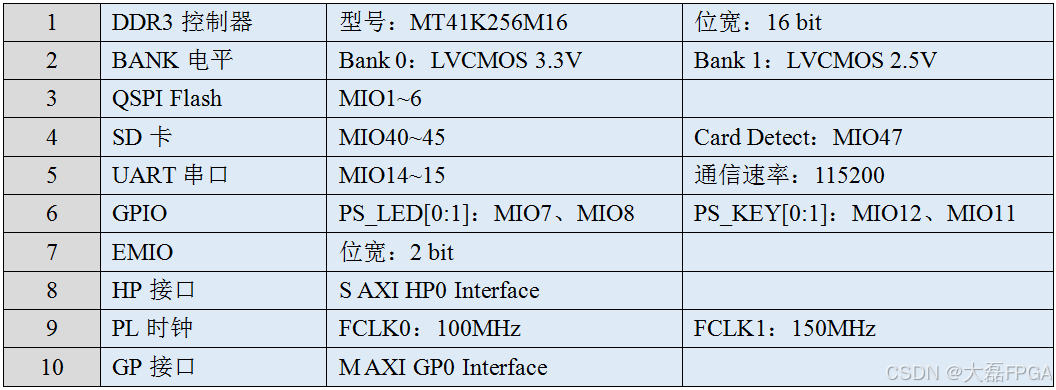

在ZYNQ视频图像处理系统中,PS端需要配置的内容如下表所示:

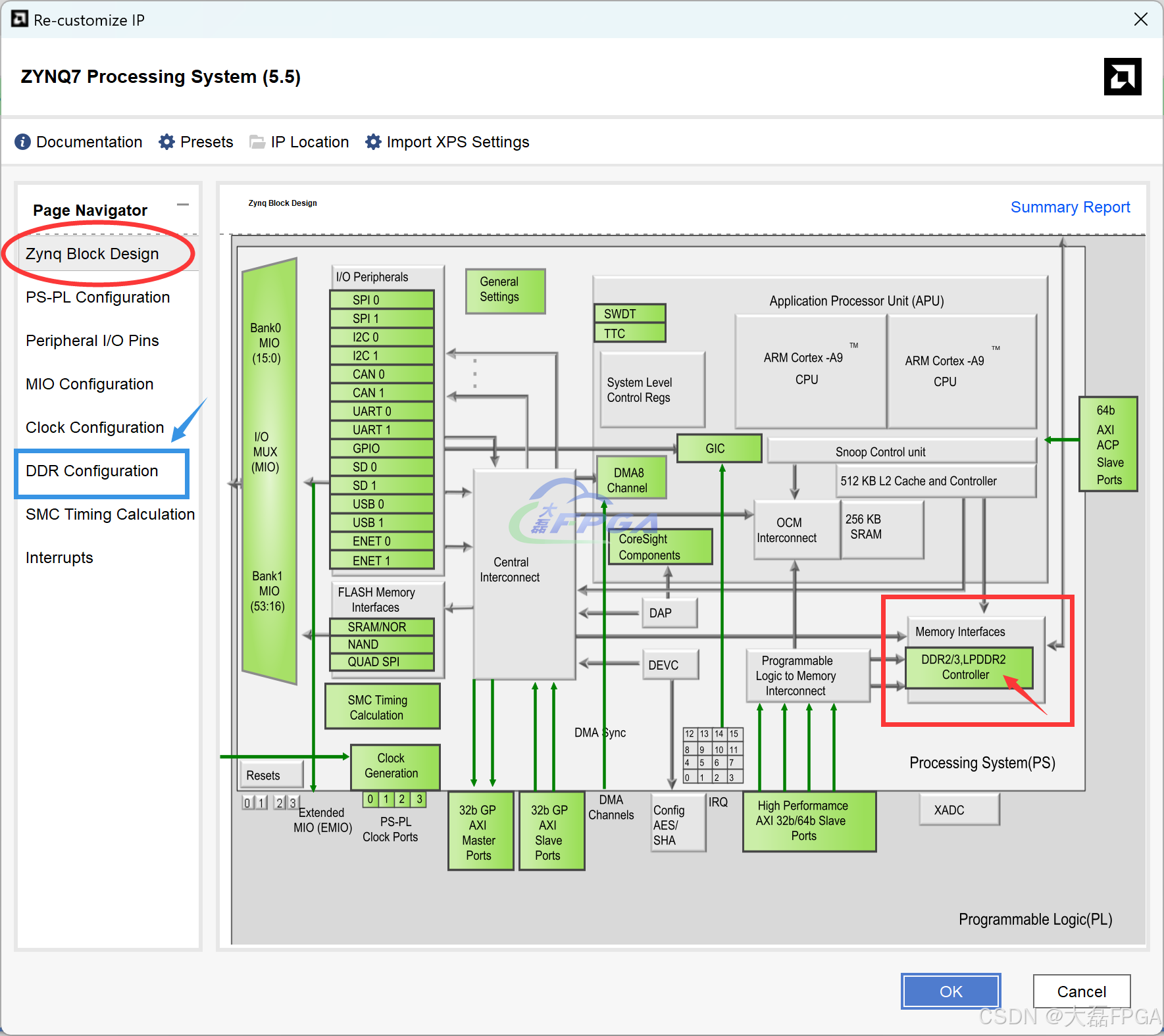

1、配置DDR3。双击图 3.2.4中的ZYNQ处理系统,可以打开ZYNQ PS端的配置界面。在Zynq Block Design页面中找到存储器接口(Memory Interface)部分,在DDR控制器(DDR2/3, LPDDR2 Controller)上单击进入DDR配置界面。如下图红色箭头所指示:

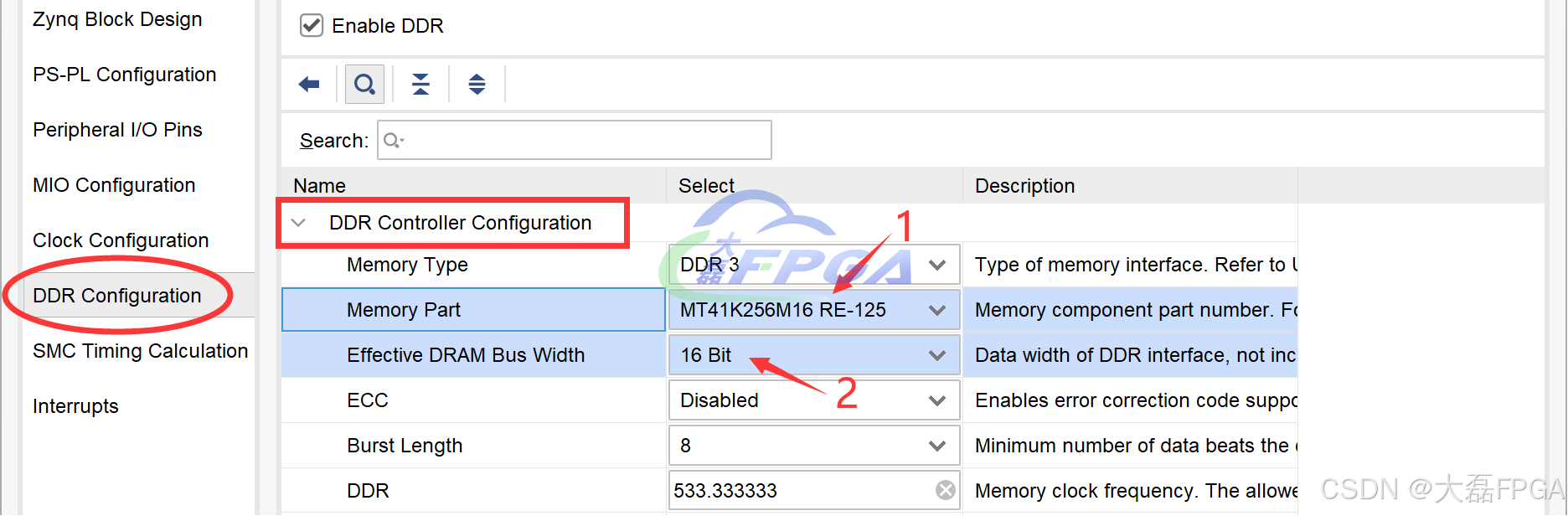

在图 3.3.2左侧的页面导航栏中,也可以通过直接点击蓝色方框中的DDR Configuration打开DDR的配置界面。选择DDR3器件型号为MT41K256M16 RE-125,总线位宽为16 Bit,如下图所示:

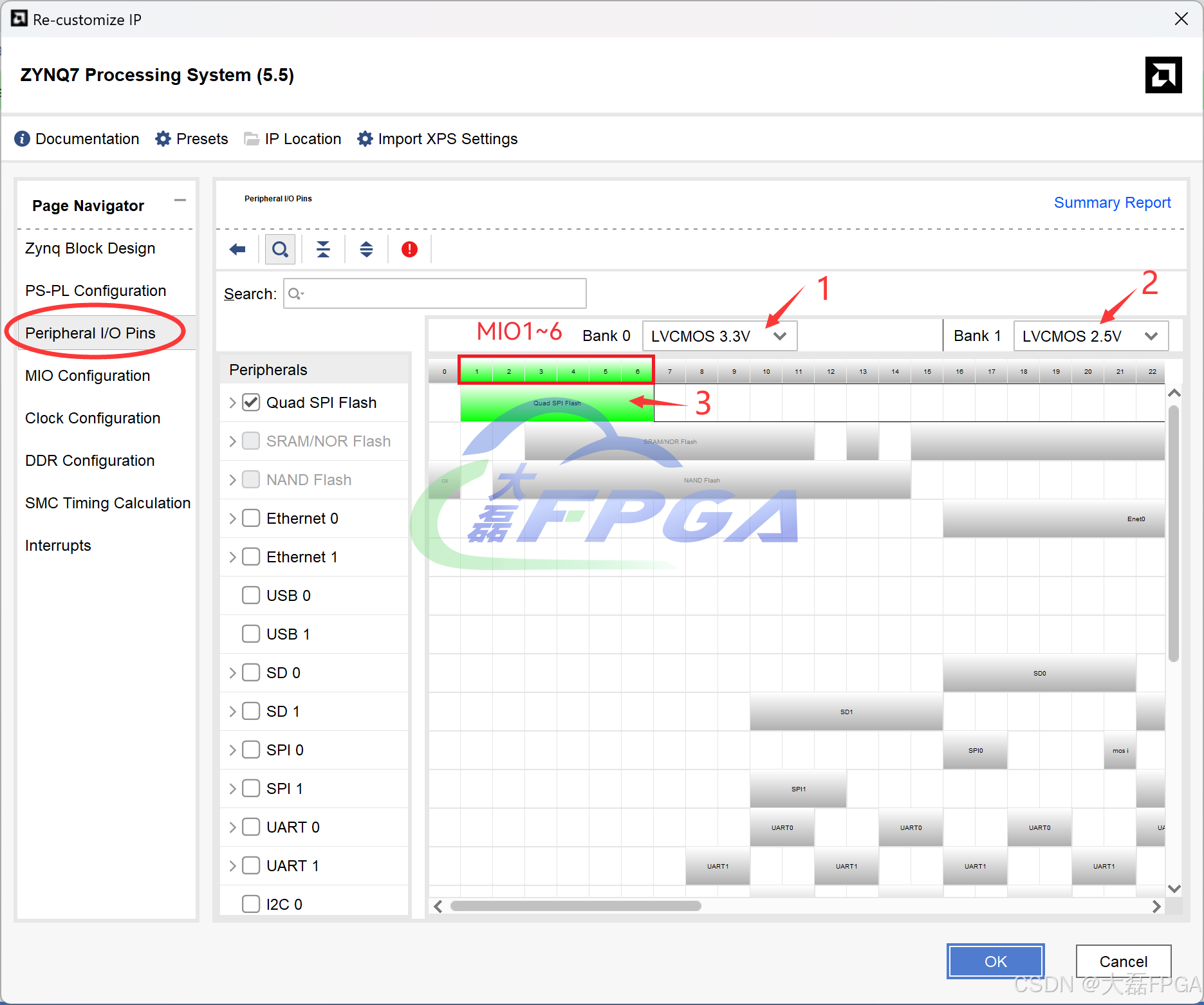

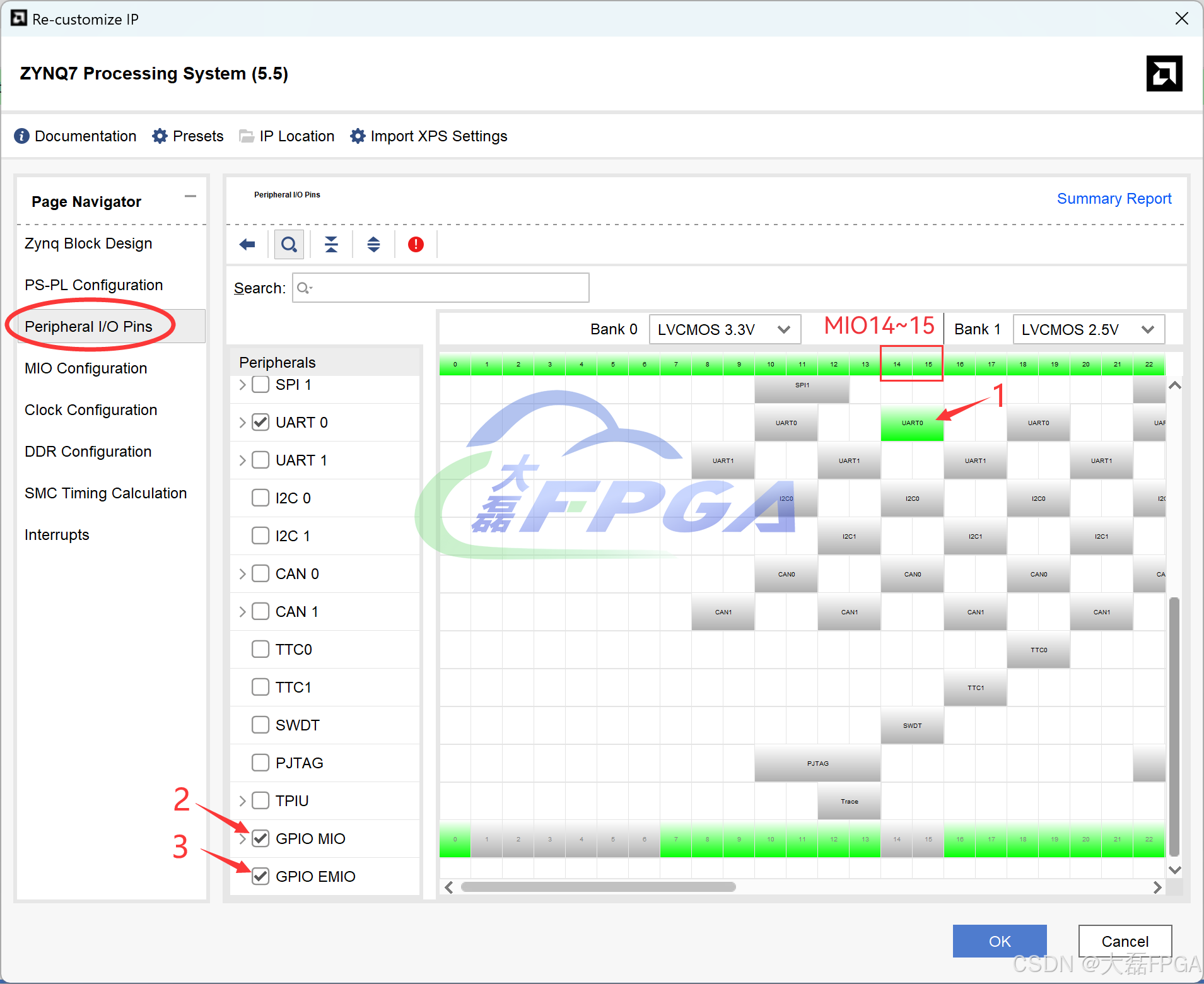

2、配置BANK电平。在左侧的页面导航栏中选中Peripheral I/O Pins页面,然后在右侧选择Bank 0的电平为LVCMOS 3.3V,Bank 1的电平为LVCMOS 2.5V,如下图红色箭头1/2所示:

3、配置QSPI Flash。在图 3.3.4中点击MIO1~6所对应的Quad SPI Flash外设,变成绿色表示选中,如上图红色箭头3所指示。

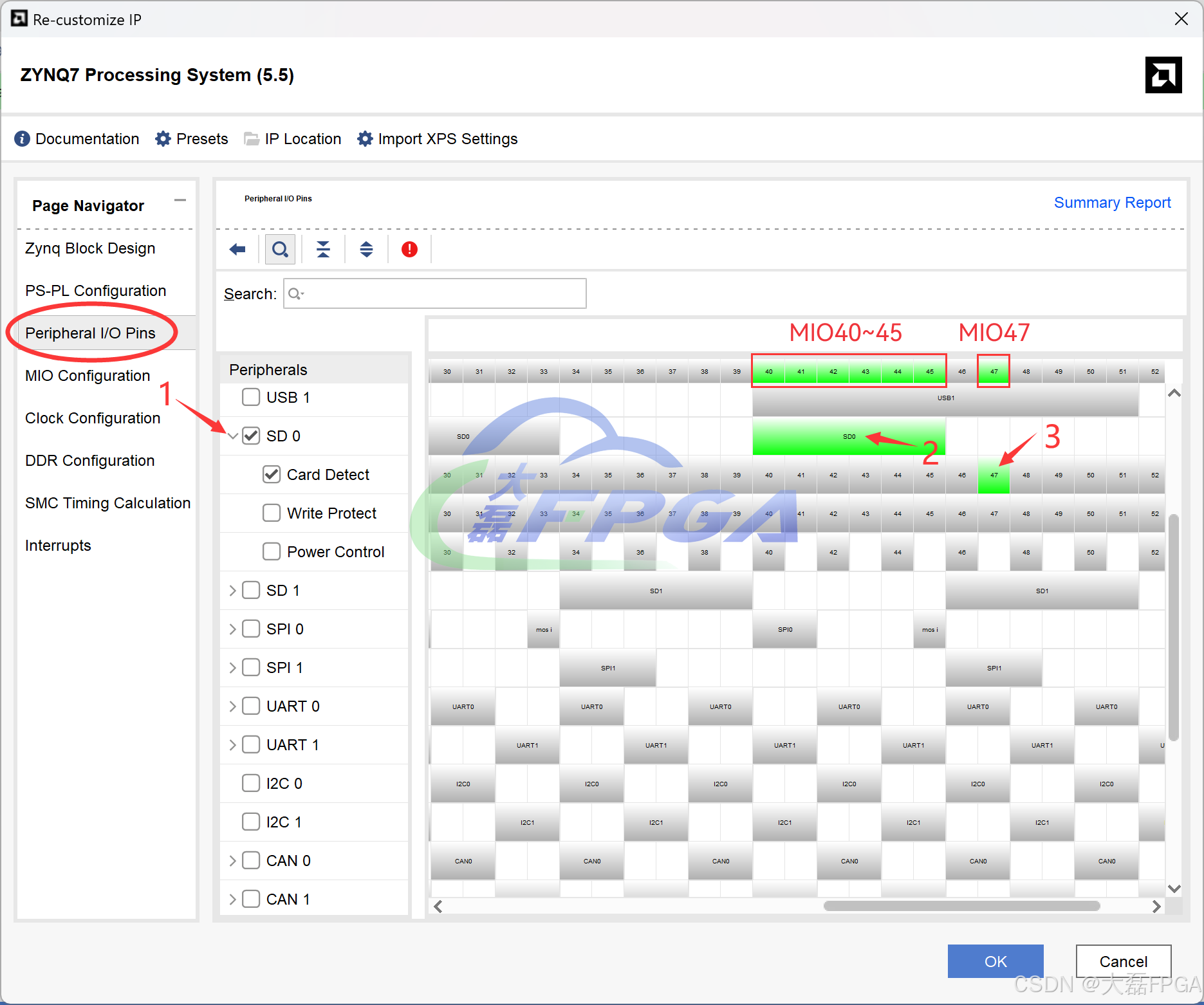

4、配置SD卡。同样是在Peripheral I/O Pins页面,展开Peripherals一栏中的SD 0,然后在右侧找到MIO40~45所对应的SD0外设并选中,另外还要选中MIO47所对应的Card Detect,如下图所示:

图 3.3.5 配置SD卡及Card Detect

5、配置UART串口。在Peripheral I/O Pins页面,选中MIO14~15所对应的UART0外设,如下图红色箭头1所指示:

6、配置GPIO和EMIO。在Peripheral I/O Pins页面,勾选Peripherals一栏中的GPIO MIO和GPIO EMIO,如图 3.3.6中红色箭头2/3所指示。

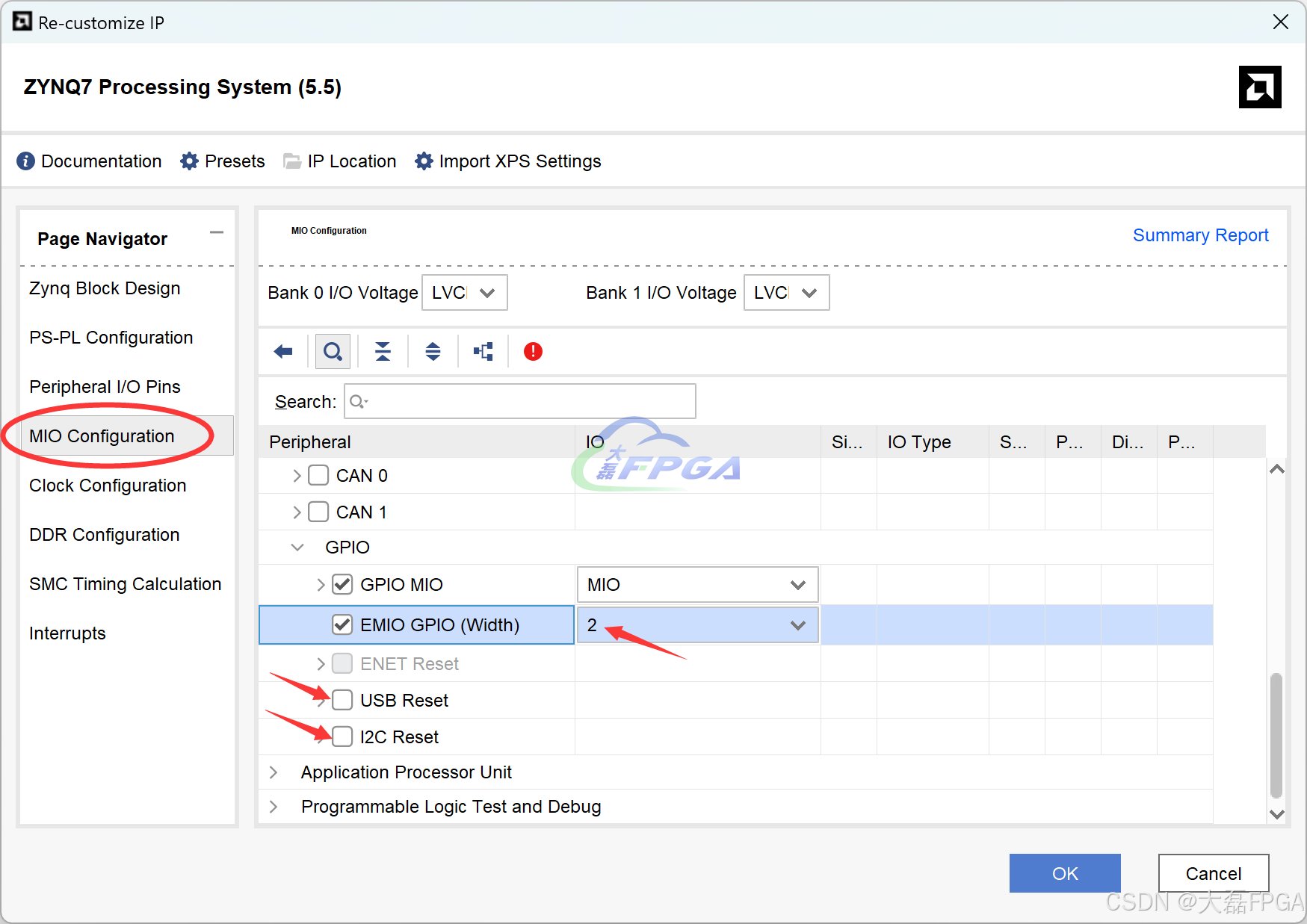

7、配置EMIO位宽。在页面导航栏中选中MIO Configuration页面,然后在右侧找到I/O Peripherals中的GPIO外设并展开,将EMIO GPIO的位宽设置为2,同时取消勾选USB Reset和I2C Reset,如下图所示:

图 3.3.7 设置EMIO位宽

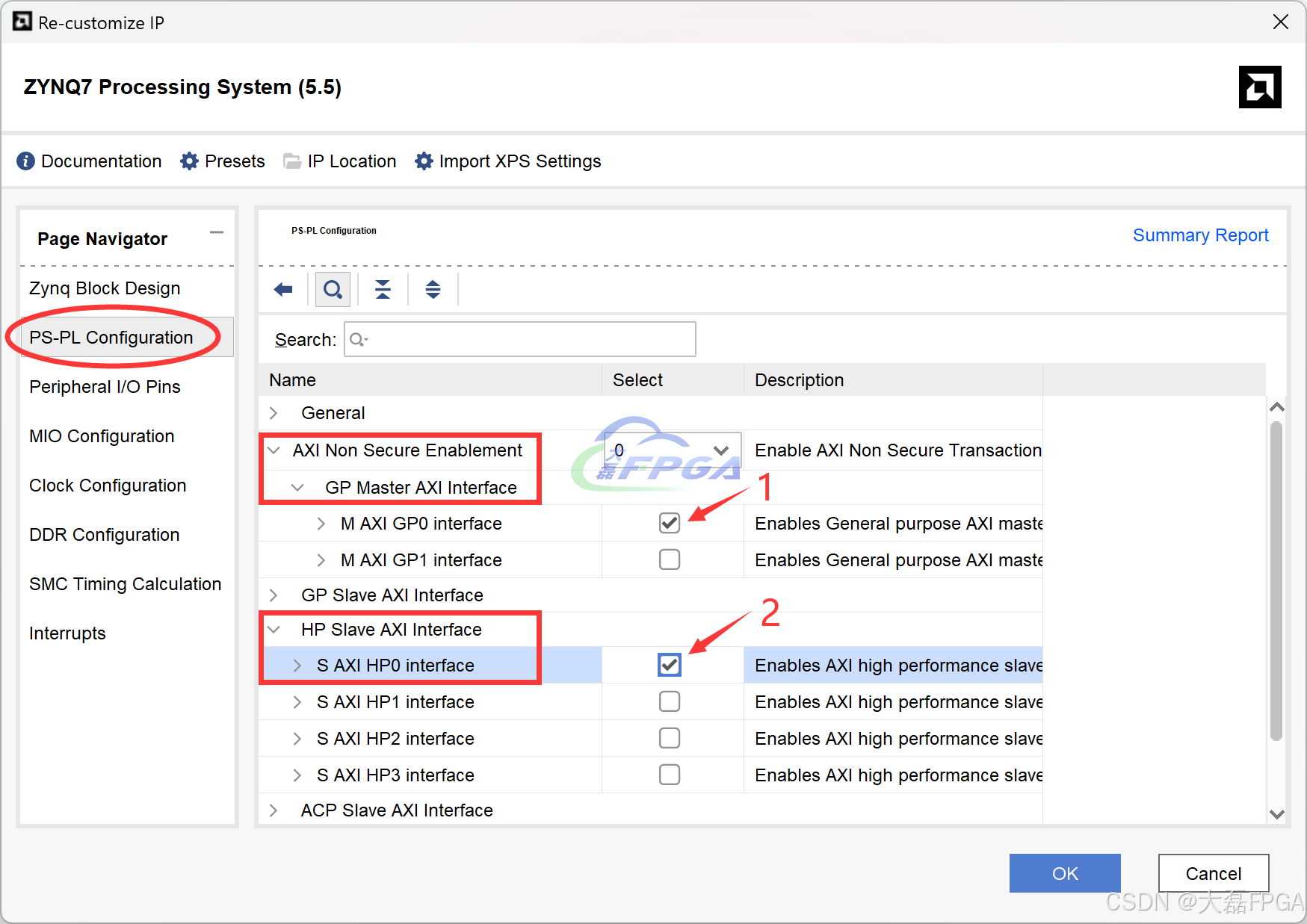

8、配置HP接口。在页面导航栏选择PS-PL Configuration页面,然后在右侧展开HP Slave AXI Interface,勾选第一个HP接口——S AXI HP0 Interface,如下图红色箭头2所示:

从图 3.3.8中红色箭头1所指示的位置可以看到,工具已经自动勾选了一个GP主机接口——M AXI GP0 Interface,因此不需要我们再手动配置GP接口。

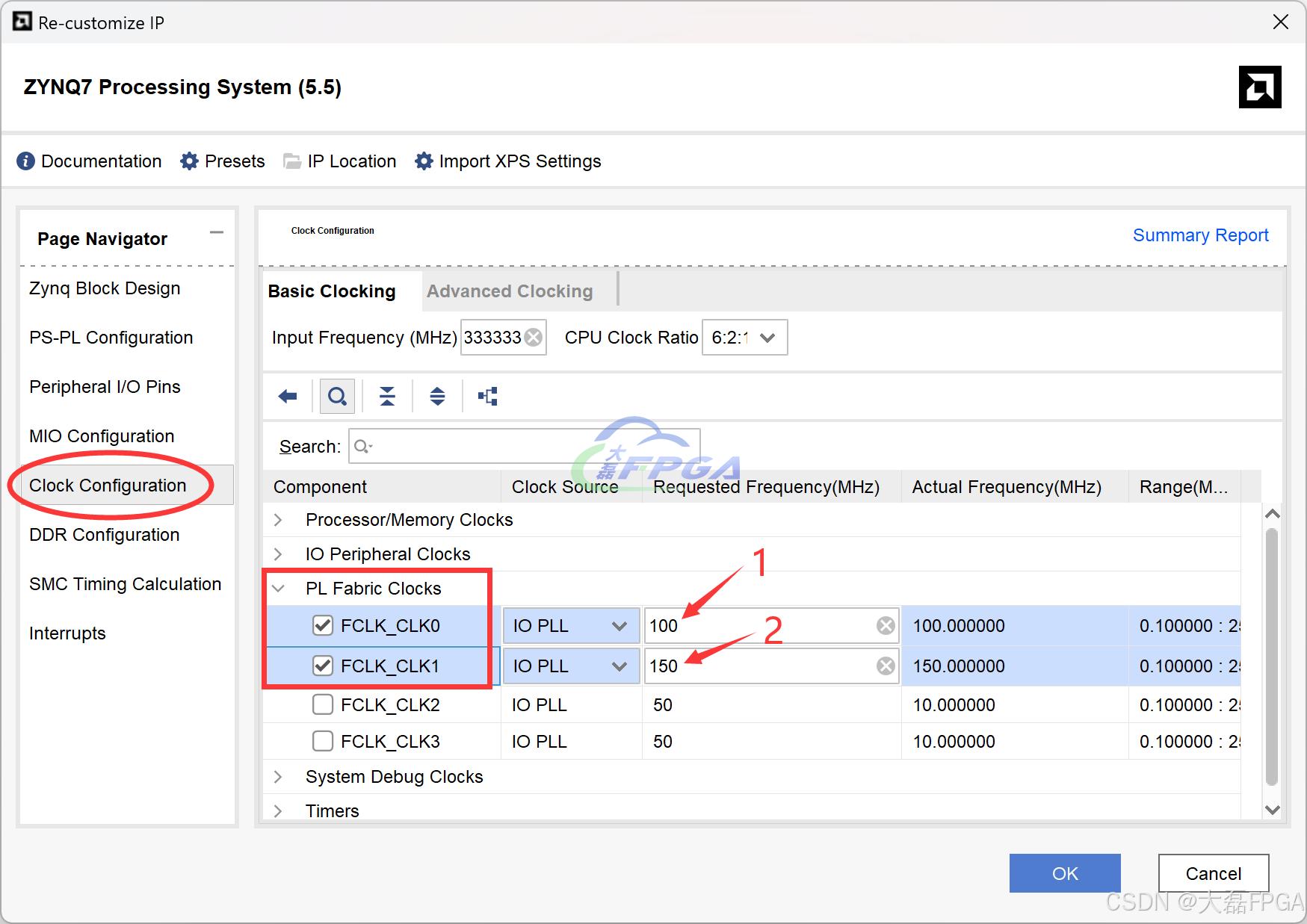

9、配置PL时钟。在页面导航栏选择Clock Configuration页面,然后在右侧展开PL Fabric Clocks,将FCLK_CLK0的频率设置为100MHz;然后再勾选下方的FCLK_CLK1,并将其频率设置为150MHz,如下图所示:

图 3.3.9 配置PL时钟

到这里我们ZYNQ视频图像处理系统的PS端就配置完成了。

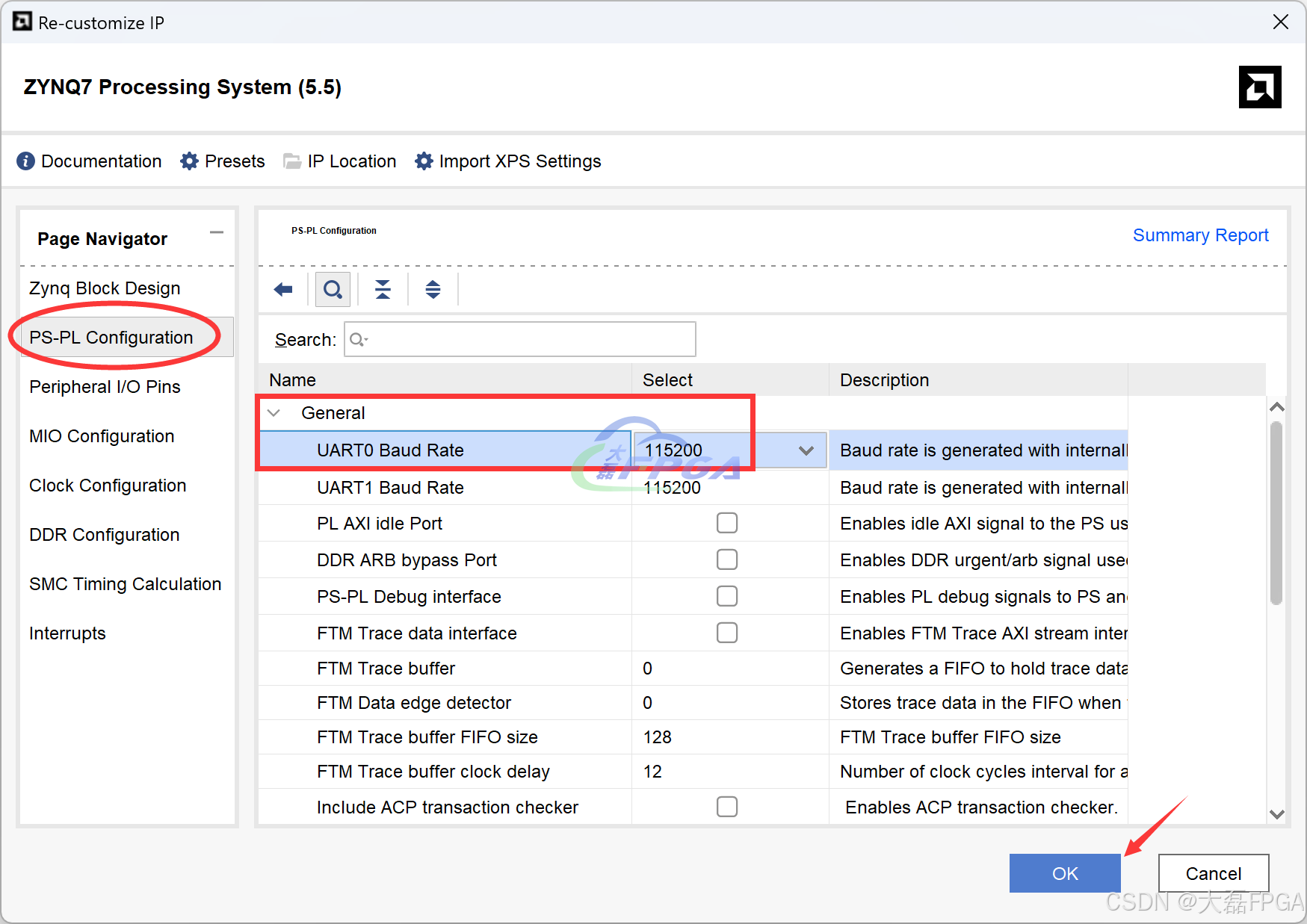

最后再给大家介绍一下如何查看PS端串口通信的速率。在页面导航栏选择PS-PL Configuration页面,然后在右侧展开General,在第一行可以看到UART0的波特率为115200:

大家对照表格 3.3.1检查PS的各项配置,确认无误后点击图 3.3.10右下角的OK完成ZYNQ PS端的配置。最终获得的ZYNQ Processing System模块如下图所示:

图 3.3.11 ZYNQ处理系统配置完成

《ZYNQ视频图像处理》配套的视频教程在B站同步更新,感兴趣的同学可以关注UP主:大磊FPGA

739

739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?