用中规模MSI基本逻辑功能模块 实现4bit的加法器和减法器(要求使用中规模实现):

功能要求:两个4位原码二进制数,在1位控制信号ctr的作用下,当ctr=1时,两个数进

行减法运算,当ctr=0时,两个数进行加法运算,计算结果仍然用原码表示。

任务要求:

(1) 分析题目功能需求进行4bit的加法器和减法器的方案设计(即给出该电路的设计方框图),包括:可能使用的基本逻辑功能模块,以及这些模块的基本连接关系,标出输入输出信号,并描述这些逻辑功能模块是如何工作才能完成该电路的功能。

(2) 完成4bit的加法器和减法器电路的原理设计,即给出具体器件的实际连接图(包括适当地方的基本逻辑门使用),并对设计原理图进行仿真分析。

一、思路与方案:

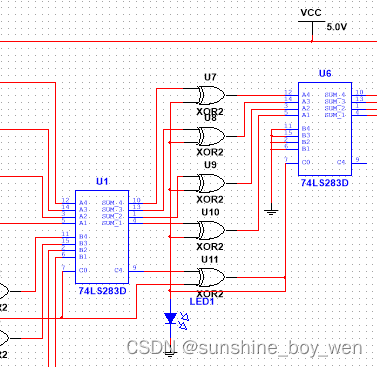

(1)74LS283功能:实现4位加法运算

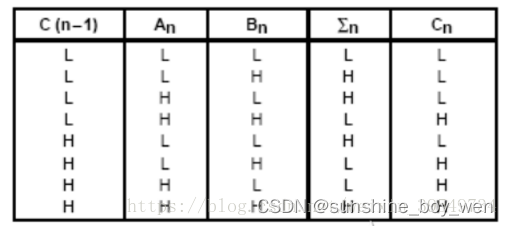

(2)加减法控制

当ctrl=0时,实行加法运算,S=A+B,直接利用4位并行加法器74LS283即可实现;ctrl=1时,实行减法运算,S=A-B,将-B转换成补码再和A相加,而补码是按位取反加1得到的,因此我们将B于ctrl异或,ctrl为0时B与0异或保持原码不变,ctrl为1时变为补码

(3)输出补码转变为原码

使用另外一个74LS283芯片,同样为正数时与0异或,补码等于原码,为负数时与1异或

另外再使用发光二极管,当结果为负数时点亮,作为判断负数的标志,方便读数

(4)通过七段译码器显示

由于大于9的数显示器是无法直接显示的,我们用两个显示器将计算结果用十进制展示出来。

个位数字利用另一块74LS283,将结果加上0110,再接入七段译码器得到

十位数字:当sum_4sum_3=1或者sum_4sum_2=1时,十位数字为1,否则为0

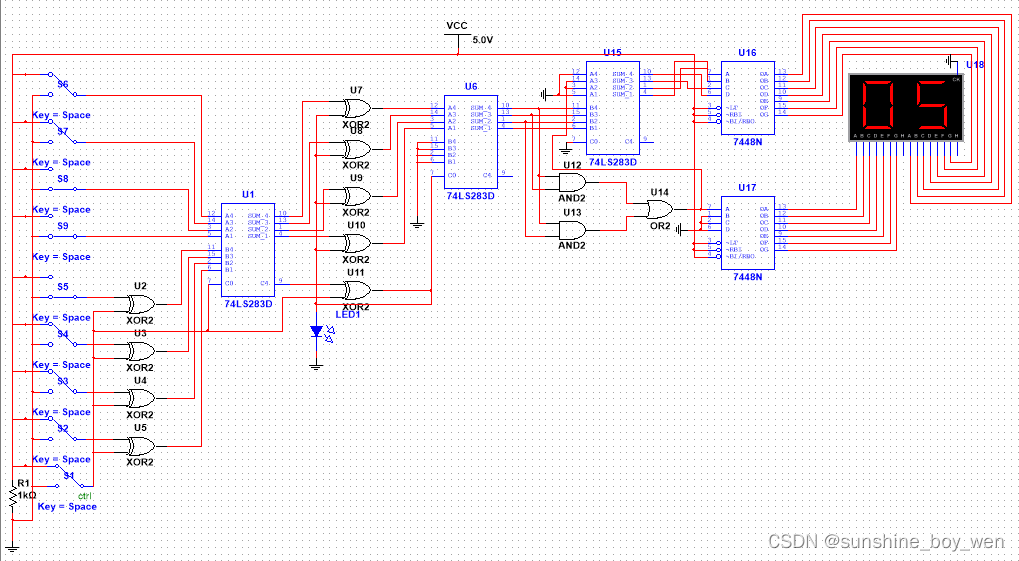

二、电路图连接:

三、仿真验证:

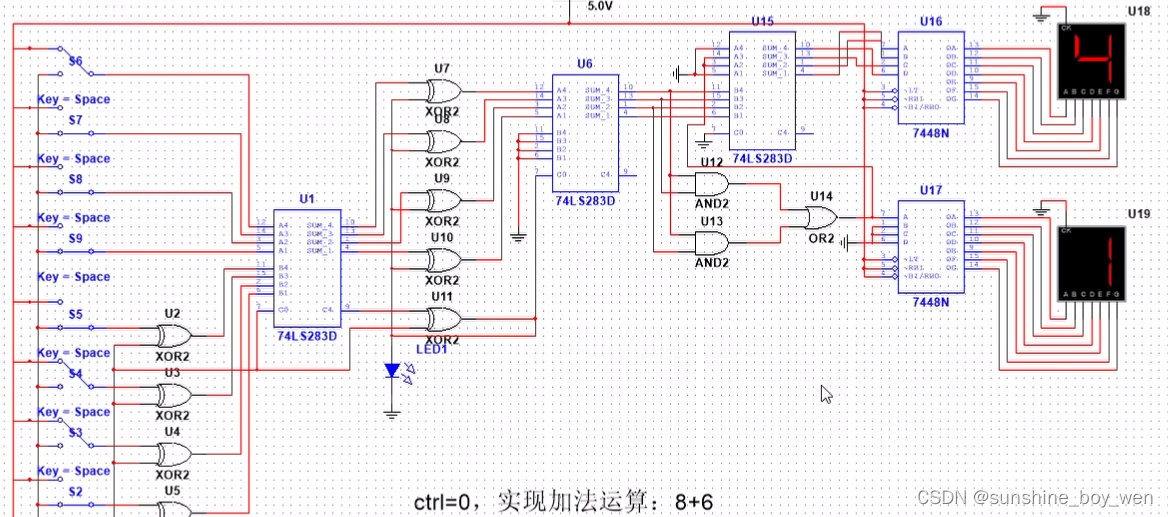

(1)加法运算(ctrl=0)

8+6=14

(2)减法运算(ctrl=1)

12-7=5

2600

2600

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?