[SystemVerilog语法拾遗] ===和!==运算符使用注意事项

引言

我们在仿真时,尤其是后仿时芯片的输出在reset之前或者在掉电后有时候会处在X态,而我们在写bfm的时候,尤其是跟数字芯片有交互的analog_bfm的时候经常会用到数字芯片的输出来产生相应的反馈信号给到数字输入。比如说,模拟芯片的pll振荡器和ldo控制逻辑的开关用到了数字信号输出的enable信号,我们在进行单独的数字芯片仿真的时候需要把pll和ldo的模拟电路用模型来替换,那么就需要通过这个enable信号来产生响应的模拟输出给到数字芯片的输入,而我们在写这部分模拟bfm的时候就需要判定数字输出的enable的值,而enable值可能出现x态、0和1三种结果,那么就需要用到运算符=和!=,本文对这两个运算符的概念以及注意事项进行简单的介绍。

==/!和=/!==的区别

按照sv标准的解释,==和!用于两值运算,即操作数不能包含x和z,否则返回的结果就是个不定态x或者z。而=/!==属于四值运算符,它会严格比对操作数的每一位,并且0、1、x、z被认为是不相等的,返回值只会是0和1这两个确定值,以上便是两类操作符的主要区别。

注意事项

由于===/!==操作符会比对操作数的每一bit,所以我们在使用缺省位宽的时候就不能像两值运算时随意,比如说数字芯片输出的位宽是2位(信号为enable),那么掉电时或者reset前输出的结果就是2’bxx,如果我们判断表达式写成如下:

enable === 'bx

那么返回值就是False(0),必须写全位宽如下:

enable === 2’bxx

因为缺省位宽时sv会自动补齐到32位,所以相当于执行的是

enable === 32’bxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

而enable的高位则用0来补上,自然两者就不相等了。

而我们在做两值运算的时候则不存在这种问题,当enable为2’b01的时候以下两种写法结果返回的都是True(1)

a === 'b1

a === 2’b1

代码实例

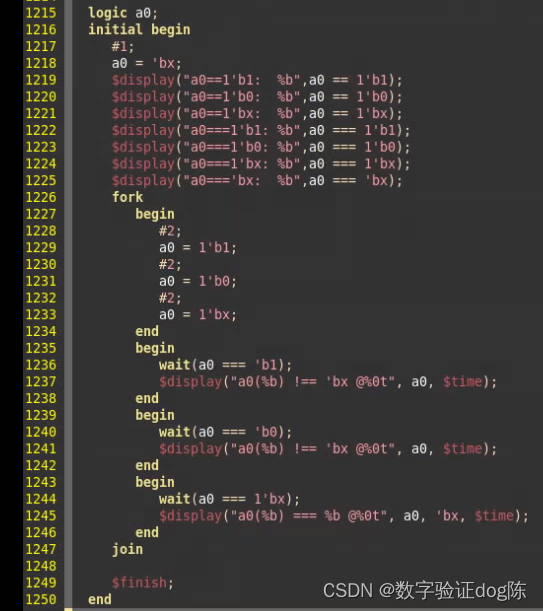

下面我们以一段代码实例和仿真结果来印证我们上面的结论,代码如下图所示

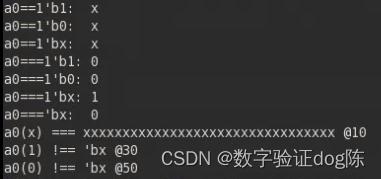

仿真结果如下图所示:

由此可见,只有指定了位宽的x态并且使用四值运算符===才能匹配上logic类型的a0信号,1245行打印的缺省信号’bx最终显示结果是32个x态值,而’b1和’b0显示的还是1’b1和1’b0,印证了我们上面的推论。

总结

本文讨论的四值运算符===和!==的使用场景以及注意事项,希望能对大家验证过程中写模型有所帮助。

1561

1561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?