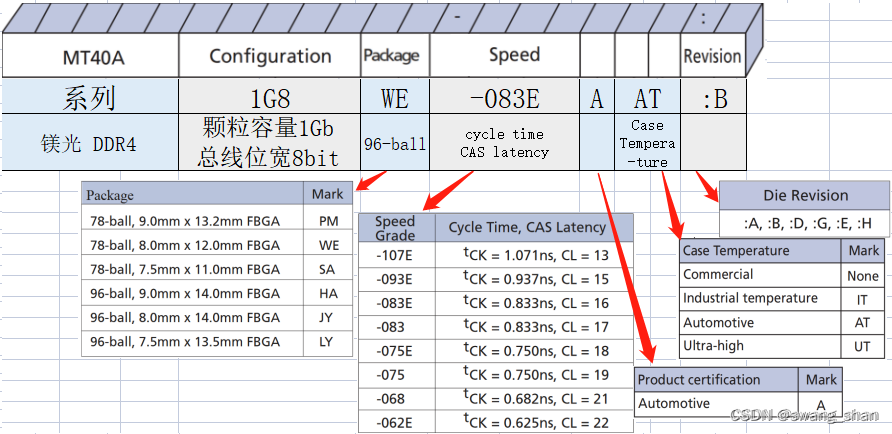

1、名称型号说明

名称型号说明以 MT40A1G8WE-083EAAT:B 为例

2、DDR基本原理

常说的 DDR,其实是 Double Data Rate 双倍速率,是指在时钟上升沿和下降沿各采一次数据(即一个时钟周期采两次),是一种技术。因为此技术广泛使用在DRAM上,所以习惯将DDR代指存储器。

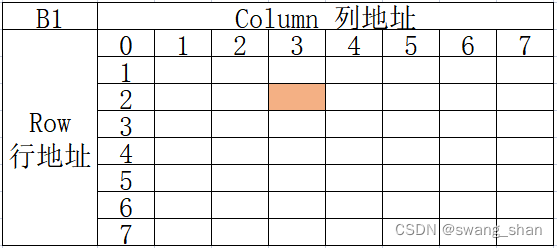

DDR内部是一个存储阵列,将其想象成一张表格,先指定一个行,再指定一个列,就可以找到所需的单元格,这就是内存芯片寻址的基本原理。这个单元格可以称为存储单元,那么这个表格(存储阵列)就是 Logic Bank(简称Bank)。

如果寻址B1\R2\C3,既能找到下图中标注的单元格。

3、性能指标说明

CAL:Command/Address latency

ODT:Nominal, park, and dynamic on-die termination

DBI:Data bus inversion

CAS: Column Address Strobe Latency,表示读取命令发出后到从列地址读出数据到IO接口的间隔时间。

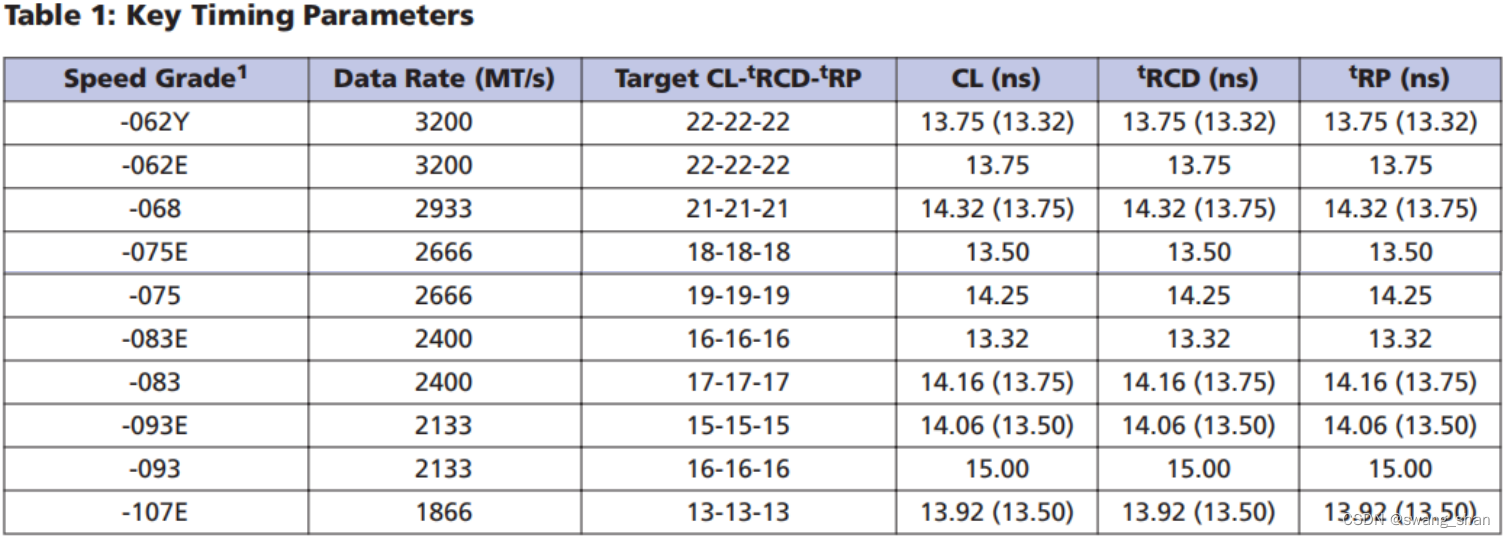

CL: CAS Latency,列地址延迟时间 ,一般用时钟周期数来表示。CL的延迟对于内存读写性能影响最大,被JEDEC当做内存第一时序中的首位。(PCEVA评测室 https://www.bilibili.com/read/cv11825095 出处:bilibili)。

tRCD: RAS-to-CASDelay,内存行地址传输到列地址的延迟时间。

tRP: Row-prechargeDelay,内存行地址选通脉冲预充电时间。

1、speed rate

高速可以向低速兼容。

(1)MT/s:MegaTransfers/s,即百万次/秒。

(2)DDR4-2400 CL17 的时钟周期时间为0.83ns,则CL = 17*0.83=14.17ns。

(3)以-083E为例,2400MT/s 即 1*109 / (2400 * 1000000) * 2 = 0.833ns。

持续更新ing

DDR是一种双倍速率的存储技术,它在时钟的上升沿和下降沿传输数据。内存寻址基于存储阵列,通过行和列地址找到特定单元格。性能指标如CAS延迟(CASLatency)、列地址延迟时间(CL)、行地址到列地址延迟(tRCD)和行地址选通脉冲预充电时间(tRP)对内存性能有直接影响。DDR4-2400的时钟周期为0.83ns,速度率为2400MT/s。

DDR是一种双倍速率的存储技术,它在时钟的上升沿和下降沿传输数据。内存寻址基于存储阵列,通过行和列地址找到特定单元格。性能指标如CAS延迟(CASLatency)、列地址延迟时间(CL)、行地址到列地址延迟(tRCD)和行地址选通脉冲预充电时间(tRP)对内存性能有直接影响。DDR4-2400的时钟周期为0.83ns,速度率为2400MT/s。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?