摘要:

针对工业自动化对控制能力和强实时性的需求,提出了一种基于

FPGA

的改进型

EtherCAT

硬件主站方案

。

该方案利用

Zynq-7000

平台,在

PL

端实现

FPGA

协议栈,以保证核心功能的高效执

行

。

基于

AXI4

总线设计

PS

与

PL

间的数据交互机制,提升主站的灵活性和数据传输效率

。

实验证明,

该设计实现了

88 ns

的最大通信抖动,保持了硬件主站的高实时性,并融合了

ARM

的灵活性

。

0

引言

近年来,由于

EtherCAT

实时工业以太网技术的卓

越性能

[

1

]

,吸引了众多学者进行相关研究

。

其中在

Windows

和

Linux

操作系统上构建

EtherCAT

主站( 即

软件主站) 已成为工业控制领域的热点

[

2

]

。

然而,国

内外关于软件主站的实时性研究都因为操作系统的

性能而限制在

μ

s

级

[

3-5

]

。

为了突破这一瓶颈,孙跃祥

等

[

6

]

将

EtherCAT

协议栈部分硬件化,即把协议栈的

数据 链 路 层 部 署 在

FPGA

(

field-programmable gate

array

,现场可编程阵列) 上以降低部分抖 动

。

经 琦

等

[

7

]

进 一 步 将

EtherCAT

主站协议栈完全部署在

FPGA

上,以此来提升主站性能

。

这种

“

硬件主站

”

的

方法在提升硬件性能上取得了显著的效果,最大通信

抖动仅有

5 ns

。

由于缺乏强大的主控单元,在工业控

制领域上有一定的局限性

。

文献[

8]提出将协议栈部

署在

Zynq

的

FPGA

上,主站的实时性由实时操作系统

保障

。

这使得通信周期的最大抖动高达

15

μ

s

,并未

体现出硬件主站强大的实时性能

。

针对以上问题,本文采用

Zynq

系列芯片

。

该芯片

集成了

ARM

(

advanced risc machine

,高级精简指令集

计算机) 双核

Cortex-A9

处理器和具有

28 nm

制程的

FPGA

可编程逻辑阵列

[

9

]

,通过该芯片构建出更为高

效的

EtherCAT

硬件主站的设计方案

。

该方案通过软硬件协同设计的方式充分结合了

Zynq

的

ARM

处理器处理复杂任务的能力,以 及

FPGA

硬件实时性的能力,既弥补传统软件主站性能

上的不足,又解决了单一

FPGA

主站灵活性差的问题,

满足了工业控制领域对控制和性能的双重需求

。

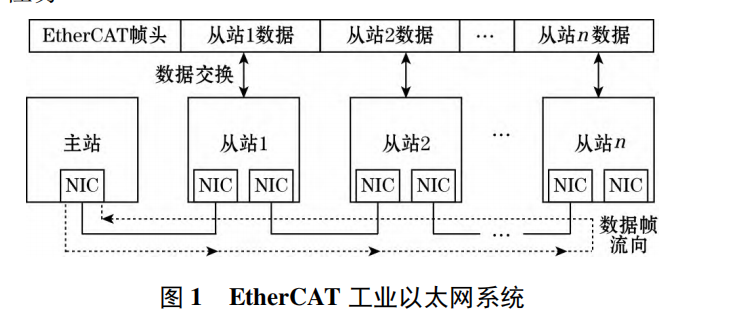

1

EtherCAT

工业以太网概述

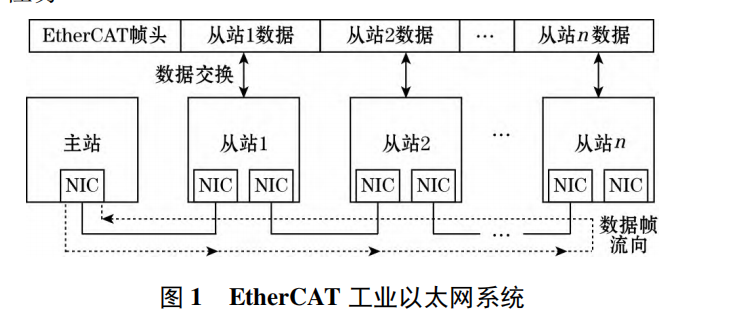

EtherCAT

工业以太网系统由核心的主站设备和

多个执行单元

———

从站设备构成

。

如图

1

所示,主站

作为系统中心负责发起数据传输,通过发送数据帧来

控制整个网络

。而各从站设备则分布在网络中,它们

的主要 任 务 是 响 应 主 站 的 指 令,执行具体的操作

任务

。

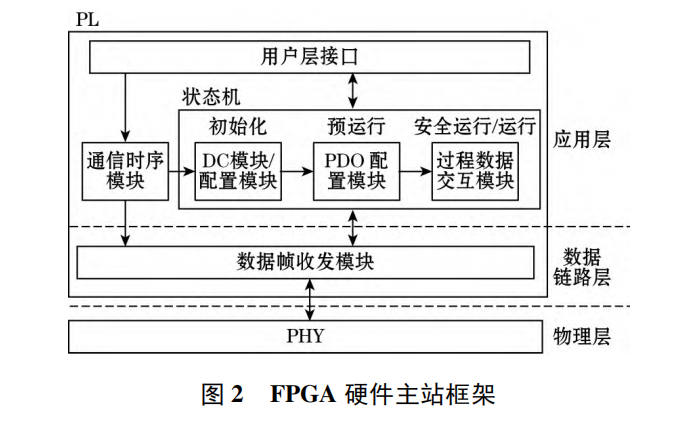

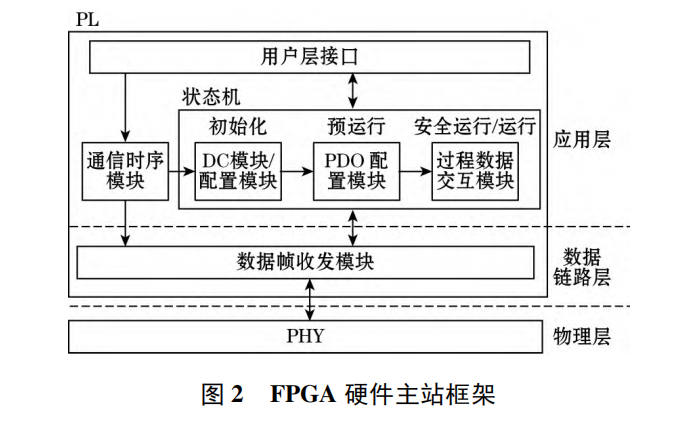

2

PL

设计

为了方便使用

verilog HDL

(

hard description lan

guage

,硬件描述语言) 实现

EtherCAT

协议栈,本文依

据

OSI

七层网络模型对协议栈进行了层次划分,具体

分为应用层

、

数据链路层

、

物理层,

FPGA

硬件主站框

架如图

2

所示

。

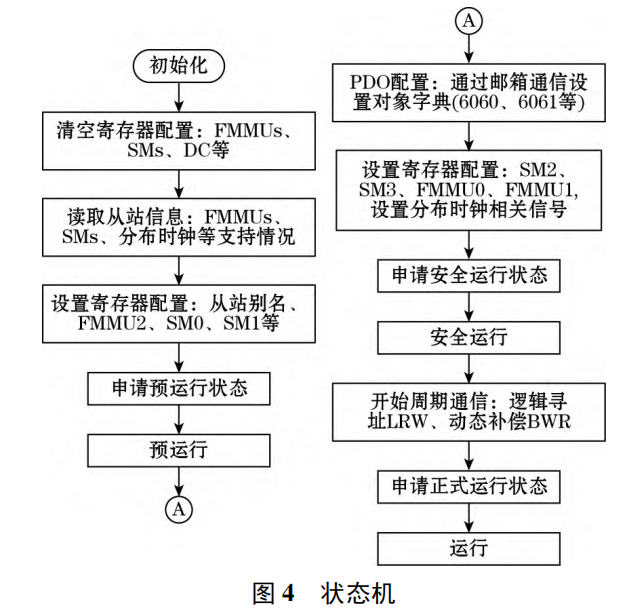

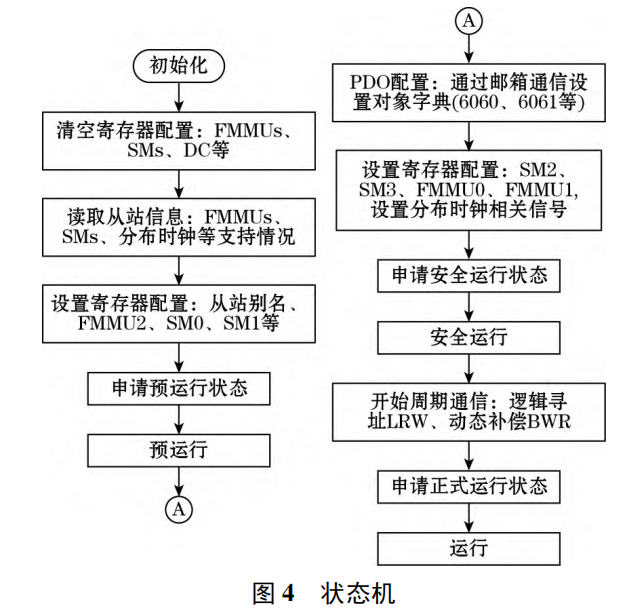

2.2

应用层

EtherCAT

状态机

EtherCAT

状态机是

EtherCAT

协议栈的基础,它

通过精确管理通信流程,确保系统的可靠性和稳定

性

。

状态机虽然增加了系统的复杂性,但对保障协议

栈的可靠性至关重要

。

其设计允许从站在配置错误

时拒绝状态变更,有效避免了潜在的运行故障

。

图

4

为主 站 使 能 从 站 从 初 始 化状态进入运行 (

OP

,

operation

) 的大致流程图

。

信迈提供ethercat主站定制。

359

359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?