学习目标:

- 理解动态随机存取存储器的基本原理和工作机制。

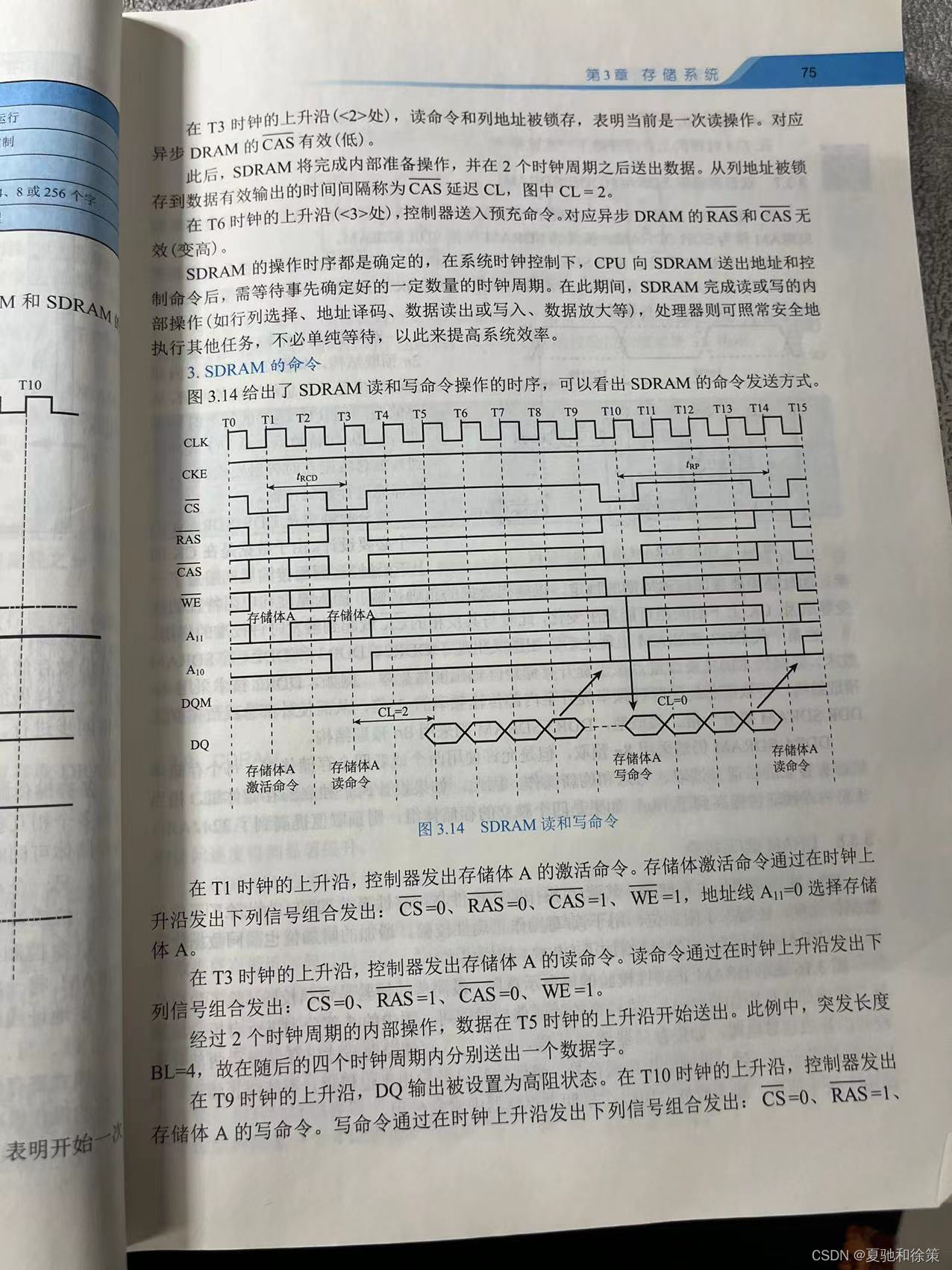

- 掌握动态随机存取存储器的读写操作及时序。

- 理解动态随机存取存储器的存储单元结构和电路设计。

- 熟悉动态随机存取存储器的刷新技术及其影响因素。

- 理解动态随机存取存储器与静态随机存取存储器的异同。

- 掌握动态随机存取存储器的容量扩展技术和多模式存储器的设计思想。

- 了解动态随机存取存储器的应用场景及其发展趋势。

学习步骤:

学习动态随机存取存储器(DRAM)时,我会遵循以下步骤:

-

学习DRAM的基本原理:了解DRAM存储器单元的组成,以及如何读取和写入数据。

-

理解DRAM的读/写时序:学习DRAM的读/写时序,了解时钟信号如何控制DRAM操作,并学习如何选择合适的时序参数以满足系统要求。

-

掌握DRAM芯片的布局:了解DRAM芯片的物理布局,包括存储阵列、行地址译码器、列地址译码器、I/O线路和控制逻辑。

-

学习DRAM控制电路的设计:学习如何设计DRAM控制电路,包括行地址译码器、列地址译码器和预充电电路等。

-

了解DRAM刷新技术:学习DRAM的刷新原理和操作,包括自刷新和外部刷新,以确保数据的稳定性和一致性。

-

掌握DRAM的性能参数:了解DRAM的性能参数,如访问时间、带宽、刷新周期等,以及它们之间的相互关系,以满足系统性能需求。

-

学习DRAM的容量扩展技术:了解DRAM的容量扩展技术,包括多芯片选择器(MCS)、双数据率(DDR)和动态RAM(DRAM)的堆叠等。

-

掌握DRAM的故障排除技巧:学习如何排除DRAM的故障,包括使用测试工具和技术手段来诊断和解决问题。

总的来说,学习DRAM需要掌握其基本原理、读/写时序、芯片布局、控制电路设计、刷新技术、性能参数、容量扩展技术以及故障排除技巧等方面的知识。需要通过理论学习、实验操作、参考资料等多种方式进行综合学习,才能深入理解和掌握DRAM的工作原理和应用。

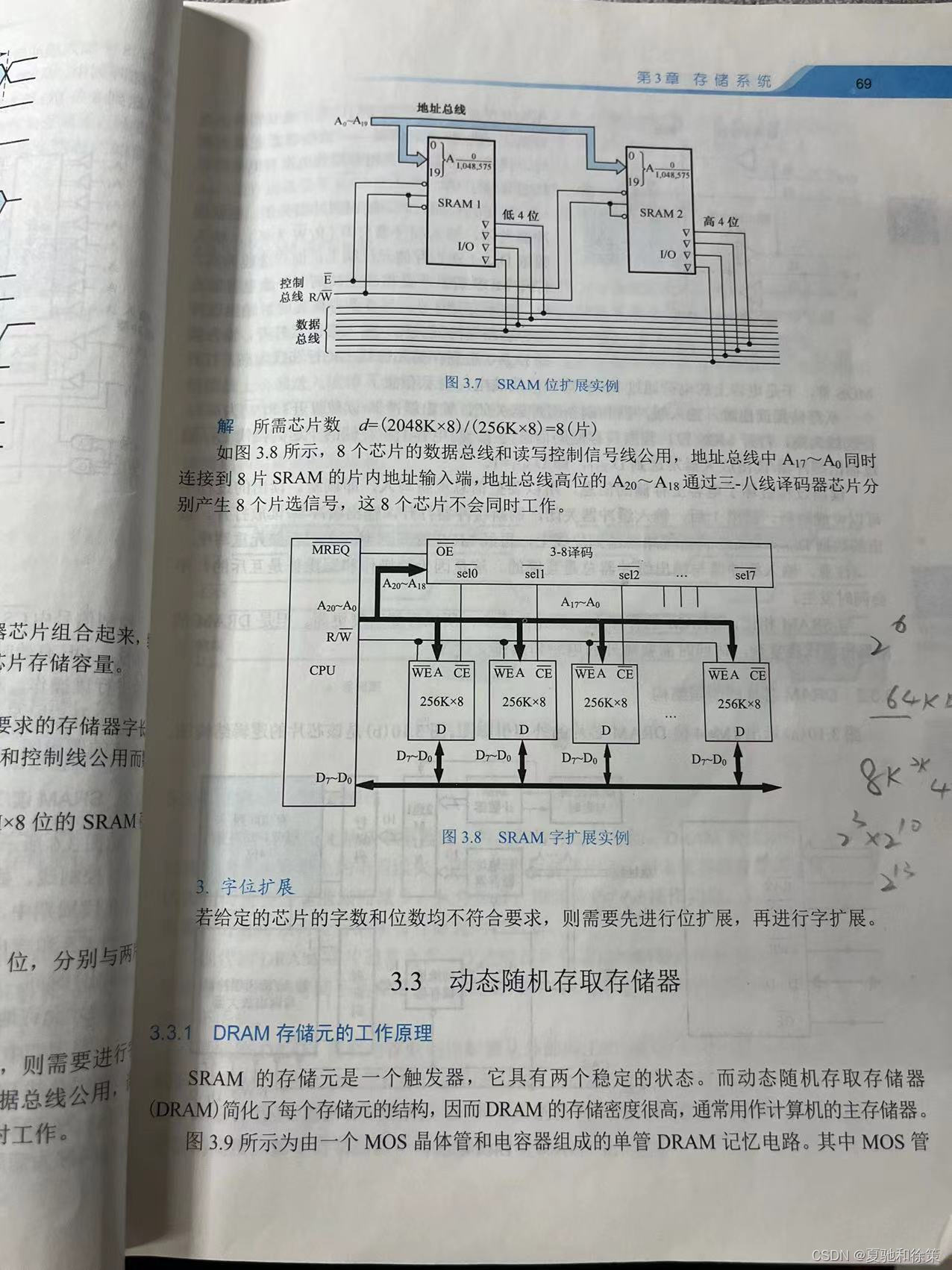

3.3.0 单管动态存储元

单管动态存储元(Single-Transistor Dynamic Random-Access Memory,简称单管DRAM)是一种常见的动态存储器,用于存储和读取数字数据。它是一种非易失性存储器,意味着数据在电源断开时也可以保持不变。

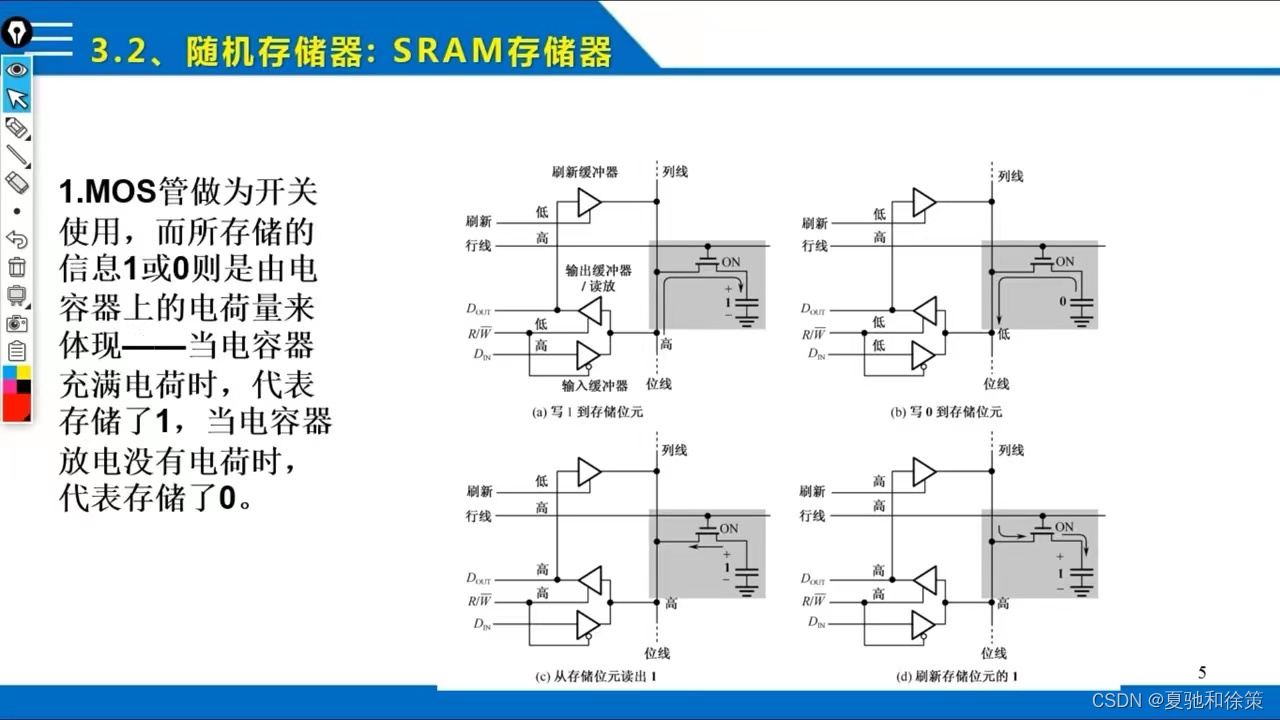

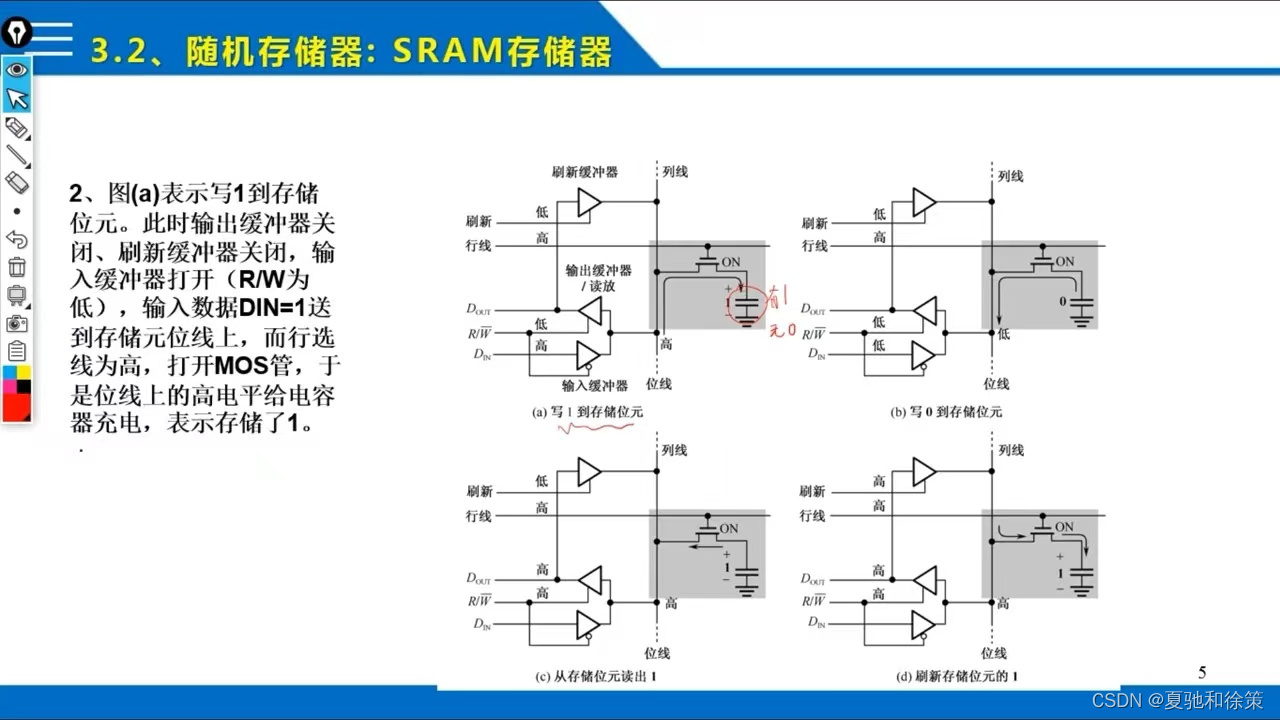

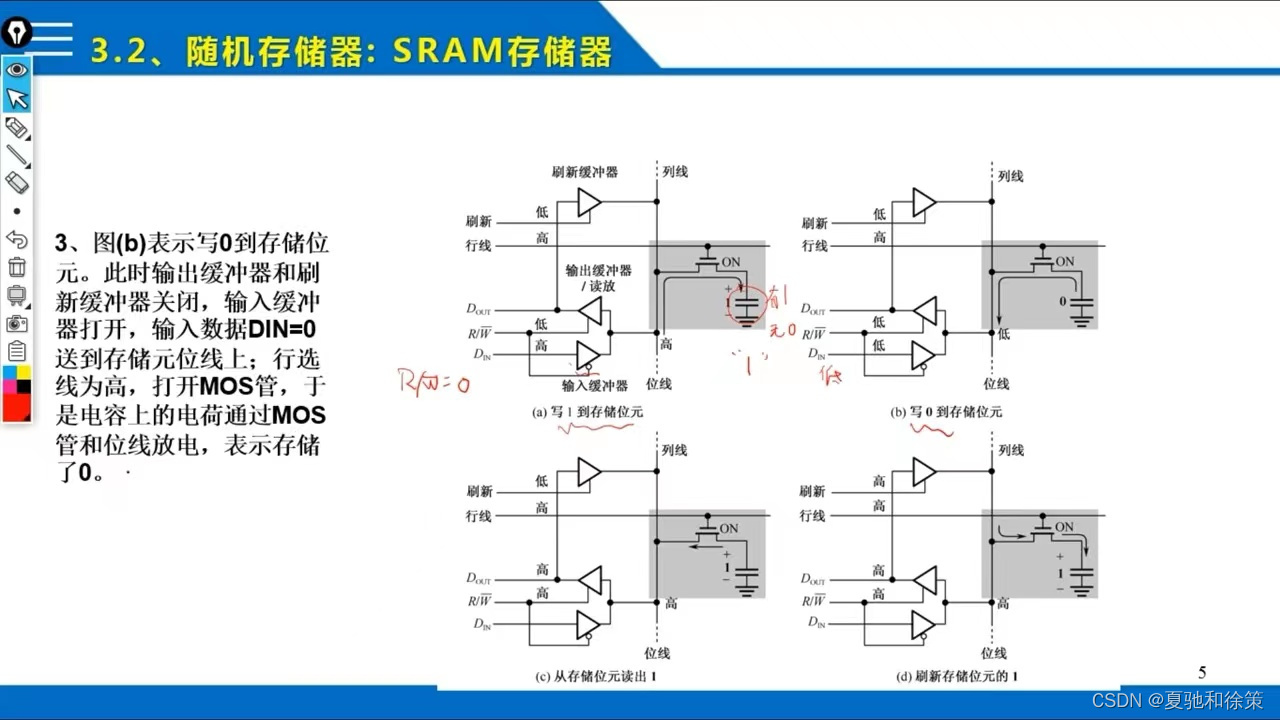

单管DRAM主要由一个MOSFET(金属氧化物半导体场效应晶体管)和一个电容器组成。MOSFET充当存储元件,电容器用于存储电荷。

其工作原理如下:

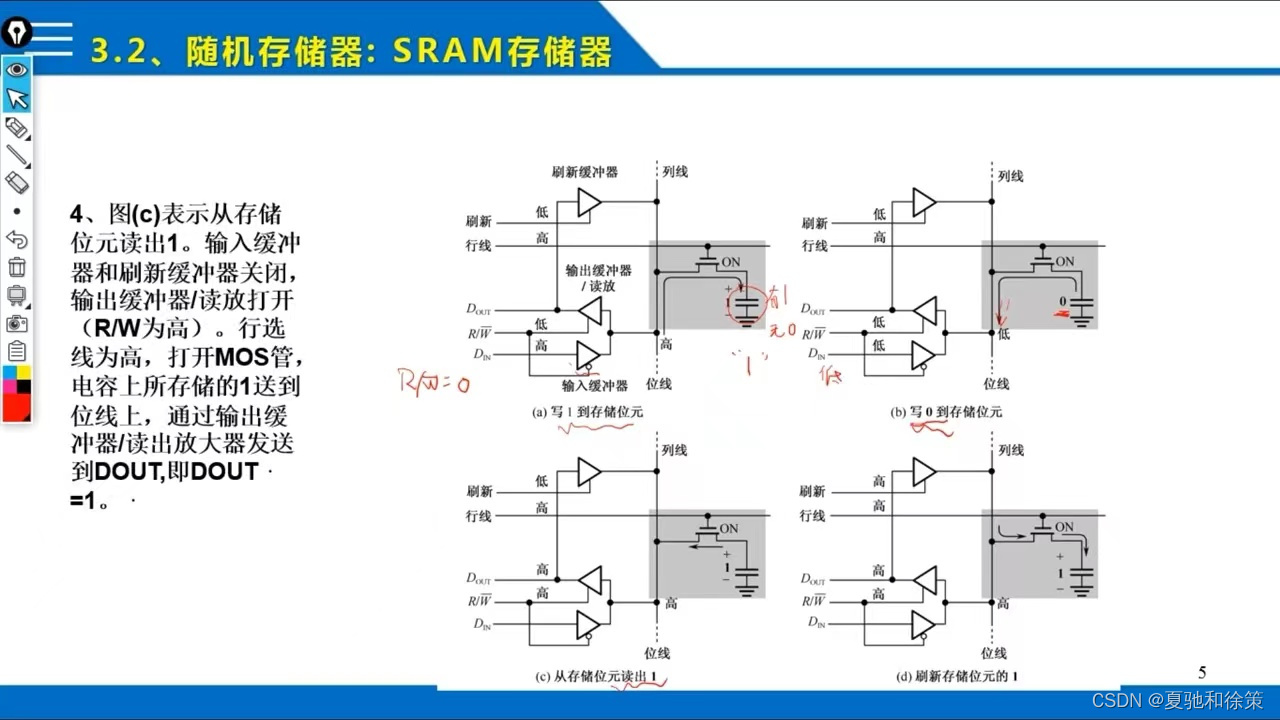

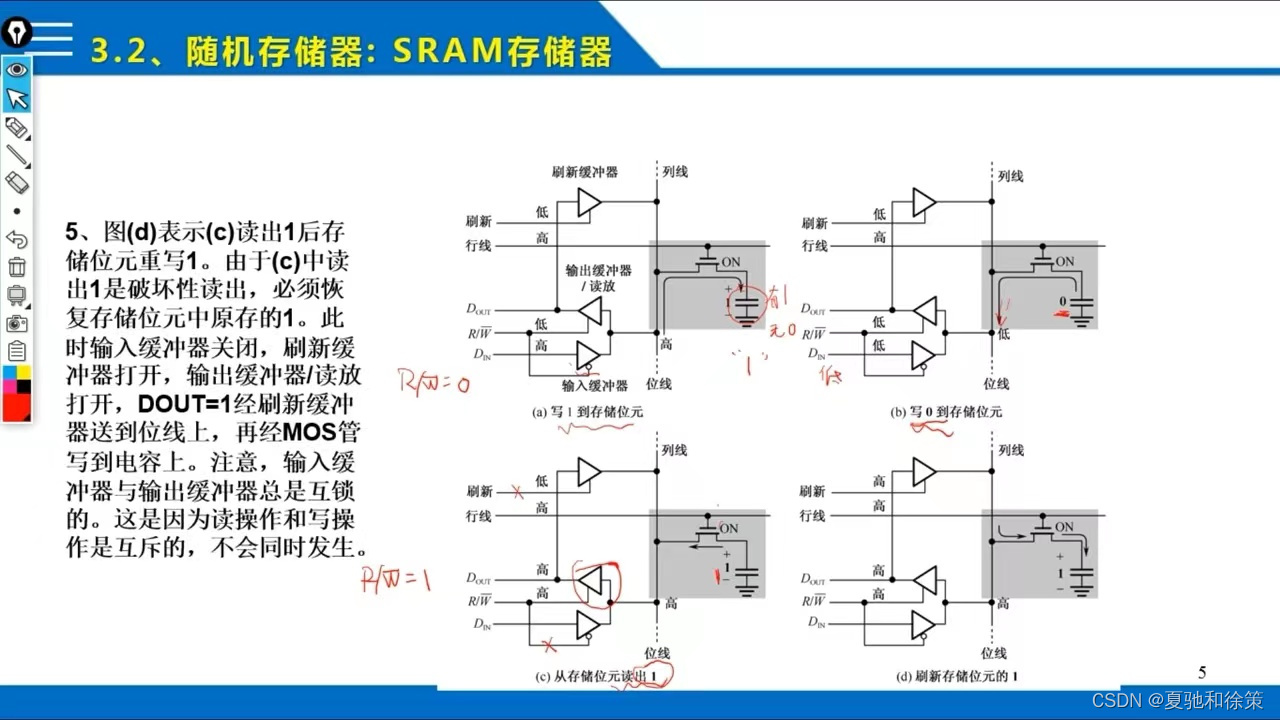

1. 写入操作:当需要写入数据时,将数据电压应用到MOSFET的栅极(Gate)上。如果数据为高电平(逻辑1),栅极上的电荷会导致MOSFET导通,电容器充电。如果数据为低电平(逻辑0),栅极上没有电荷,MOSFET截断,电容器不充电。通过这种方式,数据被存储在电容器的电荷状态中。

2. 读取操作:当需要读取数据时,通过栅极将读取电压应用到MOSFET上。如果电容器被充电,栅极上的电荷会被感应出来,MOSFET导通,表示数据为逻辑1。如果电容器没有充电,栅极上没有电荷,MOSFET截断,表示数据为逻辑0。

单管DRAM的主要优势是存储元件简单,占用面积小,使得它在集成电路中可以实现高密度的存储。然而,它也存在一些缺点,例如读写操作需要周期性刷新来保持数据,刷新操作会消耗功耗,同时存储的电荷会逐渐泄漏,导致数据丢失,因此需要定期刷新。

为了解决这些问题,现代计算机系统中更常用的是基于多个传输门的静态RAM(SRAM),它具有更快的读写速度和更好的稳定性,但相应地也需要更多的电路和面积。

刷新操作:

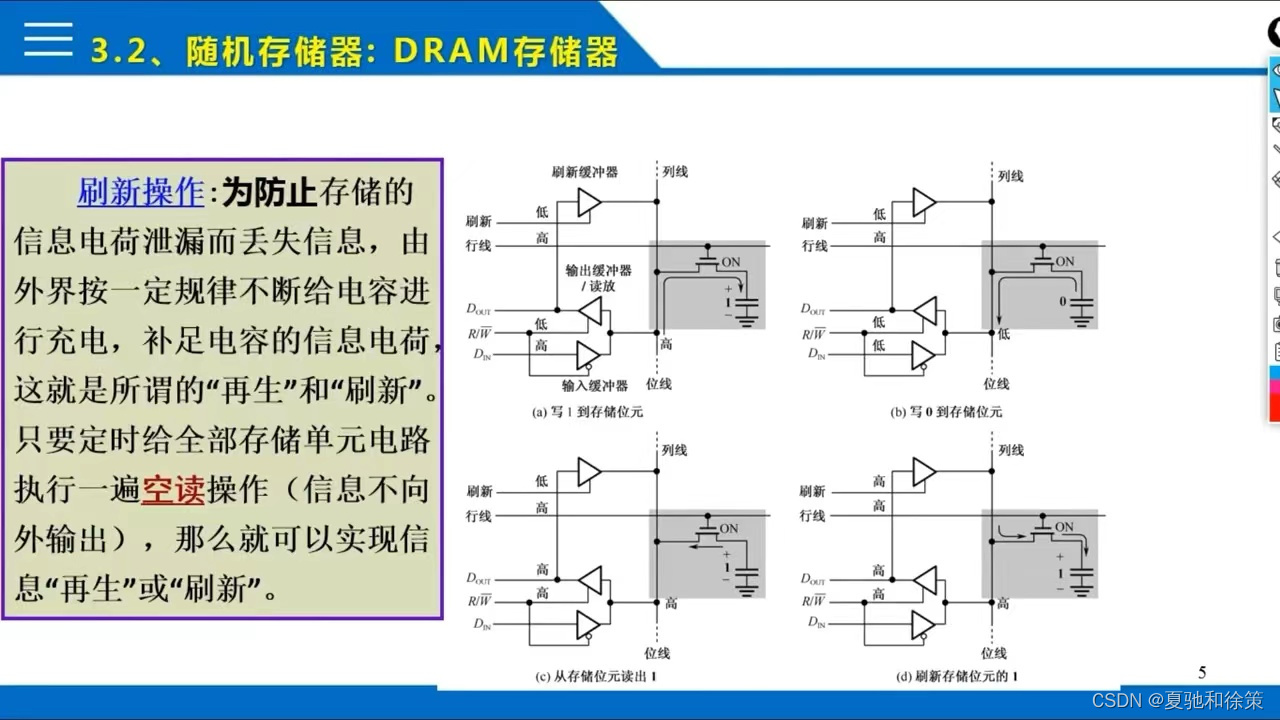

DRAM(Dynamic Random-Access Memory)是一种动态随机访问存储器,它使用电容器存储数据,并且数据需要定期刷新来保持有效。刷新操作是指DRAM中周期性地重新激活电容器以重新存储数据的过程。

DRAM中的电容器由于电荷泄漏而逐渐失去电荷,导致数据丢失。为了避免数据丢失,DRAM需要进行周期性的刷新操作。刷新操作涉及逐个访问DRAM中的存储单元,并将其内容重新写入相同的位置。这样,电容器中的电荷被刷新,数据得以保持。

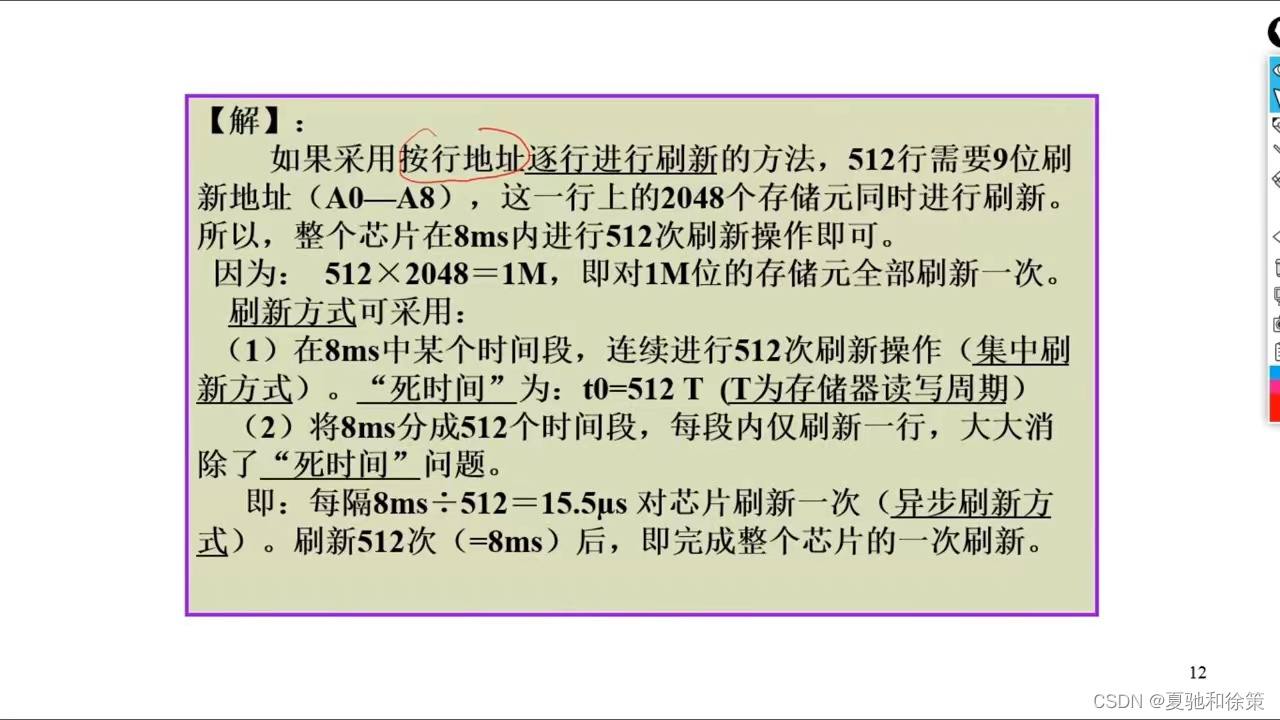

刷新操作通常是以行为单位进行的,称为行刷新(Row Refresh)。行刷新涉及选择一个DRAM芯片中的行,并逐个访问该行中的存储单元进行刷新。刷新操作的频率取决于DRAM芯片的规格和要求,通常在几毫秒的时间范围内进行。

刷新操作是DRAM的一个重要环节,但也会带来一些性能开销。因为刷新期间,DRAM无法进行读取或写入操作,导致存储器无法访问。为了最小化对系统性能的影响,通常在刷新操作与访问操作之间进行时间分片,以确保刷新操作不会过多地占用系统资源。

随着技术的进步,现代DRAM芯片通常采用自动刷新技术,即内部的控制电路会自动执行刷新操作,无需外部干预。这样可以减少对系统软件的要求,并提高DRAM的可靠性和性能。

1.刷新周期

DRAM的刷新周期是指刷新操作的时间间隔,即多长时间进行一次完整的刷新。刷新周期是DRAM芯片的一个重要参数,通常以毫秒(ms)为单位表示。

刷新周期的具体数值取决于DRAM芯片的规格和制造商的设计选择。常见的刷新周期范围为4 ms到64 ms之间。一般而言,刷新周期越短,DRAM的数据保持能力越好,但也会增加刷新操作对系统性能的影响。

根据JEDEC(Joint Electron Device Engineering Council)的标准,常见的DRAM刷新周期包括:

- 64 ms:这是传统的刷新周期,也是最长的周期。它提供了最高的数据保持能力,适用于对数据可靠性要求较高但对性能要求不敏感的应用。

- 32 ms:这是常见的刷新周期,提供了较高的数据保持能力,适用于大多数一般应用场景。

- 16 ms:这是一种中等刷新周期,提供了较好的数据保持能力,适用于对性能有一定要求的应用。

- 8 ms:这是一种较短的刷新周期,提供了更高的性能,但数据保持能力相对较低,适用于对性能要求非常高的应用。

需要注意的是,刷新周期的选择需要平衡数据保持能力和系统性能之间的要求。较短的刷新周期会增加刷新操作对系统性能的影响,而较长的刷新周期可能会降低数据的可靠性。因此,在设计和配置系统时,需要综合考虑应用的要求和DRAM芯片的规格来确定适当的刷新周期。

2.刷新方式

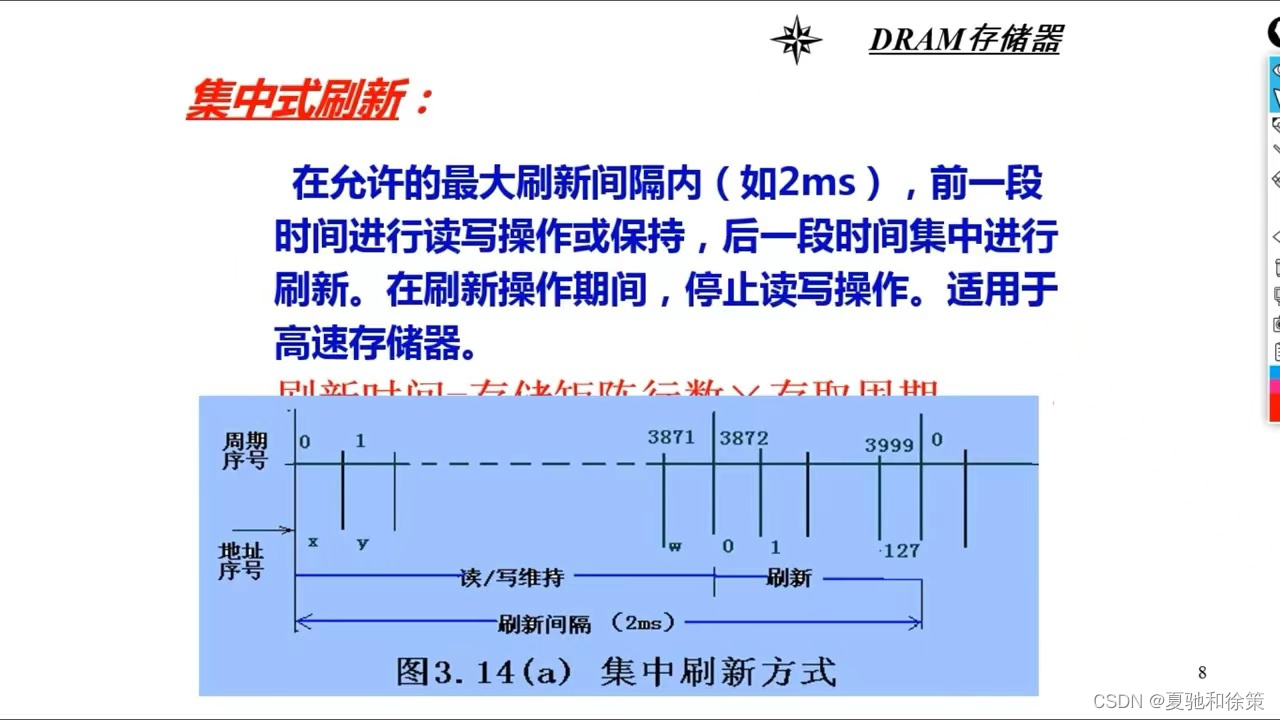

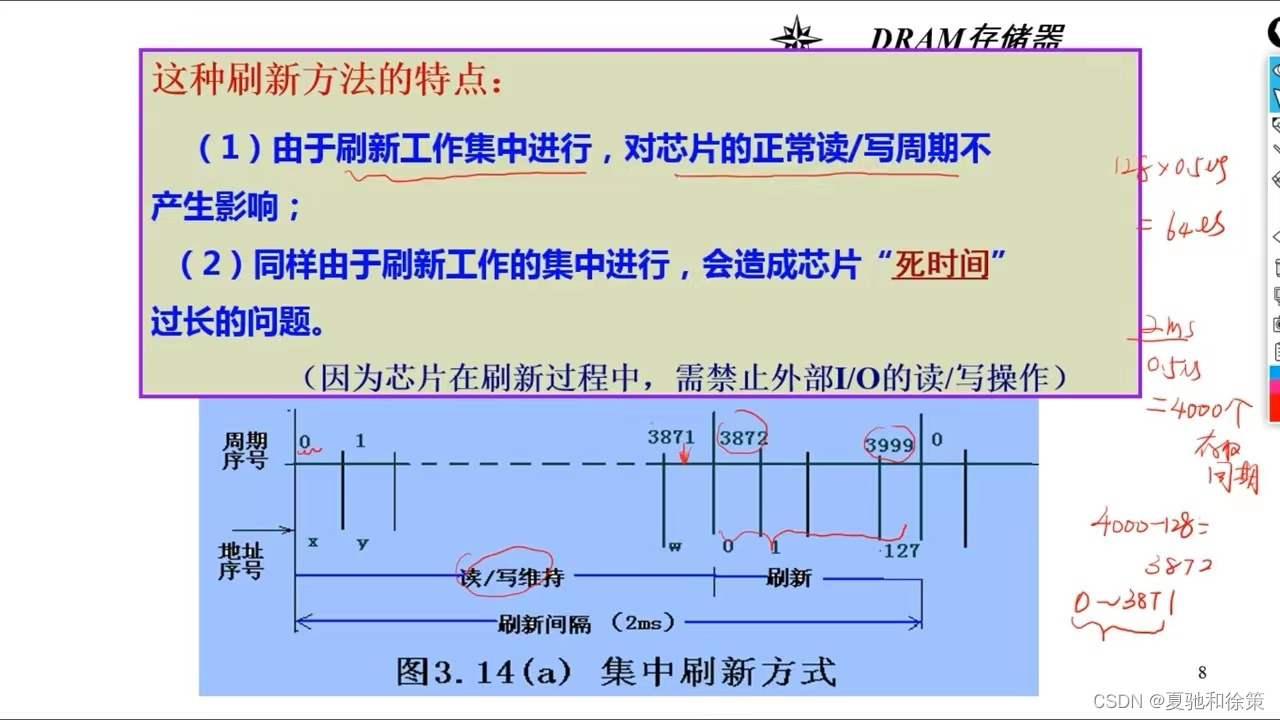

(1)集中式刷新

DRAM的集中式刷新是一种刷新方式,用于保持DRAM中存储的数据的有效性。在集中式刷新中,所有的存储单元都在同一时间进行刷新操作。

具体而言,集中式刷新是通过一个刷新控制信号来触发整个DRAM芯片中的刷新操作。当刷新控制信号激活时,所有的存储单元都会被逐个刷新,以保持数据的稳定性。

集中式刷新具有以下特点:

1. 同步刷新:所有存储单元在同一时刻进行刷新,因此具有较高的刷新效率。

2. 高效性:集中式刷新可以一次性刷新整个DRAM芯片,无需对每个存储单元进行独立刷新,减少了刷新过程的时间和开销。

3. 简单实现:相对于分布式刷新,集中式刷新的实现较为简单,只需要一个刷新控制信号即可。

然而,集中式刷新也存在一些限制和考虑因素:

1. 性能影响:刷新操作期间,DRAM无法进行读取或写入操作,因此会对系统性能产生一定的影响。在设计系统时,需要合理安排刷新操作的时间,以平衡刷新和访问的需求。

2. 刷新周期选择:集中式刷新需要在刷新周期内完成对整个DRAM芯片的刷新,因此需要选择合适的刷新周期,以确保数据的可靠性,并且不过度占用系统资源。

3. 大容量DRAM的挑战:对于大容量的DRAM芯片,集中式刷新可能会增加刷新过程的时间和复杂性,因为需要在较短的时间内刷新更多的存储单元。

综上所述,集中式刷新是一种常见的DRAM刷新方式,通过统一控制所有存储单元的刷新操作来维持数据的有效性。在设计和配置系统时,需要考虑性能、刷新周期和DRAM容量等因素,以确保刷新操作的有效性和系统的稳定性。

我的理解:

我的理解:

可以将集中式刷新比喻为一种集中管理的方式。

想象一下,你有一个大型的仓库,里面摆满了各种货物。为了保持这些货物的质量和可用性,你决定定期进行全面的清理和整理。于是你制定了一个计划,每隔一段时间,你会发出一个信号,告诉所有的工人同时开始清理各自负责的货物区域。

在这个比喻中,仓库就是DRAM芯片,货物就是存储的数据,工人就是DRAM的刷新电路,而你发出的信号就是刷新控制信号。

集中式刷新的思想是将所有存储单元的刷新操作集中起来,通过统一的刷新控制信号来触发。这样做的好处是:

- 同步性:所有存储单元在同一时刻进行刷新,确保数据的一致性和稳定性。

- 效率性:一次性刷新整个DRAM芯片,减少了刷新过程的时间和开销。

- 简单性:只需要一个刷新控制信号,实现相对简单。

然而,集中式刷新也有一些考虑因素,如刷新周期的选择和对系统性能的影响。类比仓库的情境,你需要合理安排刷新的时间,以平衡刷新和货物的使用需求,确保仓库的正常运作。

通过这个比喻,你可以更好地理解集中式刷新的概念和工作原理。它是一种集中管理和协调的方式,用于保持DRAM中存储的数据的有效性和稳定性。

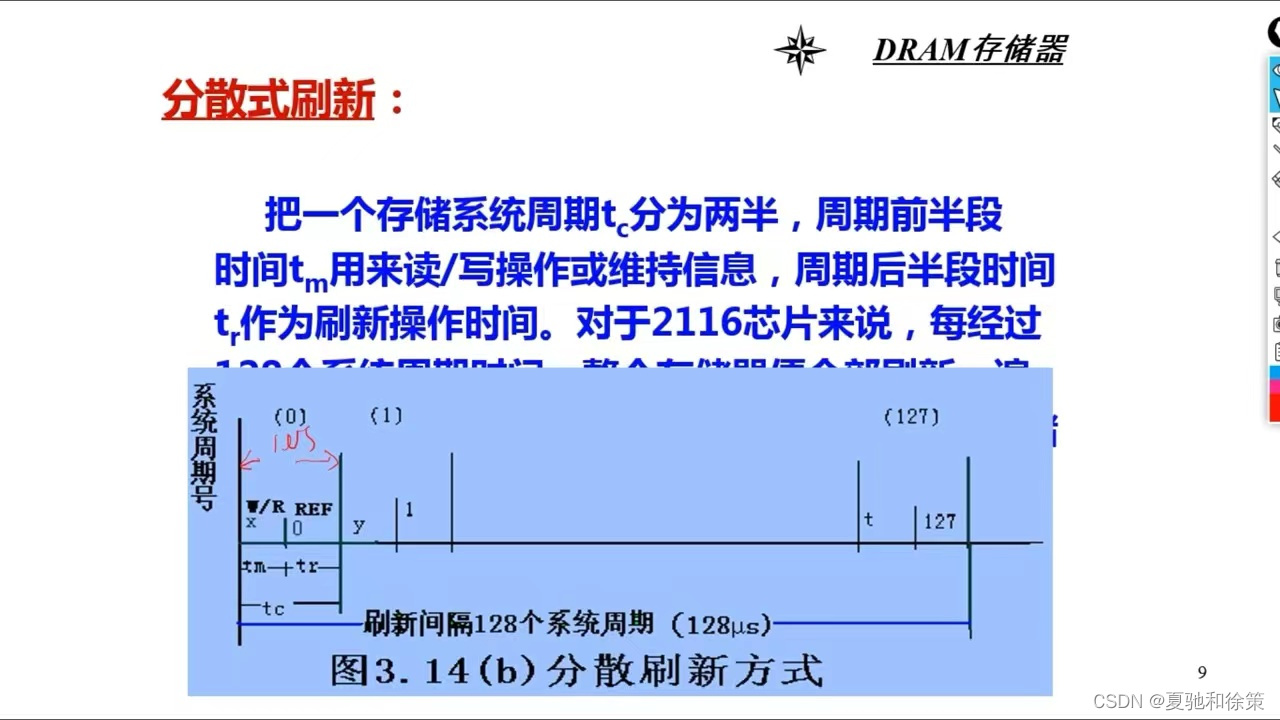

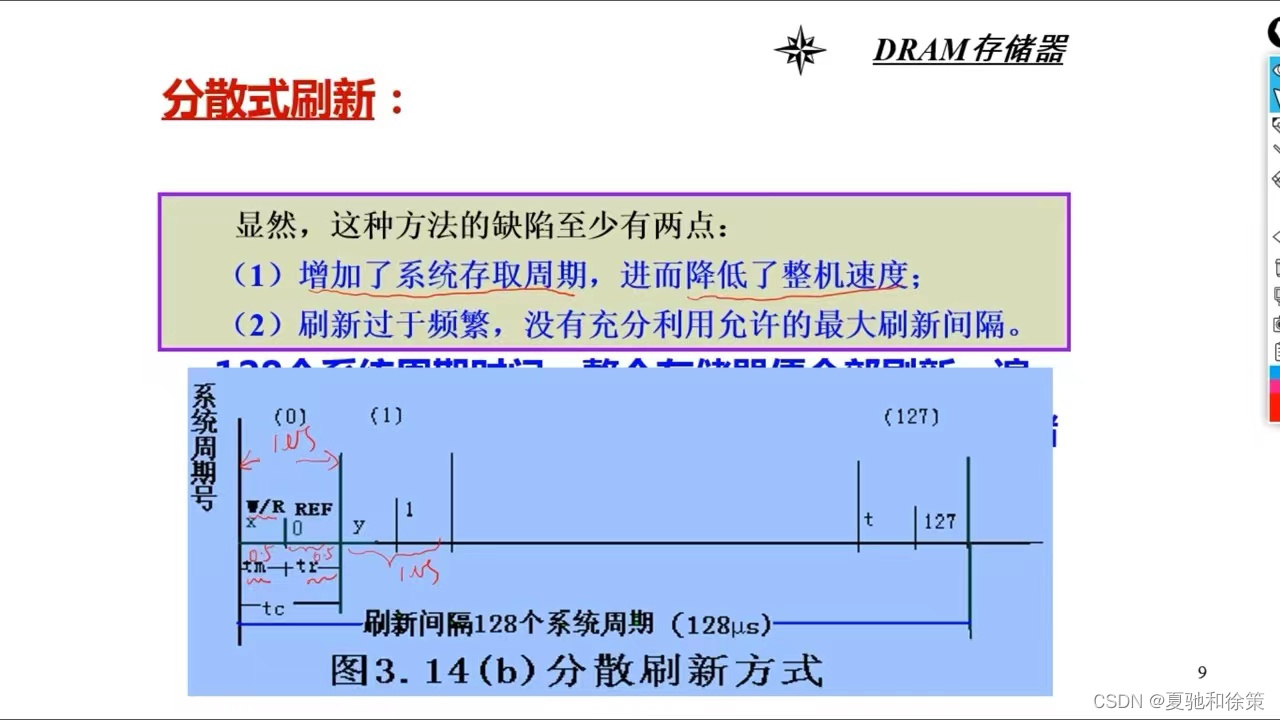

(2)分散式刷新

分散式刷新是一种用于动态随机存取存储器(DRAM)的刷新方式,与集中式刷新相对应。在分散式刷新中,DRAM芯片的刷新操作被分散到不同的时间和位置进行。

具体而言,分散式刷新将DRAM芯片划分为多个刷新组(refresh bank),每个刷新组拥有一组存储单元。每个刷新组都有自己的刷新计时器,根据设定的刷新周期,每个刷新组在不同的时间进行刷新操作。

分散式刷新具有以下特点:

1. 并行刷新:不同的刷新组可以在同一时间内进行刷新,实现并行刷新,提高了刷新效率。

2. 分散负载:刷新操作被分散到多个刷新组,减少了单个刷新操作对系统性能的影响,提高了系统的整体性能。

3. 灵活性:通过刷新组的设置,可以根据需求和系统特点来调整刷新操作的分布和频率。

然而,分散式刷新也需要考虑一些因素:

1. 资源分配:分散式刷新需要更多的硬件资源来实现多个刷新组,这可能增加了系统的复杂性和成本。

2. 刷新策略:需要合理设置刷新周期和刷新组的划分,以平衡刷新的需求和系统的性能。

3. 数据一致性:在刷新组之间进行刷新时,需要确保数据的一致性,避免数据丢失或冲突。

综上所述,分散式刷新是一种将DRAM芯片的刷新操作分散到不同时间和位置的刷新方式。它通过并行刷新和分散负载来提高刷新效率和系统性能。在设计和配置系统时,需要综合考虑刷新策略和资源分配,以确保数据的可靠性和系统的稳定性。

我的理解:

我的理解:

可以用一个类比来理解分散式刷新的概念。

想象一下你是一个学生宿舍的管理员,有很多房间需要定期打扫和清洁。为了提高效率,你决定将打扫任务分散给不同的宿舍楼层。

在集中式刷新中,你会规定一个特定的时间,所有房间的打扫人员都在同一时间进行清洁操作。这可能会导致很多人同时工作,拥堵和效率低下。

而在分散式刷新中,你将不同的房间分配给不同的打扫人员,并规定每个人员的打扫时间。例如,一些人员在上午进行打扫,另一些人员在下午进行打扫。这样一来,打扫人员分散在不同的时间进行工作,减少了拥堵和提高了效率。

类比中,学生宿舍的每个房间就是DRAM芯片的刷新组,打扫人员就是刷新操作,管理员规定的打扫时间就是刷新周期。分散式刷新通过将刷新操作分散到不同的时间和位置,提高了刷新效率和系统性能。

需要注意的是,分散式刷新也需要合理安排打扫时间和刷新组的分配,以平衡资源利用和任务完成。同时,需要确保在刷新期间数据的一致性和可靠性。

通过这个比喻,你可以更好地理解分散式刷新的概念和工作原理。它是一种将刷新操作分散到不同时间和位置的刷新方式,以提高刷新效率和系统性能。

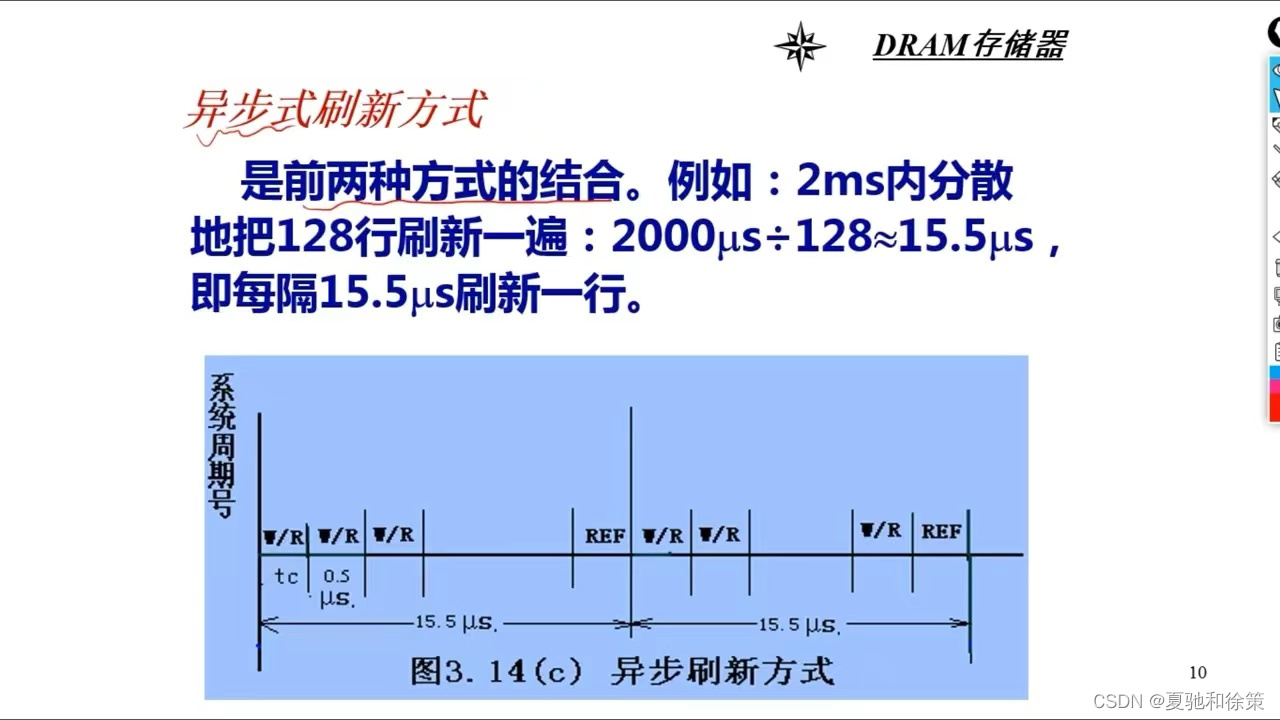

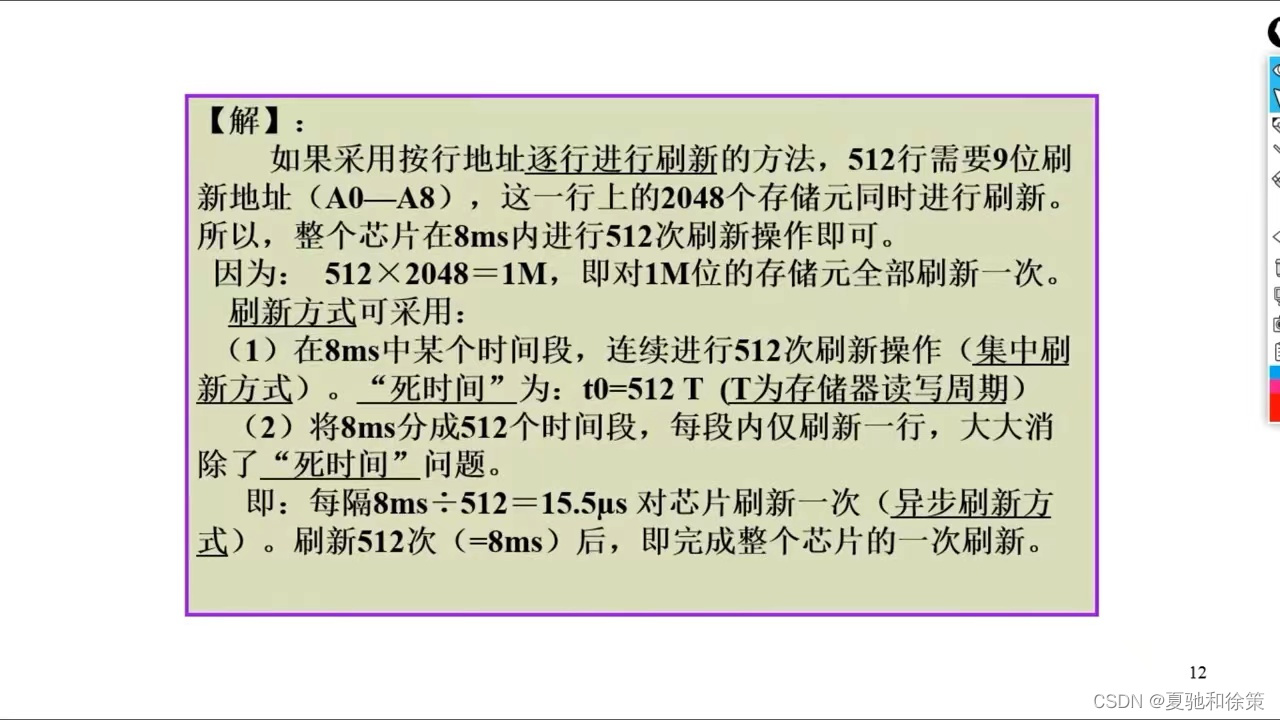

(3)异步式刷新方式

异步式刷新是一种用于动态随机存取存储器(DRAM)的刷新方式,与集中式刷新和分散式刷新相对应。在异步式刷新中,每个存储单元都有自己的刷新计时器,根据其自身的刷新周期进行刷新操作,而不依赖于全局的刷新控制信号。

具体而言,每个存储单元都包含一个刷新计时器或计数器,该计时器在存储单元被访问时开始计时。当计时器达到设定的刷新周期时,存储单元会自动触发刷新操作,更新存储单元中的数据,以保持其稳定性。

异步式刷新具有以下特点:

1. 独立性:每个存储单元都有自己的刷新计时器,刷新操作是相互独立的,不需要全局的刷新控制信号。

2. 灵活性:每个存储单元可以根据其需要设置不同的刷新周期,以满足特定的刷新要求。

3. 分散负载:刷新操作在存储单元级别进行,可以分散刷新操作的负载,减少对系统性能的影响。

然而,异步式刷新也需要考虑一些因素:

1. 管理复杂性:由于每个存储单元都有自己的刷新计时器,需要管理和维护大量的计时器,增加了系统的复杂性和成本。

2. 数据一致性:由于刷新操作是异步的,需要确保数据在刷新过程中的一致性和可靠性,避免数据损坏或冲突。

综上所述,异步式刷新是一种通过每个存储单元自身的刷新计时器进行刷新操作的方式。它具有独立性和灵活性,可以分散刷新操作的负载,提高系统性能。然而,需要管理复杂性和确保数据一致性。

我的理解:

异步式刷新可以通过以下比喻来理解:

假设你是一位学生,每天在学习之余需要给自己的植物浇水。为了确保植物的健康生长,你决定采用异步方式来进行浇水。

在异步方式中,你不使用固定的时间表或闹钟来提醒自己浇水。相反,每个植物都有一个小标签,上面写着它需要浇水的时间间隔。你根据每个植物的标签来判断何时浇水。

当你经过一棵植物时,你检查它的标签。如果标签上的时间间隔已经过去,你就会立即浇水。这样,每棵植物都有自己独立的浇水时间,不需要依赖于全局的计时器。

这种异步方式的好处是你可以更灵活地安排浇水时间。不同的植物可能有不同的需求,有些可能需要频繁浇水,而有些可能需要较长的间隔。你可以根据每个植物的需要来个别处理,确保它们得到适当的水分。

然而,异步方式也需要你保持一定的管理能力。你需要记住每棵植物的浇水周期,并确保在合适的时间内进行浇水,以避免植物干枯或过度浇水。

类比中,每棵植物就是存储单元,标签上的时间间隔就是存储单元的刷新周期,浇水操作就是刷新操作。异步式刷新通过每个存储单元独立进行刷新,提高了刷新的灵活性和效率。

通过这个比喻,你可以更好地理解异步式刷新的概念。它是一种根据存储单元的独立计时器来进行刷新操作的方式,具有灵活性和个别处理的能力。然而,需要保持管理能力以确保适时进行刷新。

例题:

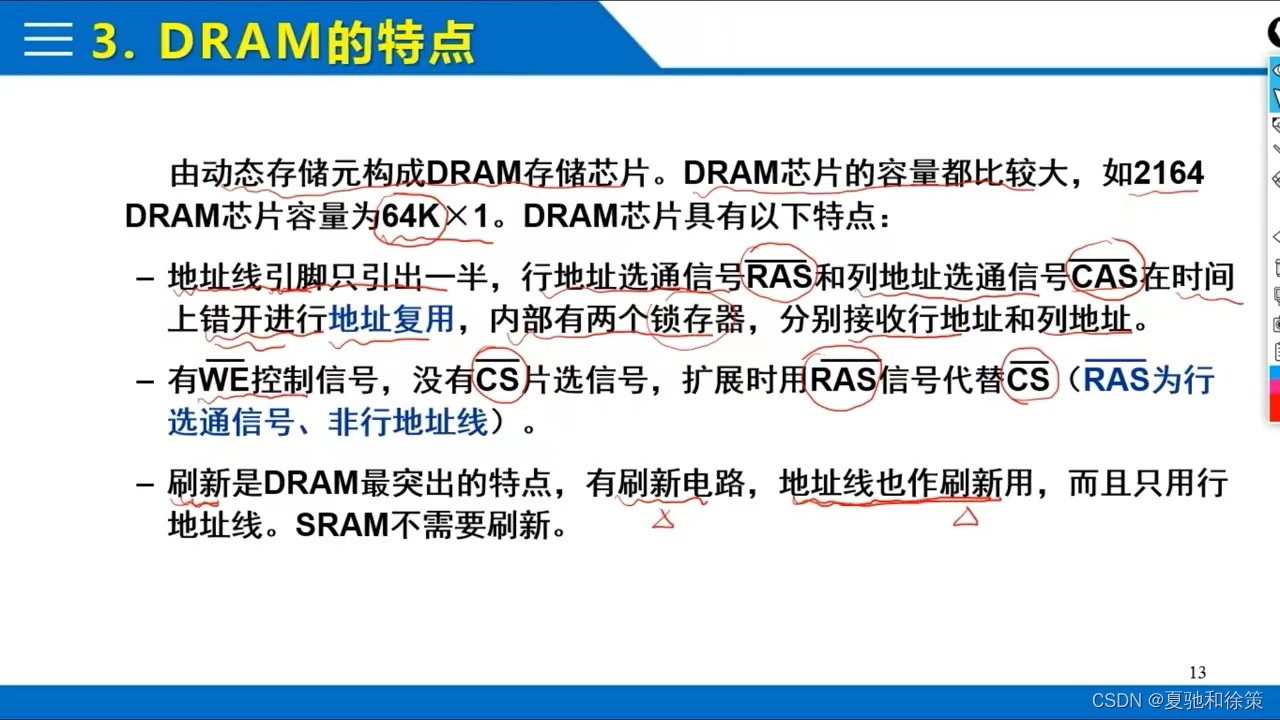

2.DRAM的特点

2.DRAM的特点

动态随机存取存储器(DRAM)是一种常用的存储器技术,具有以下特点:

1. 容量大:DRAM的存储密度很高,能够存储大量的数据。这使得DRAM成为处理大规模数据和高性能计算任务的理想选择。

2. 相对廉价:相比于其他存储器技术如静态随机存取存储器(SRAM),DRAM的制造成本较低,因此在成本敏感的应用中广泛使用。

3. 高速读写:DRAM具有较快的读写速度,可以实现快速的数据访问。这对于需要频繁读写数据的应用非常重要,如计算机内存。

4. 需要刷新:DRAM是一种动态存储器,意味着它的存储单元需要定期刷新以保持数据的有效性。由于存储单元内部的电荷逐渐泄漏,如果不刷新,数据将逐渐丧失。这是与静态存储器的一个区别。

5. 存储单元简单:DRAM的存储单元由一个电容和一个访问晶体管组成,相对于SRAM的存储单元更简单,这也是为什么DRAM能够实现高存储密度的原因之一。

6. 功耗较低:相对于SRAM,在相同的存储容量下,DRAM的功耗较低。这是因为DRAM使用的电容存储数据,而SRAM使用的是触发器电路,后者需要持续的电流来维持存储状态。

需要注意的是,尽管DRAM具有高存储密度和较低成本等优点,但它也有一些缺点。例如,DRAM的访问速度较慢,需要刷新周期,且对于读取操作需要先将数据从存储单元读出并放入内部缓冲区。此外,DRAM的存储单元还容易受到电磁干扰的影响。因此,在设计和使用DRAM时需要考虑这些特点和限制。

3.3 DRAM的存储器

DRAM(Dynamic Random-Access Memory)是一种常见的存储器类型,用于存储计算机系统中的数据。DRAM的存储器结构由多个存储单元组成,每个存储单元存储一个位(0或1)的数据。以下是DRAM存储器的一些重要特点和组成部分:

1. 存储单元:DRAM存储器由大量的存储单元组成,每个存储单元由一个电容和一个访问晶体管组成。电容用于存储数据,而访问晶体管用于读取和写入数据。

2. 地址线:DRAM存储器通过地址线来寻址每个存储单元。地址线用于指定要读取或写入的存储单元的位置。根据地址的不同组合,DRAM可以访问存储器中的特定数据。

3. 行地址译码器:行地址译码器用于选择要访问的存储行。它将输入的行地址解码为对应的行选择信号,从而选择特定的存储行进行读取或写入操作。

4. 列地址译码器:列地址译码器用于选择要访问的存储列。它将输入的列地址解码为对应的列选择信号,从而选择特定的存储列进行读取或写入操作。

5. 控制线:控制线用于传输命令和控制信号,以控制DRAM的操作。例如,读写控制信号(R/W)用于指示DRAM是执行读取操作还是写入操作;预充电信号(Precharge)用于准备存储单元进行下一次读取或写入操作。

6. 刷新操作:DRAM是一种动态存储器,需要定期进行刷新操作以保持数据的有效性。刷新操作是为了补偿电容的泄漏效应,以防止数据丢失。刷新操作可以是集中式刷新、分散式刷新或异步式刷新,以保持存储器中的数据的稳定性。

DRAM的主要优势是存储密度高和成本低,因此被广泛应用于计算机系统中的主存储器(内存)。然而,相对于静态存储器(如SRAM),DRAM的访问速度较慢,需要定期刷新操作,并且对电源噪声和干扰比较敏感。因此,在设计计算机系统时需要综合考虑存储器的特性以满足系统的性能和稳定性要求。

3.3.1 DRAM存储元的工作原理

我的理解:

DRAM(Dynamic Random Access Memory)存储元是计算机中常用的一种存储器类型。其存储单元由一个电容和一个开关晶体管组成,电容中存储着一个电荷,该电荷代表着存储的数据,当需要访问该存储单元时,电荷会被读取或写入。

DRAM存储元的工作原理可以分为三个步骤:

- 写入数据

当需要写入数据时,DRAM存储单元的地址线会将地址信号发送到存储芯片中,控制线将写入命令发送到内存芯片,该命令会使晶体管变为导通状态,将数据写入电容中。在写入数据之前,需要将电容中的电荷清空。

- 读取数据

当需要读取数据时,DRAM存储单元的地址线会将地址信号发送到存储芯片中,控制线将读取命令发送到内存芯片,该命令会使晶体管变为导通状态,读取电容中的电荷。读取完数据后,需要将电容中的电荷清空,以便存储下一次数据。

- 刷新数据

由于电容的电荷会逐渐漏电,导致存储的数据出现错误,因此需要定期刷新电容中的电荷,以维持数据的准确性。DRAM存储器会周期性地发出刷新信号,将所有存储单元中的电荷读出并再次写入,以保证数据的正确性。

以上就是DRAM存储元的工作原理。由于DRAM存储器具有容量大、价格低廉等优点,因此被广泛应用于计算机系统中的主存储器。

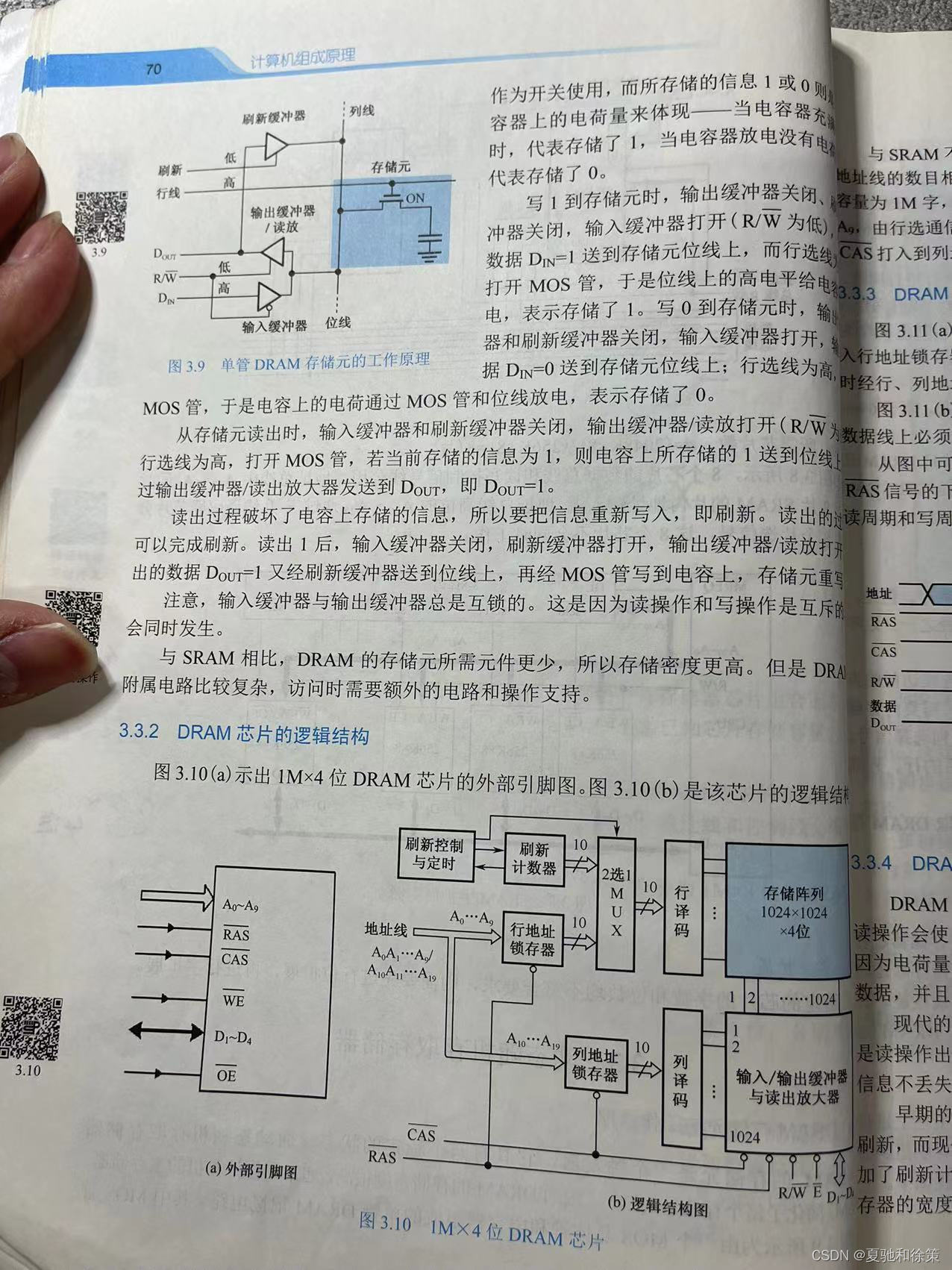

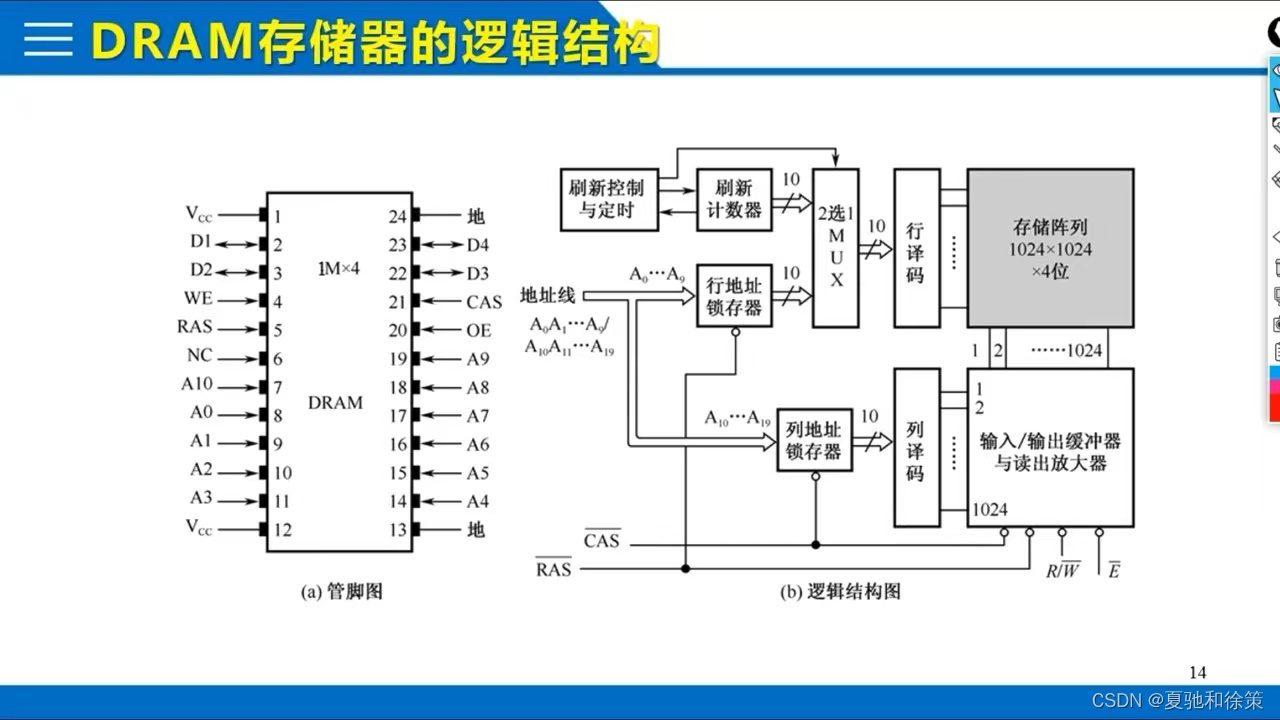

3.3.2 DRAM芯片的逻辑结构

DRAM(Dynamic Random-Access Memory)的逻辑结构包括以下几个关键组件:

1. 存储芯片(DRAM Chip):DRAM芯片是实际存储数据的主要部件。它由一个矩阵形式的存储单元阵列组成,每个存储单元由一个电容和一个访问晶体管组成。DRAM芯片通常具有多个存储单元,每个存储单元存储一个位(0或1)。

2. 地址线(Address Lines):地址线用于将内存中的特定位置与处理器或其他设备进行通信。通过地址线,计算机可以指定要读取或写入的存储单元的位置。

3. 数据线(Data Lines):数据线用于在DRAM芯片和处理器或其他设备之间传输数据。通过数据线,计算机可以将数据写入到特定的存储单元,或从存储单元读取数据。

4. 控制线(Control Lines):控制线用于传输命令和控制信号,以控制DRAM的操作。例如,读写控制信号(R/W)指示DRAM芯片是执行读取还是写入操作;预充电信号(Precharge)用于准备存储单元进行下一次读取或写入操作。

5. 行地址译码器(Row Address Decoder):行地址译码器根据输入的行地址选择要访问的存储行。通过行地址译码器,计算机可以指定要读取或写入的特定行。

6. 列地址译码器(Column Address Decoder):列地址译码器根据输入的列地址选择要访问的存储列。通过列地址译码器,计算机可以指定要读取或写入的特定列。

总体而言,DRAM的逻辑结构是由存储芯片、地址线、数据线、控制线、行地址译码器和列地址译码器等组成。这些组件共同协作,实现计算机对DRAM的读取和写入操作。

DRAM芯片的逻辑结构包括了DRAM芯片中存储单元的排列方式、控制信号的输入输出方式等。

DRAM芯片的存储单元是由一些存储电容和访问晶体管组成的。在一个DRAM芯片中,存储单元通常被排列成一个二维数组的形式,每一行被称为一个“行”,每一列被称为一个“列”。每个存储单元可以通过行地址和列地址来访问,也就是通过行列地址可以唯一地确定一个存储单元。

在访问一个DRAM芯片中的存储单元时,需要先通过行地址选择一个行,然后再通过列地址选择一个列,最后才能读取或写入数据。DRAM芯片内部会通过行地址解码器和列地址解码器来选择相应的行和列,然后将数据读取或写入到这个存储单元。

DRAM芯片还需要一些控制信号来控制读写操作。例如,读写控制信号用于控制读取或写入操作,时序控制信号用于确定读写操作的时序。在DRAM芯片内部,这些控制信号会被解码并转换为相应的操作信号,以控制存储单元的读写操作。

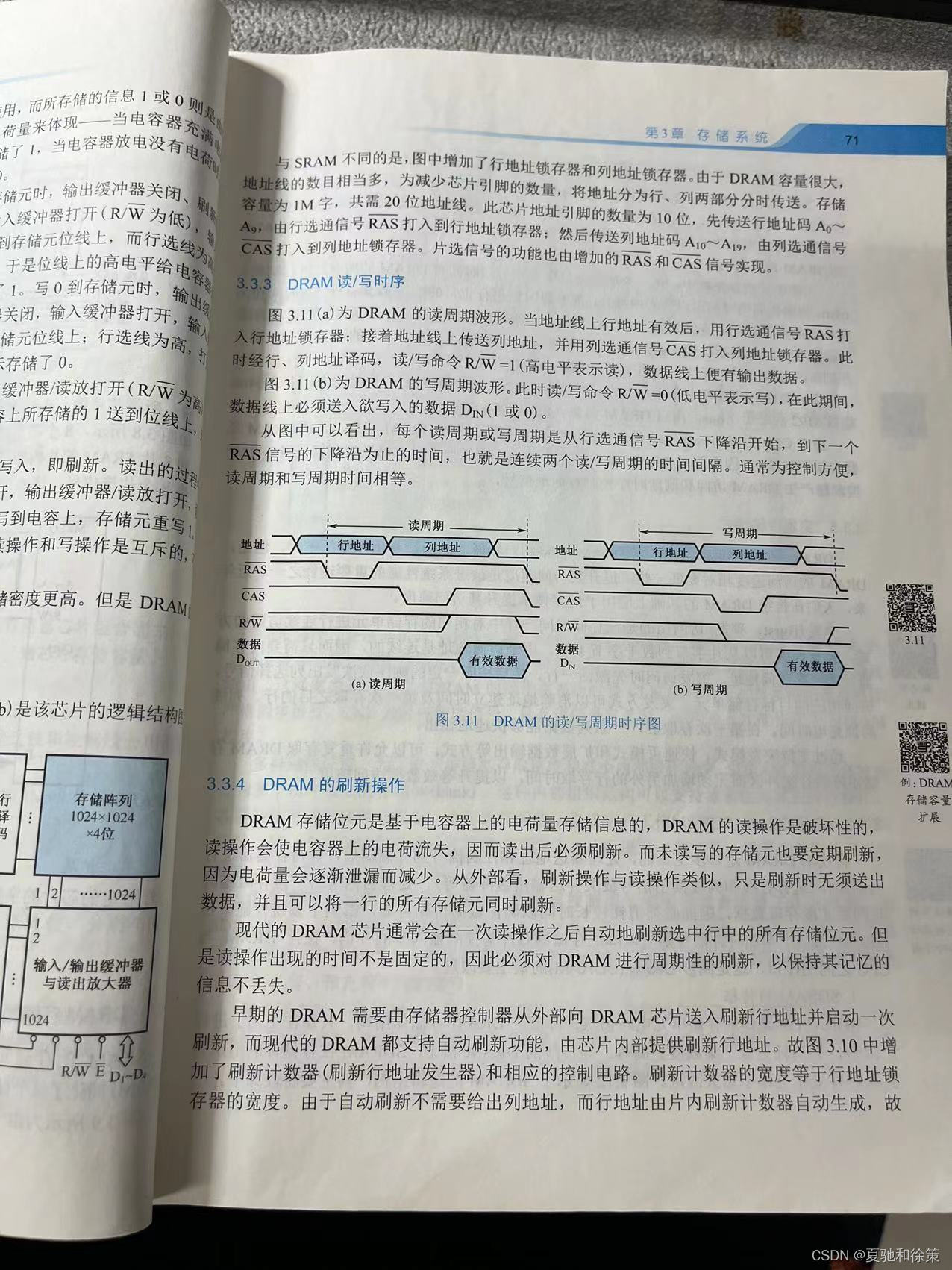

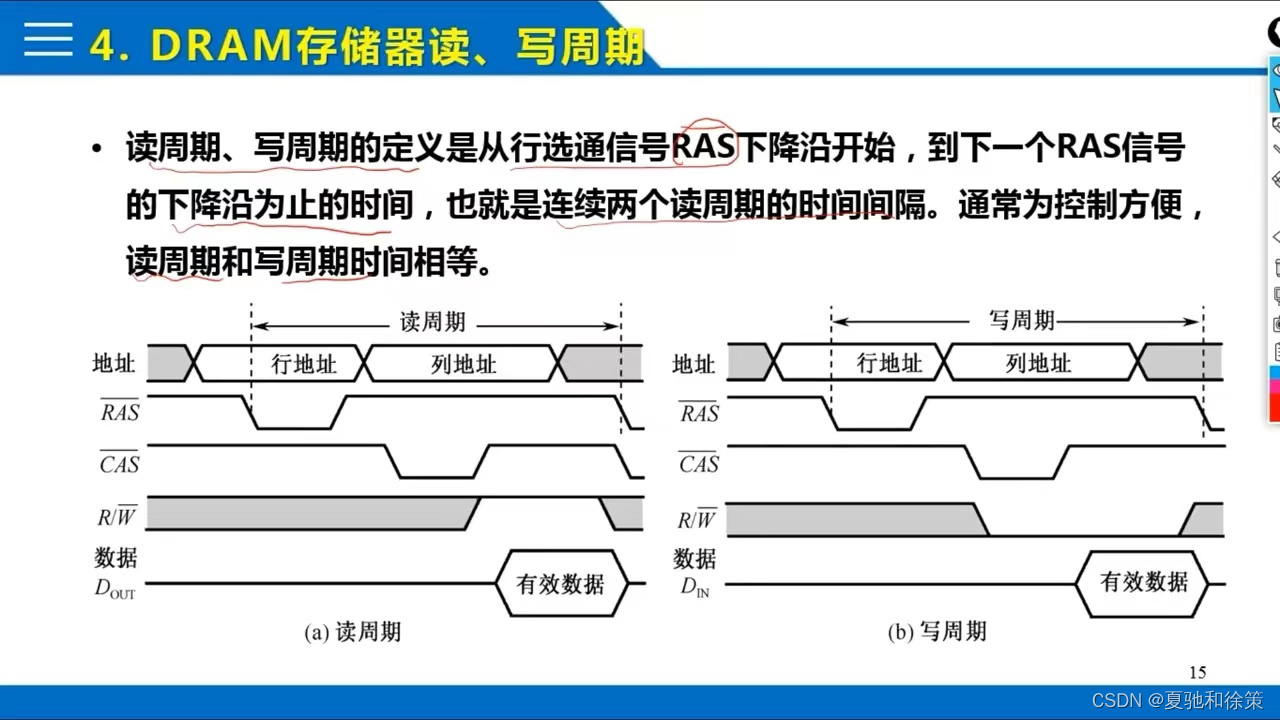

3.3.3 DRAM读/写时序

DRAM的读/写时序是指控制DRAM存储元进行读写操作时的时序规定。通常包括时钟脉冲的产生、地址信号的输入、数据的读写等过程。

在进行DRAM读操作时,首先需要给出一个读指令和相应的行地址和列地址。DRAM将指定行的所有存储元中的数据读出并预先放置到内部的读缓冲区。然后,在下一次时钟上升沿时,DRAM将数据从读缓冲区中输出并传输给CPU或其他外部设备。整个读操作需要一定的时序,包括行地址的输入时间、预充电时间、数据输出时间等。

在进行DRAM写操作时,首先需要给出一个写指令和相应的行地址和列地址。DRAM将指定行的所有存储元的内部存储单元置位待写,并将数据存储到写缓冲区中。在下一次时钟上升沿时,DRAM将写缓冲区中的数据写入到指定行的所有存储元中。整个写操作同样需要一定的时序,包括行地址的输入时间、预充电时间、数据输入时间等。

为了保证DRAM读/写时序的正确性,需要根据具体的DRAM芯片和外部控制器的规格书进行时序设计。常见的时序参数包括行选通延迟(tRAS)、行预充电时间(tRP)、列选通延迟(tCAS)、列写入延迟(tCWL)等。在实际的系统设计中,需要根据时序参数和时钟频率等因素综合考虑来确定DRAM的读/写时序。

3.3.4 DRAM的刷新操作

DRAM(Dynamic Random Access Memory)是一种动态随机存取存储器,其存储单元为存储电容器,需要定期刷新以防止电荷漏失。刷新规则是指在何时、何地、如何刷新DRAM存储器中的内容。

具体来说,DRAM存储器需要定期刷新其存储单元中的电荷,以保持数据的可靠性。刷新规则包括两种类型:基于时间的刷新和基于请求的刷新。

基于时间的刷新:DRAM存储器需要周期性地对存储单元进行刷新操作。这个周期称为刷新周期(Refresh Cycle),也就是DRAM存储器要多长时间才会对其中的数据进行一次刷新。在刷新周期中,DRAM存储器会按照预先设定的刷新顺序,依次对每个存储单元进行刷新操作。刷新周期的长度取决于DRAM存储器的工作频率和内部结构,通常为64ms至16ms之间。

基于请求的刷新:也称自适应刷新(Auto-Refresh),DRAM存储器在空闲时会检查存储单元的状态,如果有需要刷新的单元,则会进行刷新操作。基于请求的刷新方式能够减少刷新操作对系统性能的影响,但需要额外的控制电路来实现。

总体来说,刷新规则是DRAM存储器必须遵循的重要规定,对保证数据的可靠性具有重要作用。

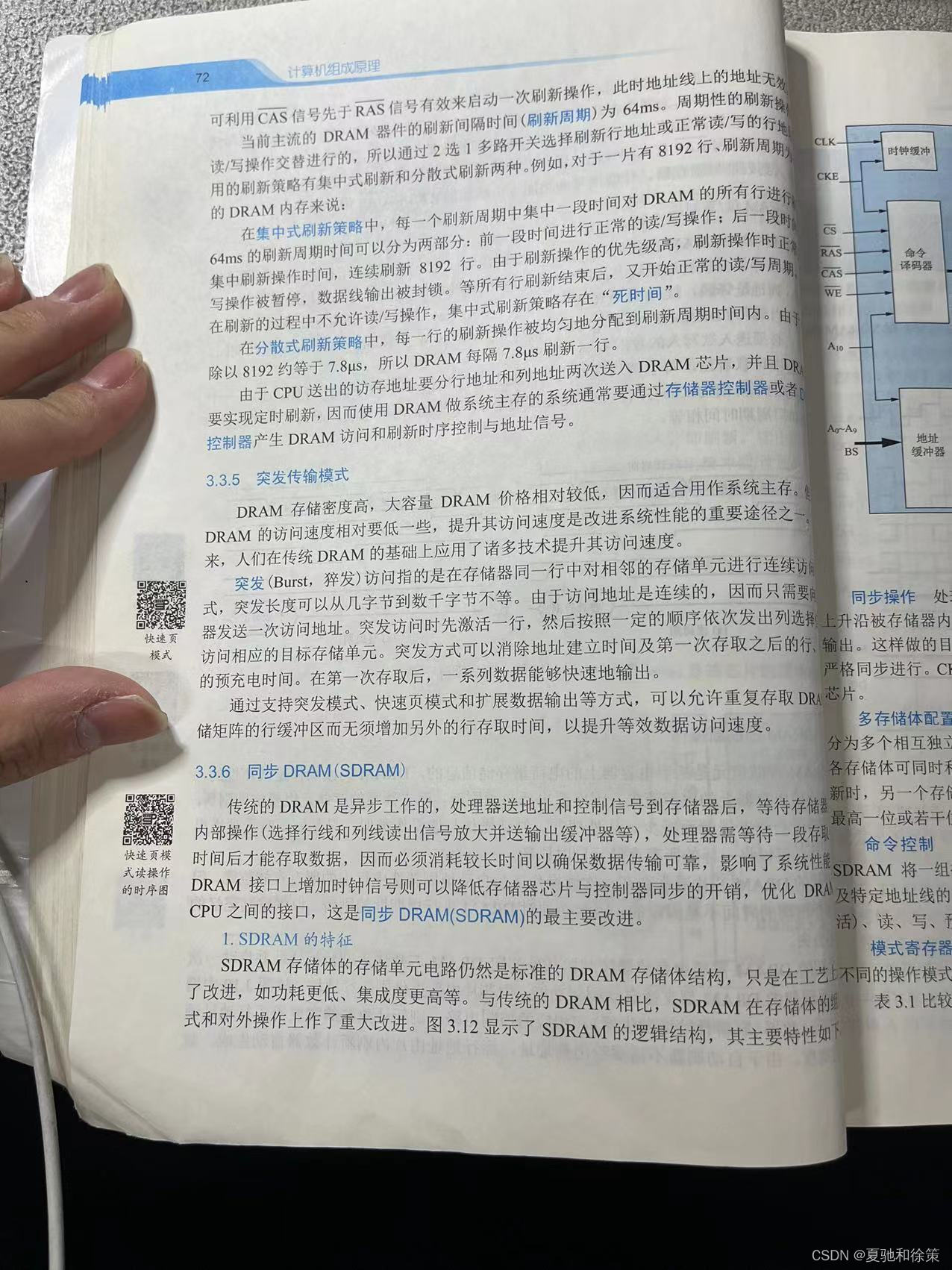

3.3.5 突发传输模式

突发传输模式(Burst Mode)是指在一次访问中连续地从DRAM存储单元中读取或写入多个数据。与传统的单个数据读/写相比,突发传输模式可以有效提高数据传输速率和系统性能,减少因频繁读/写单个数据而引起的延迟和功耗开销。

在突发传输模式下,DRAM芯片会自动连续输出或接收多个数据,因此不需要每个数据都进行读/写时序控制。突发传输模式的长度可以根据具体的实现进行设置,通常为4、8或16个数据。

在DRAM突发传输模式中,首先需要发送一个预充电命令(Precharge),将所有行预充电,为后续的读/写操作做好准备。然后,通过发送一个列地址和一个列地址有效命令(CAS)来选择一个列,并将该列中的多个数据连续输出或写入。最后,发送另一个预充电命令以清除该行,并进行下一次读/写操作。

需要注意的是,在突发传输模式下,DRAM芯片内部的自动刷新操作可能会干扰传输,因此需要特殊处理来保证稳定性。

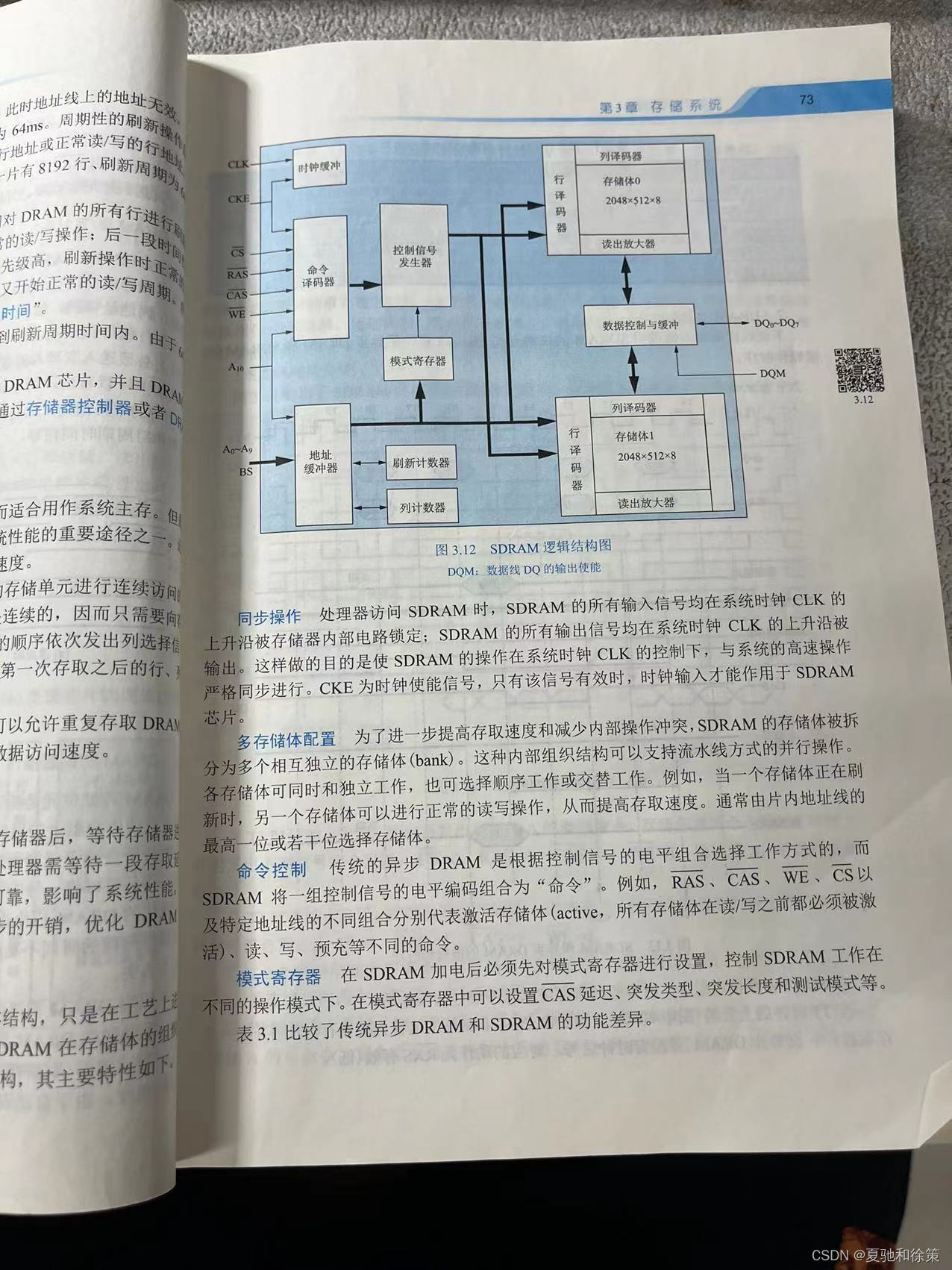

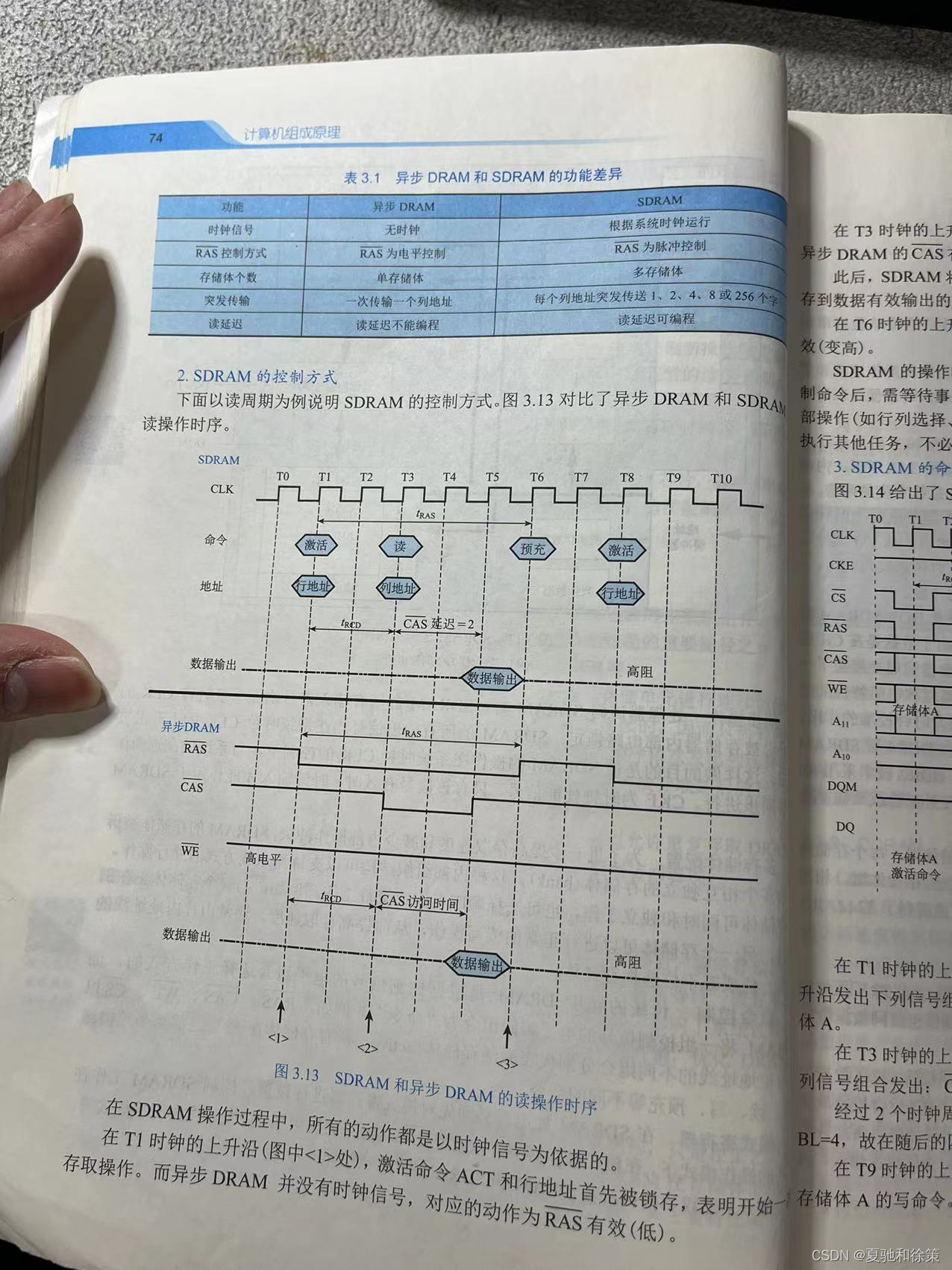

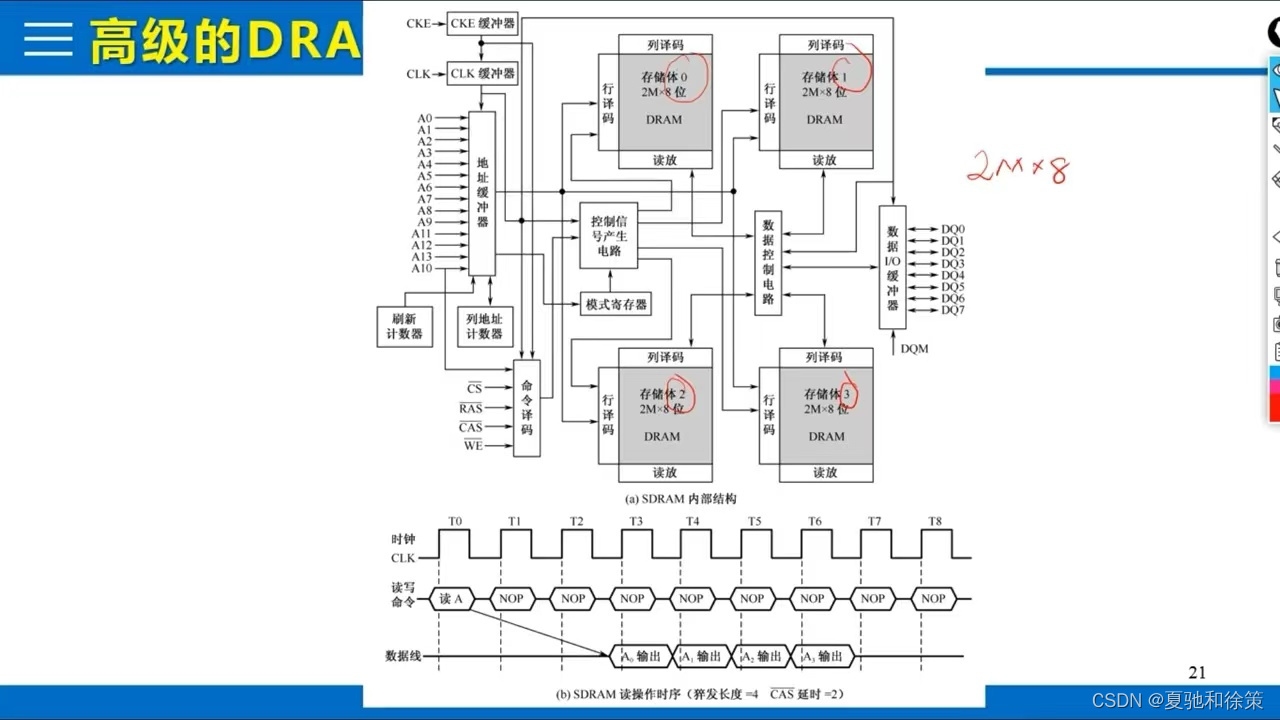

3.3.6 同步DRAM

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存取存储器)是一种内存芯片,它使用同步时钟信号来提高数据传输速率和效率。

与传统的DRAM不同,SDRAM在内部使用了一组复杂的控制和同步逻辑,以支持高速的读/写访问。这些逻辑包括一个内部时钟发生器,它用于在读/写访问期间生成时序信号;还有一个地址和命令管线,它用于加速命令和地址的传输。

SDRAM还使用了突发传输模式(burst mode),这意味着它可以在一次读/写命令中传输多个数据项,从而减少命令和地址信号的传输次数,提高传输效率。突发传输模式还可以减少对SDRAM总线的竞争,从而提高总线效率。

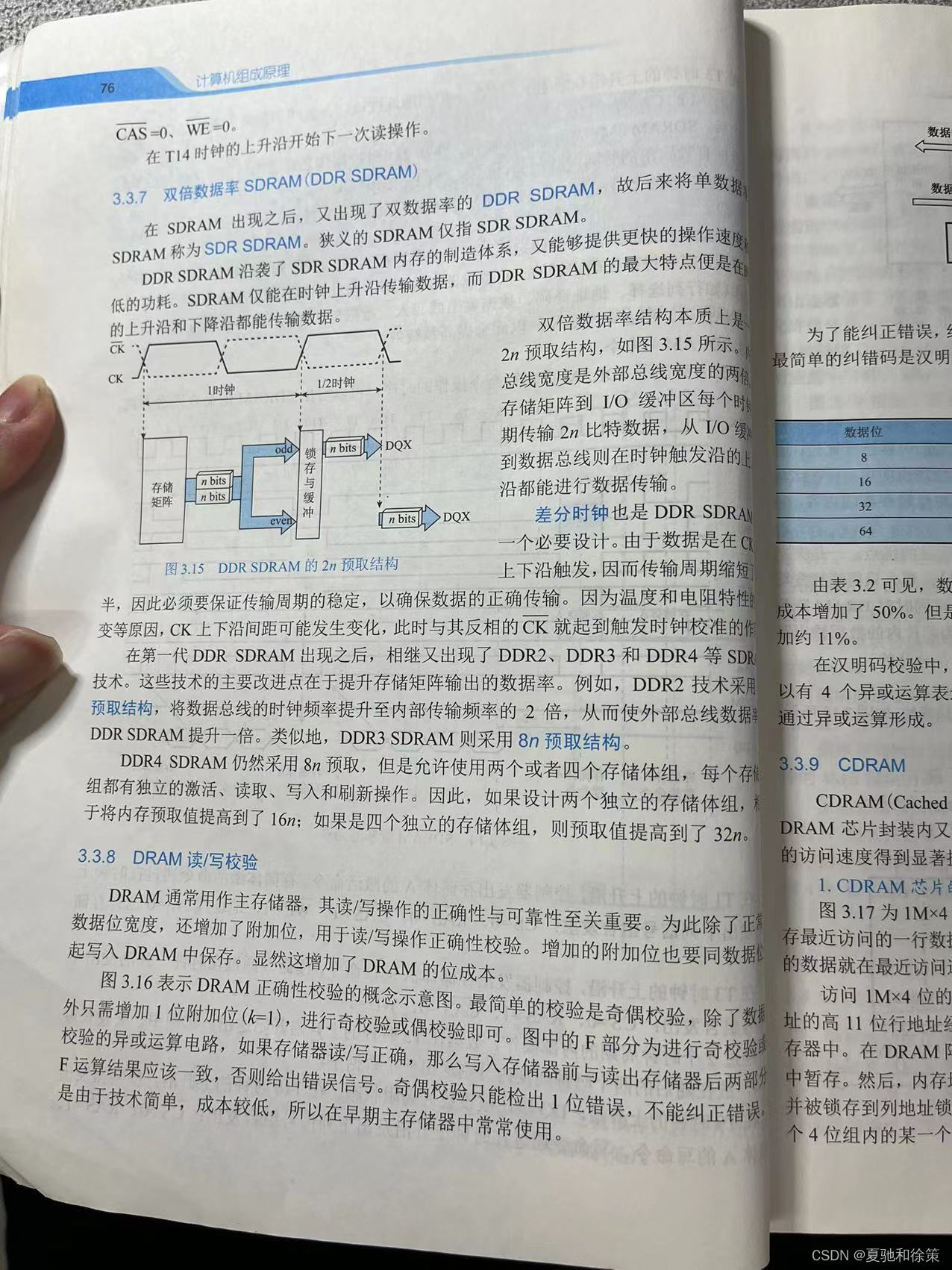

SDRAM也有不同类型的规格,例如DDR、DDR2、DDR3和DDR4等,它们具有不同的传输速率和时序要求,可以根据实际应用需求选择。

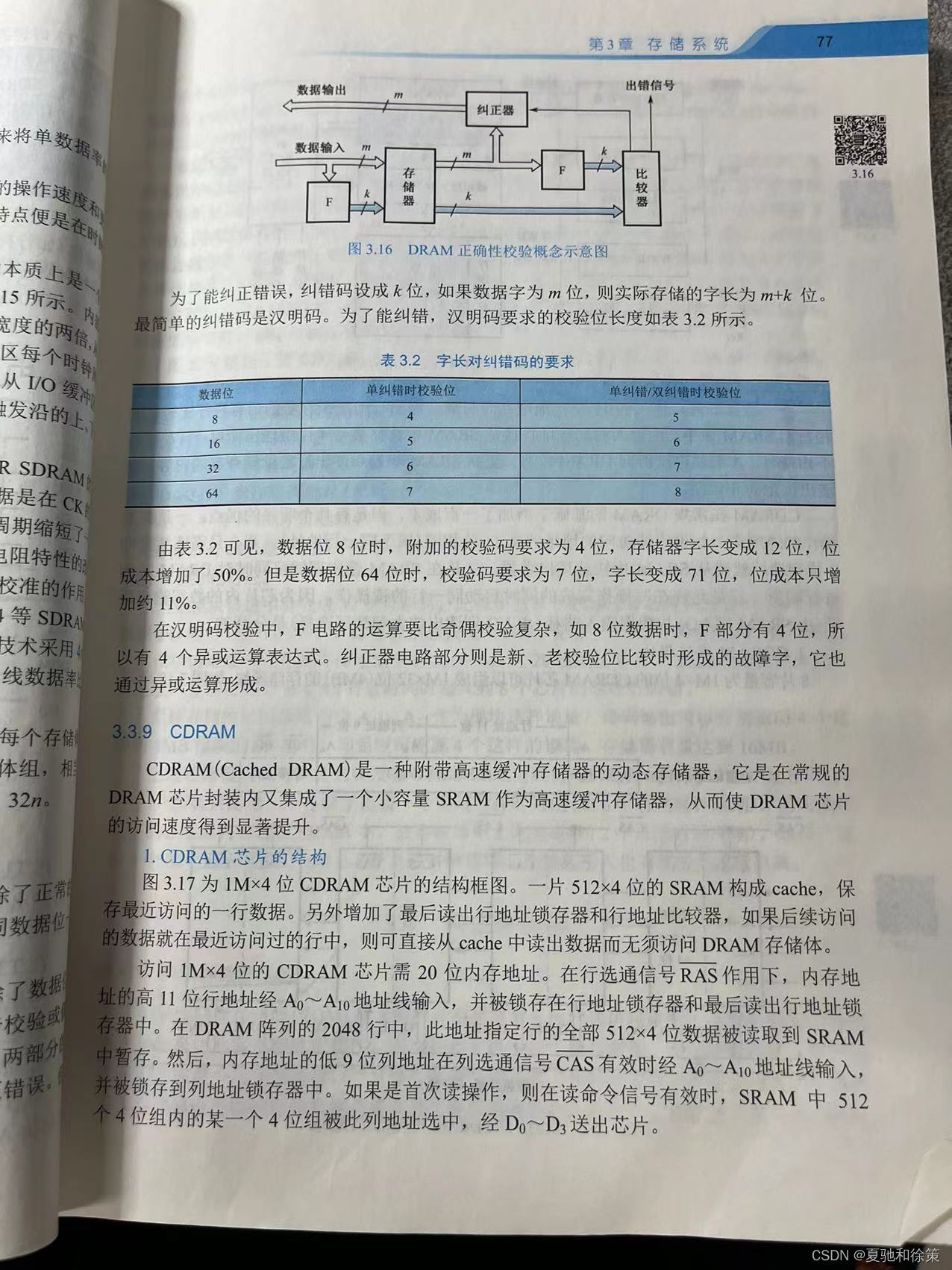

3.3.8 DRAM读/写校验

DRAM读写校验是一种用于检测DRAM读写操作是否正确的技术。由于DRAM存储单元的可靠性较低,可能会出现硬件错误,比如位翻转,而这些错误可能会导致程序崩溃或数据损坏。为了检测这些错误,DRAM读写校验技术会在DRAM读写操作完成后,对读取或写入的数据进行校验和计算,并将校验和与原始数据一起存储在另外的存储单元中。当需要使用这些数据时,系统会重新计算校验和,并将其与之前存储的校验和进行比较。如果校验和不匹配,就说明数据已经被修改或者存在硬件错误,需要进行相应的处理,比如重新读取或者报错提示。

常用的DRAM读写校验技术包括ECC(错误检测与纠正)和Parity(奇偶校验)等。ECC技术能够检测和纠正单个或多个比特的错误,它需要在存储器中额外存储一些纠错码(校验码),来检测和纠正存储单元中的错误。Parity技术则是通过将一个奇偶校验位添加到每个字节或字中,来检测和纠正单个比特错误。ECC技术通常比Parity技术更可靠,但是它也需要更多的存储空间和计算开销。

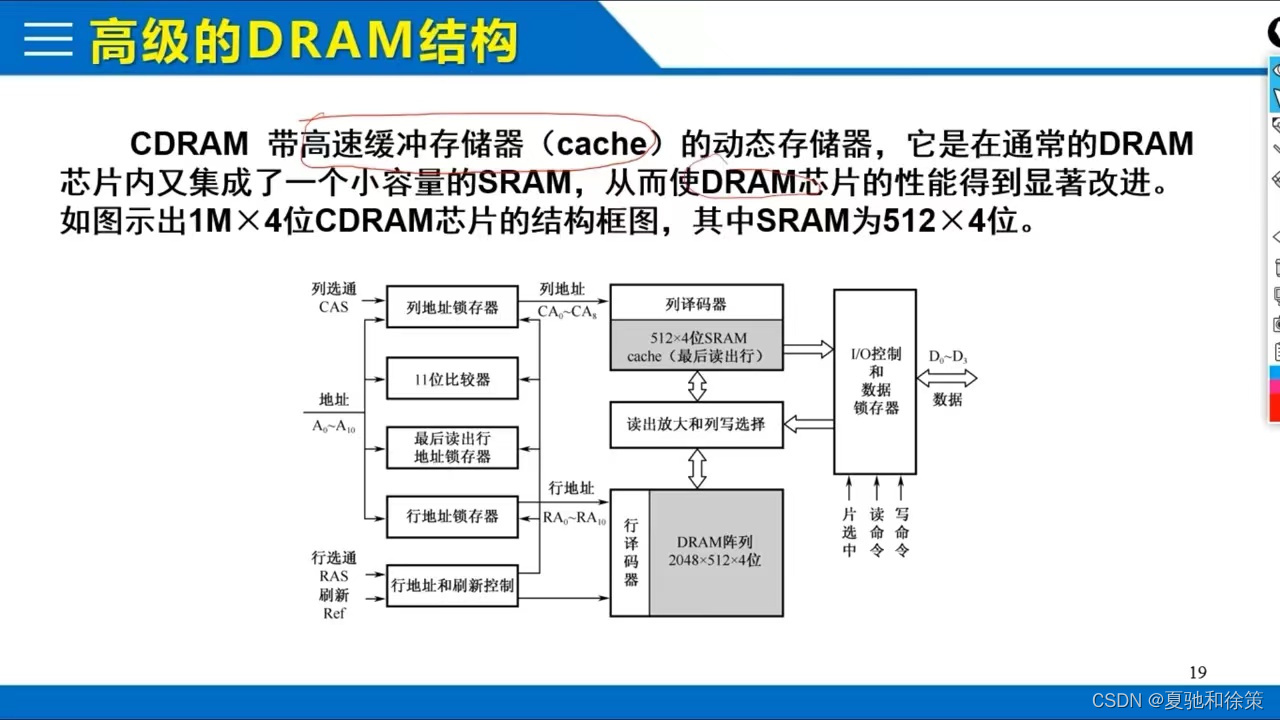

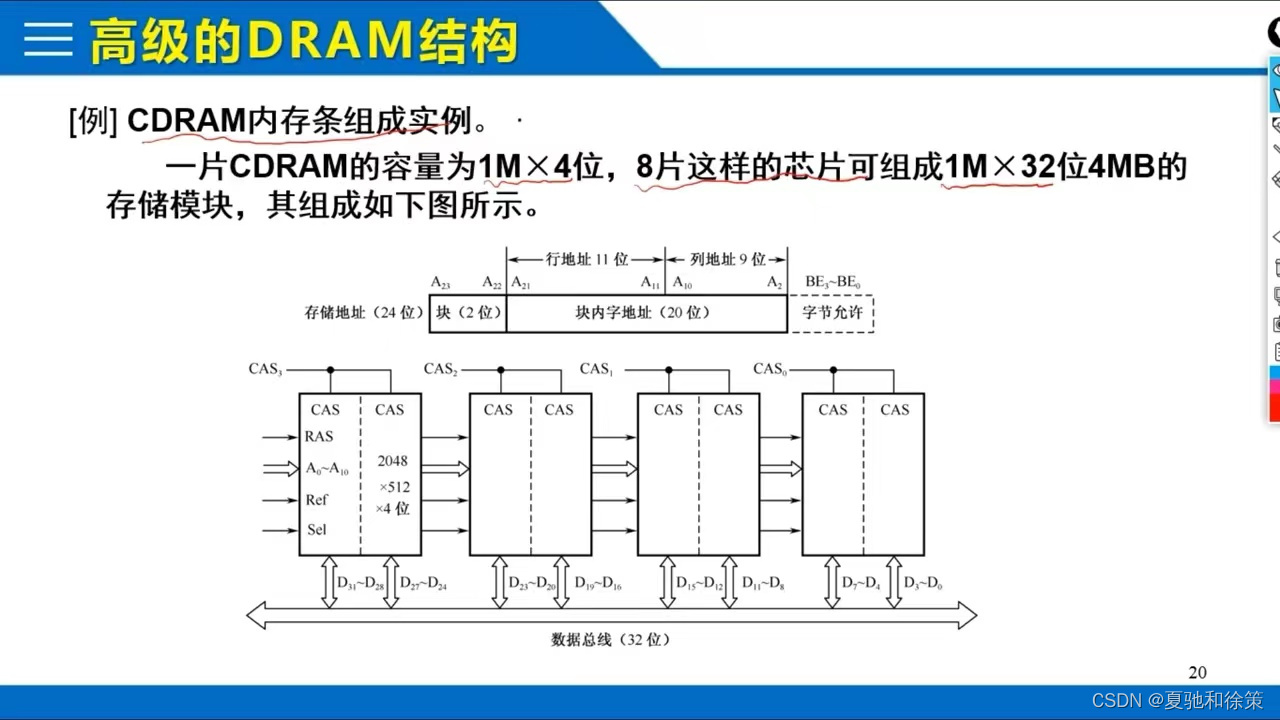

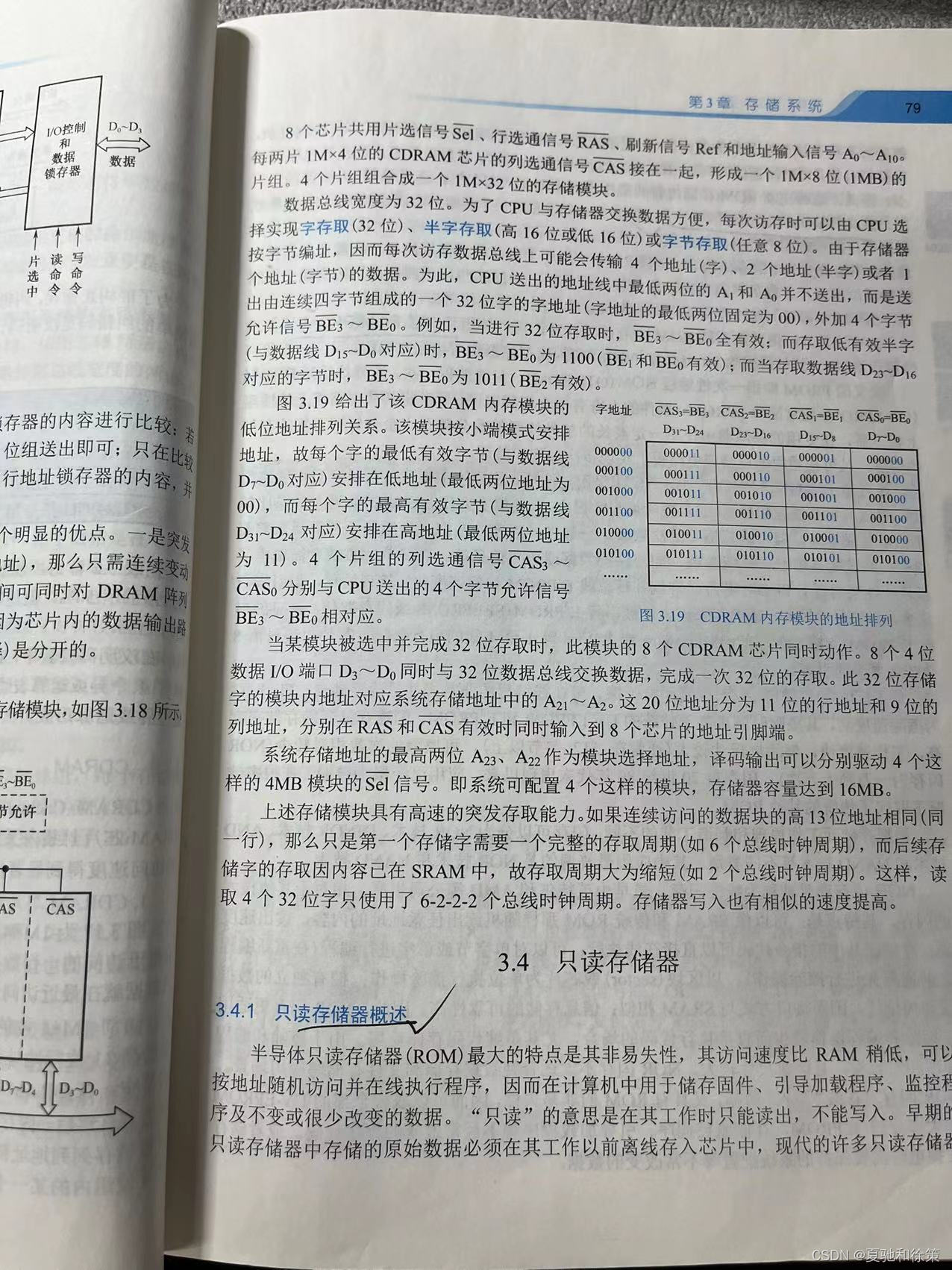

3.3.9 CDRAM

CDRAM是一种基于DRAM技术的存储器,其名称是“Cache DRAM”的缩写,它被设计用于高速缓存存储器中。与传统的DRAM不同,CDRAM使用了一种特殊的高速缓存控制逻辑,可以将常用的数据缓存到高速缓存中,以提高系统性能。以下是CDRAM的一些特点:

-

高速缓存:CDRAM具有内部高速缓存,可以存储常用数据,以加速读取速度。

-

数据预取:CDRAM可以在读取数据时同时预取下一个数据,以进一步加快访问速度。

-

高速数据传输:CDRAM支持高速数据传输,使得数据能够更快地传输到处理器。

-

缓存失效:当内部高速缓存无法命中时,CDRAM将自动读取主存中的数据并将其缓存到高速缓存中,以加快后续访问速度。

-

双倍速刷新:CDRAM支持双倍速刷新,可以加快DRAM的刷新速度,减少系统的延迟。

总的来说,CDRAM是一种高性能存储器,主要用于高速缓存存储器中。它具有高速缓存、数据预取、高速数据传输等特点,能够显著提高系统性能。

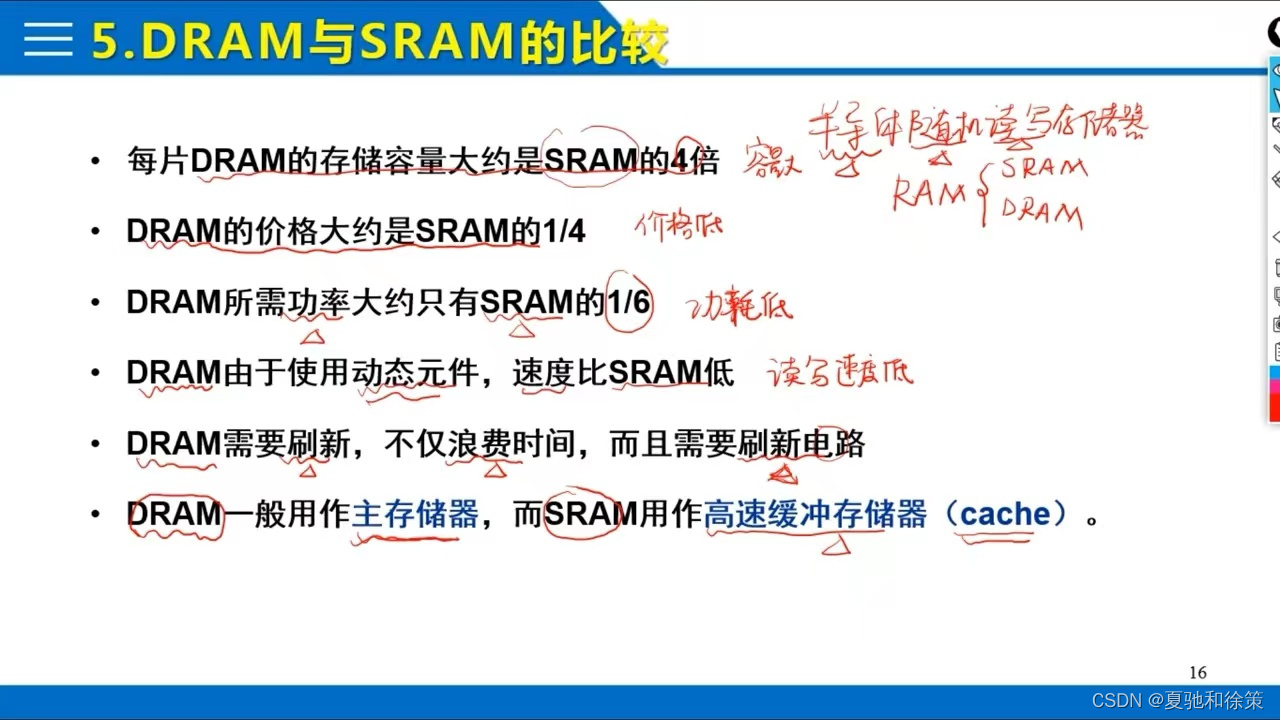

3.3.10 DRAM和SRAM的比较

DRAM(Dynamic Random-Access Memory)和SRAM(Static Random-Access Memory)是两种常见的存储器技术,它们在结构、性能和应用方面存在一些重要的区别。

1. 结构:DRAM的存储单元由电容和访问晶体管组成,而SRAM的存储单元由触发器电路组成。DRAM的存储单元结构相对简单,可以实现更高的存储密度,而SRAM的存储单元结构相对复杂,因此其存储密度较低。

2. 访问速度:SRAM的访问速度比DRAM快,因为SRAM的存储单元是通过触发器电路实现的,可以直接读取和写入数据,而DRAM的存储单元需要通过访问晶体管和电容来读取和写入数据,需要更多的操作步骤,因此速度较慢。

3. 成本:相对于DRAM,SRAM的制造成本较高。SRAM的存储单元结构复杂,需要更多的晶体管来实现,因此制造成本较高。而DRAM的制造成本相对较低,因为其存储单元结构简单,可以实现更高的存储密度。

4. 功耗:在相同的存储容量下,SRAM的功耗较高。SRAM使用的是触发器电路,需要持续的电流来维持存储状态,因此功耗较高。而DRAM使用的是电容存储数据,不需要持续的电流,功耗较低。

5. 刷新操作:DRAM需要定期刷新操作以保持数据的有效性,因为电容会逐渐泄漏,导致数据丢失。而SRAM不需要刷新操作,存储的数据可以长时间保持有效。

6. 应用领域:由于DRAM具有高存储密度和较低的成本,它广泛用于计算机内存和大容量存储系统。而SRAM由于其快速访问速度和稳定性,常用于高速缓存和低功耗的应用,如处理器高速缓存和嵌入式系统。

需要根据具体的应用需求来选择适合的存储器技术。如果需要高存储密度和较低的成本,可以选择DRAM;如果需要快速访问速度和稳定性,可以选择SRAM。

总结:

动态随机存储器(DRAM)是计算机中最常用的内存类型之一,其工作原理和结构与静态随机存储器(SRAM)有所不同。以下是DRAM学习中的重点和难点和易错点的总结:

重点:

- DRAM存储元的工作原理和逻辑结构。

- DRAM的读/写时序和刷新规则。

- 突发传输模式和如何提高DRAM的数据传输效率。

- SDRAM和DDR SDRAM的特点和区别。

难点:

- DRAM存储元的内部电荷如何被读取和写入。

- DRAM的刷新规则和如何在刷新时保持数据的可靠性。

- DRAM的读写时序的复杂性和如何进行时序分析和优化。

- 如何解决DRAM的存储密度和功耗之间的矛盾。

易错点:

- 配置DRAM时序参数时的错误。

- 配置DRAM时传输模式和频率的错误。

- DRAM刷新规则和刷新周期的错误配置。

- DRAM的数据传输错误和数据完整性问题。

了解和掌握以上重点和难点以及避免易错点,将有助于更好地理解和应用DRAM技术。

1082

1082

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?