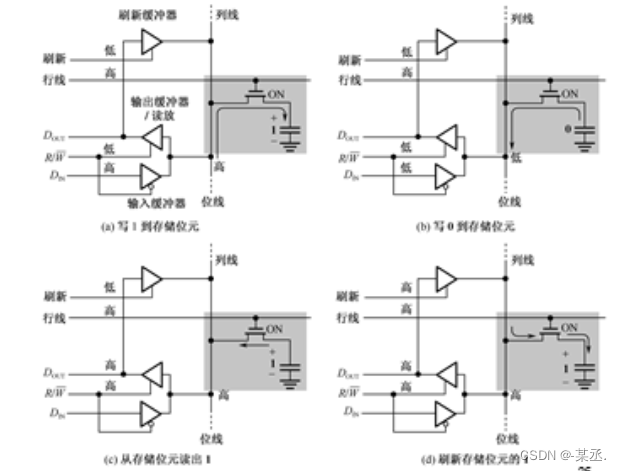

1.DRAM存储源的工作原理

SRAM的存储元是一个触发器,它具有两个稳定的状态,而动态随机存取存储器(DRAM)简化了每个存储元的结构,因而DRAM的存储密度很高,通常用作计算机的主存储器。

读出过程破坏了电容上存储的信息,所以要把信息重新写入即为刷新。读出的过程中可以完成刷新。

注意输入缓冲器与输出缓冲器总是互锁的,这是因为读操作和写操作是互斥的,不会同时发生。

与SRAM相比,DRAM的存储元所需元件更少,所以储存密度更高。但是DRAM的附属电路比较复杂,访问时需要额外的电路和操作支持。

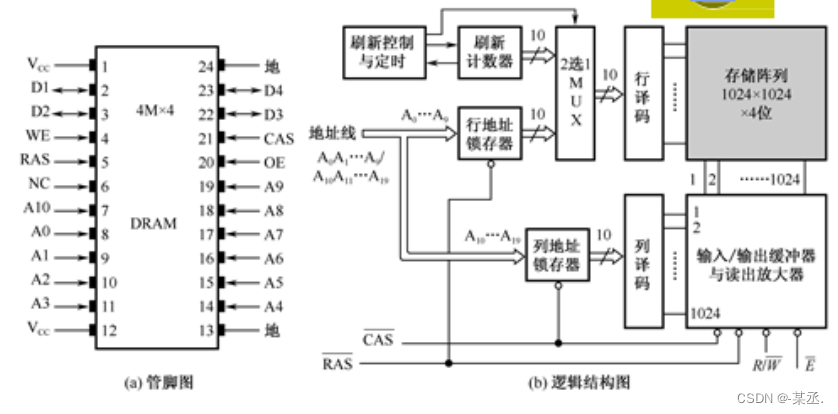

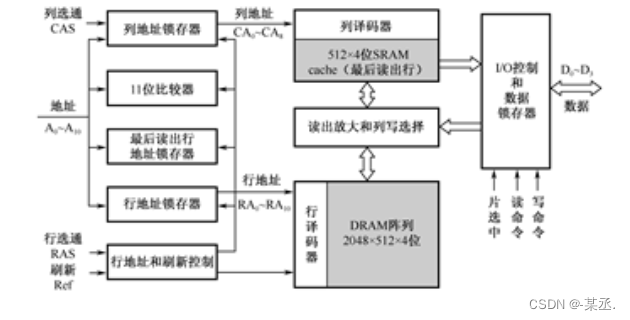

2.DRAM芯片的逻辑结构

与SRAM不同的是图中增加了行地址锁存器和列地址锁存器。由于DRAM容量很大,地址线的数目相当多,为减少芯片引脚的数量,将地址分为行、列两部分分时传送。(时分复用)

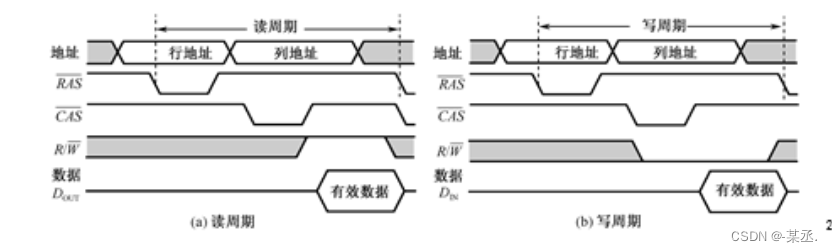

3.DRAM读/写时序

每个读周期或写周期是从行选通信号RAS非下降沿开始,到下一个RAS非信号的下降沿为止的时间,也就是连续两个读/写周期的时间间隔。通常为控制方面,读周期和写周期时间相等。

4.DRAM 的刷新操作

DRAM存储位元是基于电容器上的电荷量存储信息的,DRAM的读操作是破坏性的,读操作会使电容器上的电荷流失,因而读出后必须刷新。而未读写的存储元也要定期刷新,因为电荷量会逐渐泄漏而减少。从外部看,刷新操作与读操作类似,只是刷新时无法送出数据,并且可以将一行的所有存储元同时刷新。

在集中式刷新策略中,每一个刷新周期中集中一段时间对DRAM的所有行进行刷新。

在分散式刷新策略中,每一行的刷新操作被均匀的分配到刷新周期时间内。

由于CPU送出的访存地址要分行地址和列地址两次送入DRAM芯片,并且DRAM还要实现定时刷新,因而使用DRAM做系统储存的系统通常要通过存储器控制器或者DRAM控制器产生DRAM访问和刷新时序控制与地址信号。

预冲:下次访问的数据不在此次访问的行中,需要关闭当前行,另选行地址,这一过程叫做预冲。

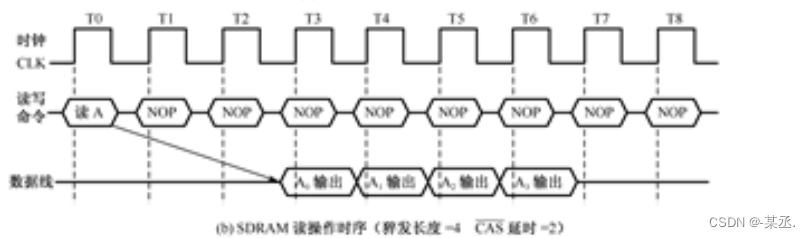

5.突发传输模式

突发访问指的是在存储器同一行中对相邻的存储单元进行连续访问的方式,突发长度可以从几字节到数千字节不等。

突发方式可以消除地址建立时间及第一次存取之后的行、列线的预充电时间。

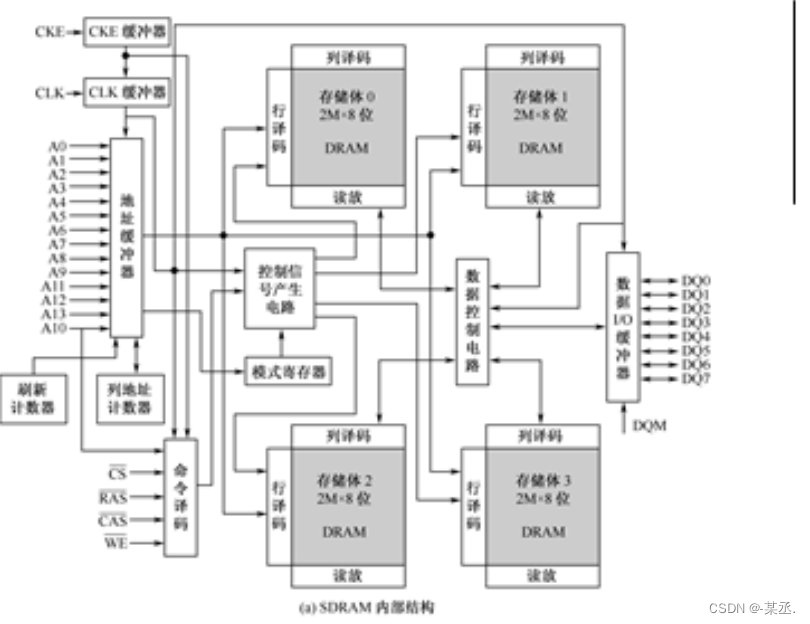

6.同步DRAM(SDRAM)

1)SDRAM的特征

同步操作(时钟信号)

多存储体配置(可在不同的存储体上同时读写)

命令控制(由CPU中的CU所发出的命令)

模式寄存器

2) SDRAM的控制方式

3)SDRAM的命令

7.双倍数据率SDRAM(DDR SDRAM)

双倍数据率 SDRAM 即 DDR SDRAM ,在时钟的上升沿和下降沿都能传输数据,能够提供更快的操作速度和更低的功率。

DDR SDRAM 之后,相继又出现了DDR2、DDR3和DDR4等 SDRAM 技术。

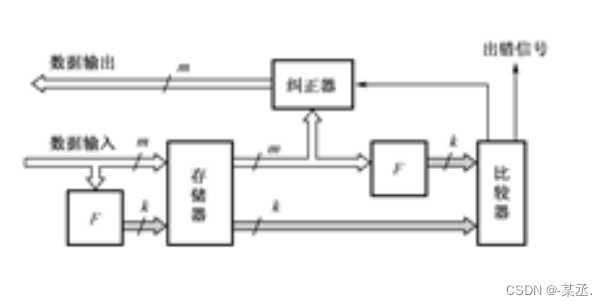

8.DRAM读/写校验

DRAM 通常用做主存储器,其读写操作的正确性与可靠性至关重要。为此除了正常的数据位宽度,还增加了附加位,用于读/写操作正确性校验。增加的附加位也要同数据位一起写入 DRAM 中保存。其原理如图所示。

9.CDRAM

CDRAM(Cached DRAM)是一种附带高速缓冲存储器的动态存储器,它是在常规的DRAM芯片封装内又集成了一个小容量SRAM作为高速缓冲存储器,从而使DRAM芯片的访问速度得到显著提升。

589

589

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?