根据Dvm-gli的博客(彬哥的论坛),彬哥的串口发送程序在用户需要连续进行数据发送时,使用起来不方便,因为每发送一个数据,都要给出一个相应的发送脉冲。这时可以在用户和uart_transfer之间加入一个fifo模块,用户只需要把要发送的数据写入fifo,自动由uart_transfer模块进行发送,这样使用上方便一些。

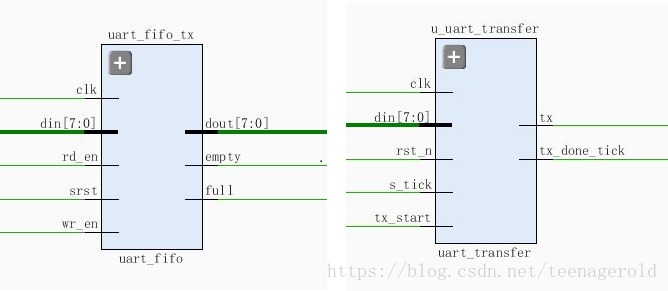

主要端口如下,

需要注意的信号有两个,一个是uart_transfer在什么时候去读取fifo_tx,另外一个是什么时候给uart_fifo传送tx_start(发送使能)信号。

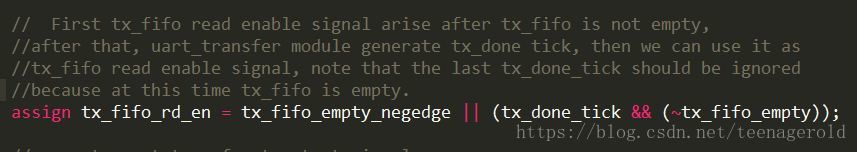

对于fifo_tx的读取使能rd_en,我们这样处理:(1)在fifo_tx不为空的时候,empty会有一个从高电平到低电平的跳变,我们使用下降沿检测电路作为首个rx_en的使能信号。(2)接下来,数据从fifo_tx的dout引脚输出,接入uart_transfer的din引脚,给出发送使能信号tx_start,发送完成后产生tx_done_tick发送完成脉冲信号,以后我们就使用tx_done_tick作为fifo_tx的读取使能信号rd_en。需要注意的是在最后一个数据从fifo_tx输出后,empty拉高,fifo_tx此时已空,那么最后一个tx_done_tick产生时fifo_tx早已空,故最后一个tx_done_tick不能使用。综上,我们可以得出fifo_tx的读取使能信号rd_en的产生形式如下:

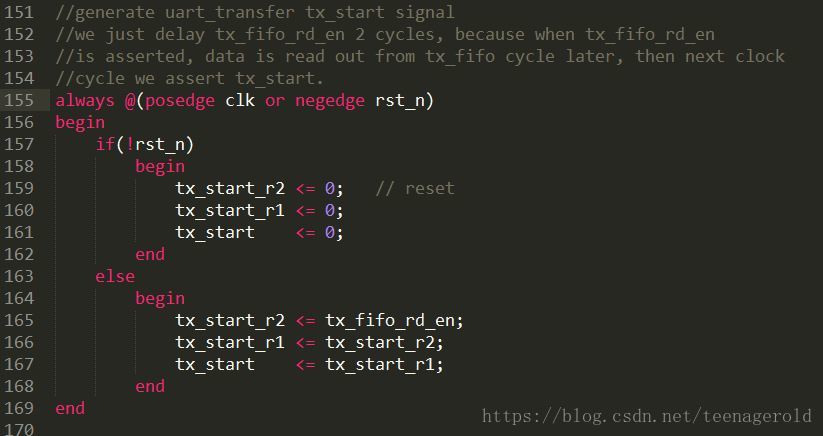

对于串口发送模块的发送使能信号tx_start,根据Xilinx的FIFO IP核文档的描述,在rd_en信号为高的的下一个时钟周期,数据从dout输出。为了使数据在tx_start使能信号有效前稳定下来,我们将rd_en信号打慢两拍,作为tx_start信号。

给串口模块加入FIFO

最新推荐文章于 2024-03-05 14:51:04 发布

1182

1182

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?