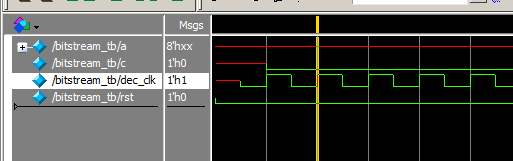

变量(reg)在全局reset时未初始化,

工作之后终于知道有专门一个名词叫作x propagation

仿真和实际上板跑有一个区别是仿真时未初始化的变量在波形里是红色的x,实际上板跑的时候是不会有这种信号。导致上板结果和仿真不一致。

在实际调试时发现未初始化的变量在全局reset时并不一定是低电平的0,原因是程序中很多代码不依赖reset就已经开始跑了,

最简单的例子

always @ (posedge clk)

a <= b;

在未reset之前,a就依赖b而动了,在reset时a可能不是低电平的0了。

有些状态机在未reset时就已经往下跑了,开始状态迁移了,所以最好的设计是在reset之前状态机保持不动。

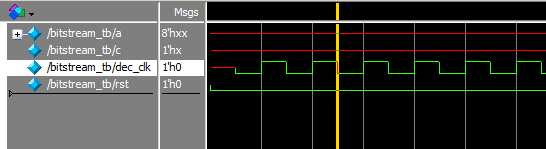

if (a==30)

c <=1;

else

c <= 0;

if(a!=30)

c <= 1;

else

c <= 0;

如果a是x,这两个判断都走else分支,c结果都是0

`timescale 1ns / 1ns // timescale time_unit/time_presicion

module bitstream_tb;

reg rst;

reg dec_clk;

initial begin

rst = 0;

#50 rst = 1;

#1 rst = 0;

end

always

begin

#1 dec_clk = 0;

#1 dec_clk = 1;

end

reg signed [7:0] a;

wire signed [7:0] b;

reg c;

always @ (posedge dec_clk) begin

if (a==8'h30)

c <= 1;

else

c <= 0;

end

endmodule

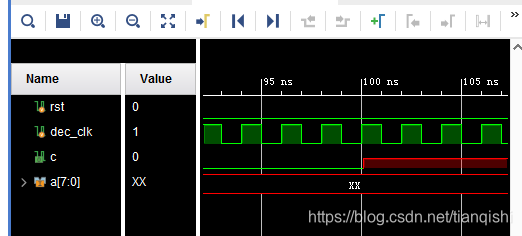

vivado PostSynthesis仿真时,结果有点不一样,100ns之前c是0,之后就是X了

c <= a?1:0 这样,问号代替if,结果a为x,c也为x

Conditional Operator ?:

Operates like the C statement I conditional expression ? true expression : false expression ;

The conditional expression is first evaluated

If the result is true, true expression is evaluated

If the result is false, false expression is evaluated

If the result is x:

both true and false expressions are evaluated,...

their results compared bit by bit,...

returns a value of x if bits differ, OR...

the value of the bits if they are the same.

This is an ideal way to model a multiplexer or tri-state buffer.

`timescale 1ns / 1ns // timescale time_unit/time_presicion

module bitstream_tb;

reg rst;

reg dec_clk;

initial begin

rst = 0;

#50 rst = 1;

#1 rst = 0;

end

always

begin

#1 dec_clk = 0;

#1 dec_clk = 1;

end

reg [7:0] a;

reg b;

reg c;

always @ (posedge dec_clk) begin

c <= a?1:0;

end

endmodule

1241

1241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?