数据与位宽不匹配,数据长则舍弃最高位,位宽大则前面补0

0 1 z(高阻态) x(未知状态)

wire 线连接

reg 寄存器(always组合逻辑只能用reg)

=阻塞赋值 ,执行结束之后才执行下面语句

<=非阻塞赋值

归约运算 是第一步先用操作数的第一位和第二位进行位操作,然后再用第一步的结果和操作的数的下一位 进行位操作,如此重复直到最后一位。

将8bit的a、3bit 的 b、5bit的c按顺序拼接成一个16位的d,表示方法为: d = {a, b,c}:

时间单位和时间精度由值1、10、和100以及单位s、ms、us、ns、ps 和fs组成。

1s = 1000ms 1ms = 1000μs 1μs = 1000ns 1ns = 1000ps

#10 代表延时10个时间单位

时间精度:决定时间相关量的精度及仿真显示的最小刻度。

'timescale 1ns/10ps精度0.01,#10.11表示延时10110ps。

系统函数

打印输出

$display 可以自动换行

$write 需要写换行符 \n

$strobe 只能最后执行

$monitor 检测变量变化,只有变化才能打印

时间函数

$time返回时间

$random 返回随机数

$readmemb用于读二进制文件函数

$readmemb ("<数报文件名>",<存贮器名>); 把数报文件名赋给存贮器

$readmemh 用于读十六进制文件函数

向量表示 : reg [7:0] count

一维数组表示 : reg count [7:0] (默认每个元素位宽为一)

reg [7:0] count [3:0] 4个位宽为8元素的一维数组

二维数组 :reg [7:0] count [3:0][3:0] 可以看作矩阵

奇、偶分频

偶分频

module divider_six

#(

parameter CNT = 2'd2)

(

input wire sys_clk ,

input wire sys_rst ,

output reg clk_out

);

reg [1:0] cnt;//012

//reg cnt_flag;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

cnt=2'b0 ;

else if(cnt==CNT)

cnt=2'b0 ;

else

cnt=cnt+2'b1 ;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

clk_out=1'b0 ;

else if(cnt==CNT)

clk_out= ~clk_out ;

else

clk_out= clk_out ;

endmodule奇分频 1、数到5,cnt_flag标志

2、奇分频,上升沿下降沿各一次,然后两个结果或运算

always@(posedge sys_clk or negedge sys_rst)

always@(negedge sys_clk or negedge sys_rst)

x<<n使用的是逻辑移位运算符,其对包括符号位在内的所有位进行移位操作;(乘除法)

x<<<n使用的是算术移位运算符,其只对非符号位的进行移位操作,而符号位保持不变。

4’b1001<<1 = 5’b10010;

4’b1001<<2 = 6’b100100;

1<<6 = 32’b1000000;

4’b1001>>1 = 4’b0100;

4’b1001>>4 = 4’b0000;

逻辑左移(<<):低位补0

逻辑右移(>>):高位补0

算数左移(<<<):低位补0

算数右移(>>>):对于有符号数,高位补符号位;对于无符号数,高位补0

下降沿、上升沿寻找,除了打一拍之外的操作

//寻找busy的下降沿

reg [1:0] busy_reg;

wire busy_neg;

always@(posedge CLK_OUT or negedge sys_rst)

if(sys_rst == 1'b0)

busy_reg<=2'd0;

else

busy_reg<={busy_reg[0] , busy};

assign busy_neg=(!busy)&busy_reg[0];wire read_done;

reg [1:0] read_done_reg;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

read_done_reg<=2'd0;

else

read_done_reg<={read_done_reg[0],read_done};

assign read_done_pos=(!read_done_reg[0])&read_done;以太网

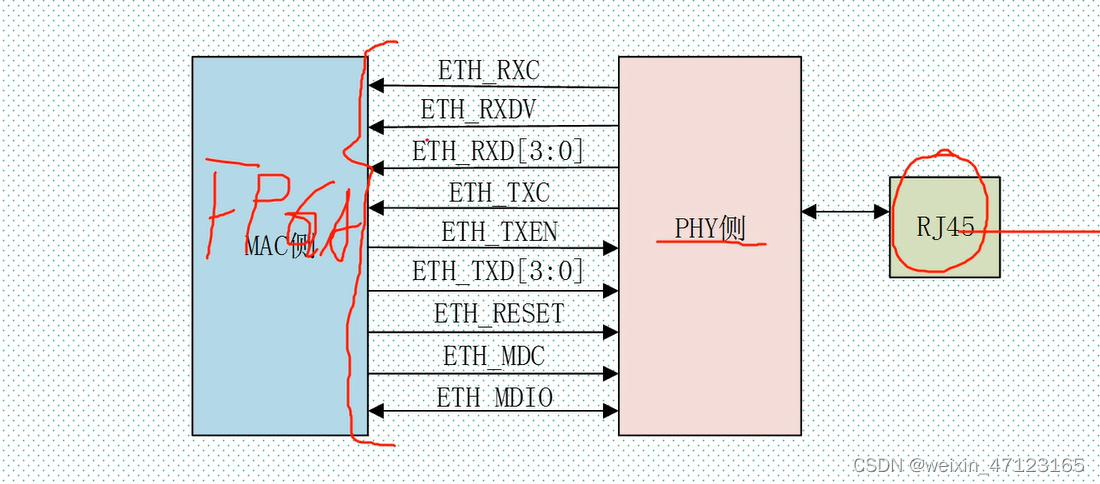

发送数据时钟,先发送低位,再发送高位,4位4位的发送;接收时序也是一样;

关于txc核rxc的时钟是根据开发板的通信速率/4得到的,因为一个时钟传4位

8636

8636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?