Camera DVP协议讲解

- 该文章写于2016年,一直未发表。近期工作中又涉及到了Camera相关的内容,重新温习了下相关知识。决定把这篇文章发表出来,大家共同学习。

DVP(Digital Video Port)摄像头数据并口传输协议,提供8-bit或10-bit并行传输数据线、HSYNC(Horizontal sync)行同步线、VSYNC(Vertical sync)帧同步线和PCLK(Pixel Clock)时钟同步线。8-bit或10-bit是依Pixel的位深而定的,8bit A/D Pixel位深8bit,10bit A/D Pixel位深10bit。具体提供8bit还是10bit数据线依Sensor而定,有的Sensor虽有10bit数据线(D0–D9),但接线时一般只接高8位(D2–D9),舍弃低2位的原因是对图像效果影响并不大。有的平台也有10bit数据线,接线时也得区分是高8位(D2–D9)还是低8位(D0~D7),并与软件解析相对应,不能是硬件接了低8位,而软件仍按高8位解析数据(出现粉红屏),或者反过来也是不允许的(出现高亮发红)。

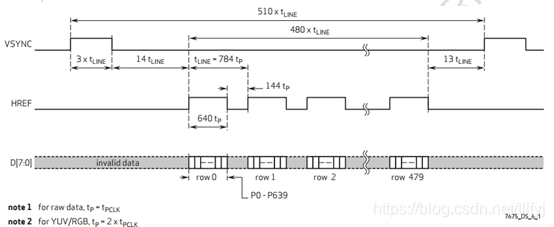

DVP接口一个PCLK周期可以传输1byte数据,1byte各位并行输出,一行Pixel输出完后,Sensor输出一个HSYNC行同步信号,一帧所有行输出完成后,输出一个VSYNC帧同步型号。如图4.3-1是一个输出VGA大小的示例时序图,HREF便是HSYNC,3xtLine是VB(Horizontal Blank Dummy Line)帧空闲时间,14tLine是帧头与第一行第一个Pixel数据开始的时间St,640tp表示一行有640个Pixel,然后HSYNC变为低电平,144tp是HB(Horizontal Blank Dummy Pixel)行空闲时间,13tLine是最后一行最后一个Pixel到帧尾的时间Et,510xtLine是一帧的时间。

510xtLine=3tLine+14tLine+480tLine+13tLine,480tLine=(640tp+144tp)x480-144tp。

HB、VB、St、Et时间一般有寄存器可以进行设置,St、Et一般很少动采用默认值即可,HB、VB决定了Sensor输出的最大帧率,HB、VB也不是可以无限小的,需要大于某个最小值,值太小图像边缘会出现花边。HSYNC、VSYNC可以在低电平输出有效数据,也可以在高电平输出有效数据,PCLK可以上升沿出数据也可以下降沿出数据,Sensor一般都开放了寄存器来设置HSYNC、VSYNC、PCLK的极性,极性设置应该与平台抓数据时采用的极性相一致,如VSYNC、HSYNC极性错误会引起黑屏,PCLK极性错误会引起花屏。DVP接口是靠HSYNC、HSYNC中断信号检测有效帧的,Data线发生错位、开路、短路、相位差,并不会引起出不了图像,只是图像不正常而已,越高位的Data线出问题花屏就越严重,D7>D6…>D1>D0。

PCLK、D0、D1都是高频信号线(低位变化更加频繁),Layout时注意屏蔽干扰、不可与其它高频线并排或重叠走线,最好用GND线或者低频线(如D7、D6)隔开。

本文详细介绍了DVP摄像头数据并口传输协议的工作原理和技术细节,包括8-bit或10-bit并行传输数据线、HSYNC行同步线、VSYNC帧同步线和PCLK时钟同步线的作用及配置方法。此外,还探讨了传感器输出的有效帧检测机制以及PCLK、D0、D1等高频信号线的布局注意事项。

本文详细介绍了DVP摄像头数据并口传输协议的工作原理和技术细节,包括8-bit或10-bit并行传输数据线、HSYNC行同步线、VSYNC帧同步线和PCLK时钟同步线的作用及配置方法。此外,还探讨了传感器输出的有效帧检测机制以及PCLK、D0、D1等高频信号线的布局注意事项。

1811

1811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?