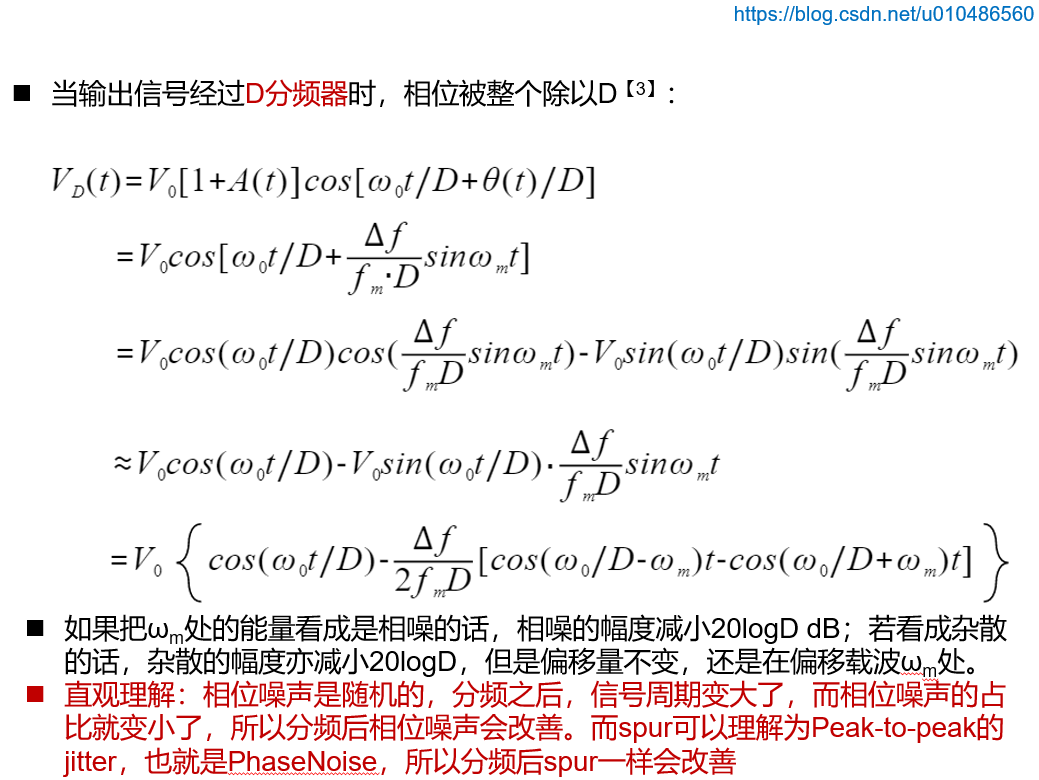

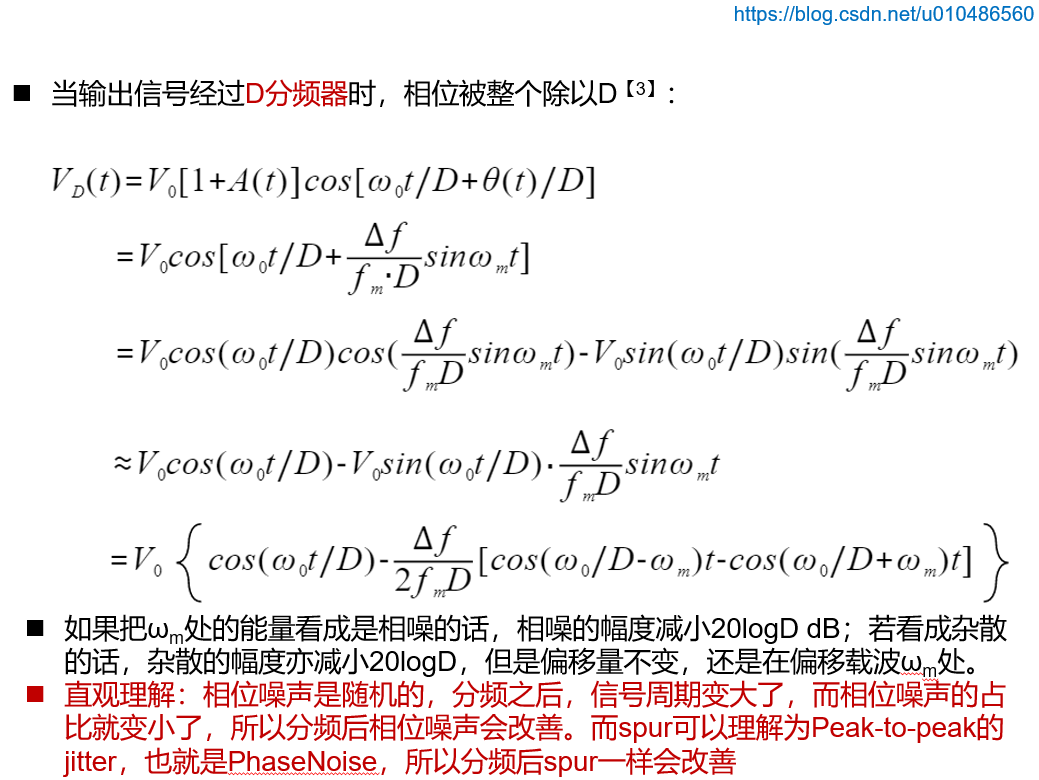

当VCO的输出信号通过D分频时,其相噪下降20log10(D);杂散幅度亦下降20log10(D),但频率偏移量(offset frequency)保持不变,即每2分频,改善6dB,而倍频则相反,由此在PLL测试Phase noise时,尽量不要分频或倍频,保持原有信号。

VCO输出端的分频器对相噪和杂散的影响

于 2021-07-30 00:38:20 首次发布

当VCO的输出信号通过D分频时,其相噪下降20log10(D);杂散幅度亦下降20log10(D),但频率偏移量(offset frequency)保持不变,即每2分频,改善6dB,而倍频则相反,由此在PLL测试Phase noise时,尽量不要分频或倍频,保持原有信号。

1911

1911

3103

3103

1万+

1万+

8985

8985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?