1. 什么是PCIe?

PCIe(Peripheral Component Interconnect Express)是一种高速串行总线标准。它是2001年由Intel提出的,代替PCI/PCI-X和AGP等传统总线。既然是Intel提出的,那它肯定是用于计算机中连接CPU和各种外设。

想象一下,你的电脑就像是一个超级忙碌的城市,里面有许多不同的“街道”和“交通工具”,它们负责把信息从一个地方传送到另一个地方。PCIe就是这些“街道”之一,它连接着电脑内部各种重要的硬件设备,像显卡、硬盘、网卡等。

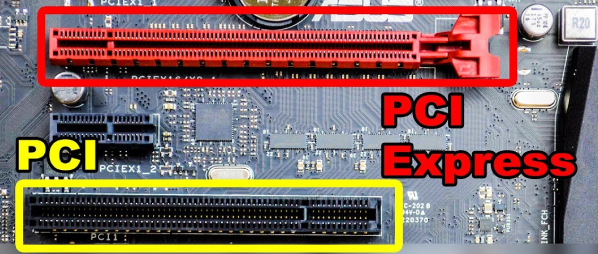

在计算机主板上,PCIe和PCI总线如下图所示。

(图来自网络)

过去,电脑里面的硬件设备是通过 PCI 总线连接的。想象一下,PCI 就像是一个老旧的城市道路,车辆(数据)必须排队等候才能走,而且道路容量有限,交通容易拥堵,速度慢。而 PCIe 就像是一条现代化的高速公路,它不仅更快、更宽敞,而且每辆车(设备)都有自己专用的车道,不会与其他车辆发生拥堵。

PCIe总线特点:串行、差分、全双工、点对点通信、嵌入式时钟、多通道配置和高扩展性。

2. 串行传输

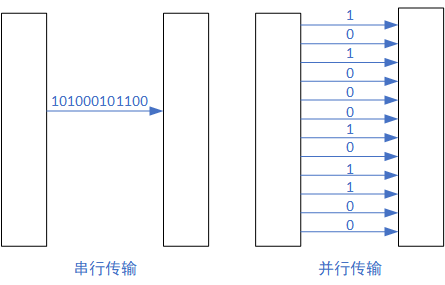

PCIe串行传输,即数据一位一位地按顺序发送。而PCI是多bit并行传输,例如32bit PCI总线一次可并行发送32bit数据。

这里大家肯定会想,多位数据并行传输肯定速度快于单bit数据传输。在时钟频率相同的情况下确实如此,1个时钟周期,PCIe只传输了1bit数据,而32bit PCI已经传输了32bit数据了。如下图所示,串行传输101000101100这十个数据需要10个时钟周期,而并行传输只需要1个周期即可完成。

但是实际上串行传输速率肯定优于并行传输的。这是因为串行传输相比并行传输有如下优点。

优点

(1) 串行传输更容易提升速率,而并行传输很容易遇到瓶颈,需要所有bit数据严格同步,频率越高信号同步就越困难。例如,PCI 32bit总线最大时钟33MHz,带宽仅133MB/s,而PCIe 5.0单Lane速率可达4GB/s,远超PCI。

(2) 多bit并行传输易受电磁干扰。串行传输可以使用差分信号,抗干扰能力强。

(3) 采用串行传输,可以增加Lane来提升带宽。

缺点

(1)需要差分信号来减少干扰,增加了设计复杂度。

(2)在低速、短距离的场景下,串行没有明显优势,并行传输依然高效。

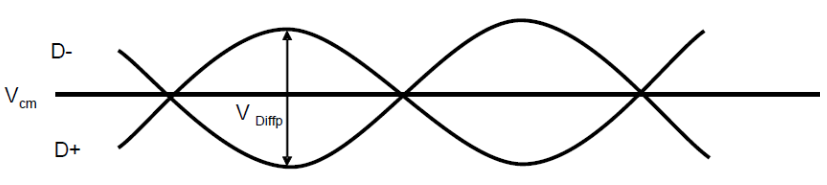

3. 差分

相位相反,即一条信号上升,另一条信号下降。

优点

抗干扰能力强。因为两条信号相反,外部干扰会同时作用在两条线上,但它们的电压差不变,可以有效消除噪声。

缺点

更复杂的硬件设计、更高的成本。

4. 全双工

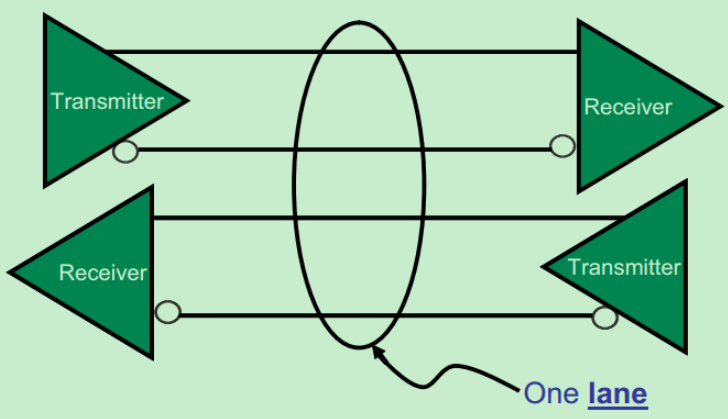

全双工指双向同时传输,每条通道包含独立的发送和接收路径。

PCIe采用串行差分信号,每个Lane都有独立的发送和接收通道,因此天然支持全双工通信。而PCI采用并行总线架构,所有设备共享总线,数据在同一时间只能单向传输。

优点

(1) 提升了带宽利用率,理论带宽是PCI的2倍。

(2) 不需要等待总线仲裁,可立即收发数据。

(3) 适合多设备并行工作。PCIe每个设备都有独立通道,可以同时通信。而PCI多个设备共享同一条总线,必须轮流使用。

缺点

(1) 布线更复杂,物理资源需求更高。

(2) 设计复杂度增加,需要更多的协议管理层。

(3) 能耗可能增加。

5. 点对点通信

设备独享带宽,不会因为其他设备的存在而降低速度,避免传统总线因共享带宽引发的性能瓶颈。点对点架构具有明显的性能优势,但是所有设计都是trade-off的。

也带来了一些缺点:

(1) 主板需要设计更多的独立PCIe通道,增加了工程的复杂度。

(2) 需要更复杂的RC和Switch。

(3) 需要更复杂的驱动和协议(PCIe热拔插、DMA访问),相比PCI总线协议,软件开发更难。

(4)PCI在特定场景仍有优势:低速设备,声卡、嵌入式工业设备,或者设计简单,制造成本较低,适合成本敏感的产品。

为什么PCI传统总线会共享带宽?

因为传统PCI总线架构中,所有设备共享同一条数据总线,数据传输时需要轮流使用总线,就像一条车道上的多辆汽车,每辆车必须等前面的车走完才能通信。

如果多个设备同时传输数据,带宽会被分割,导致数据拥塞,性能下降。因为它们无法独占带宽,所以会影响高速设备如显卡、SSD的性能。

6. 嵌入式时钟技术

PCI使用独立时钟线来同步数据,而PCIe采用8b/10b编码(PCIe 1.0-2.0)或者128b/130b编码(PCIe 3.0+)。

优点

(1)PCIe在数据流中嵌入时钟,不需要额外的时钟线。降低布线复杂度。

(2)提高信号同步性,减少时钟偏移(Skew)。

缺点

(1)需要额外的时钟恢复电路。

(2)更容易受时间抖动(Jitter)的影响。相位抖动会影响信号完整性,需要更严格的时钟补偿。

(3)PCIe初始链路训练时间更长。PCIe设备在启动时需要调整接收端的时钟恢复电路,使其与发送端同步。而PCI直接依赖外部时钟,不需要训练,设备初始化更快。PCIe设备上电时,链路训练可能需要几毫秒到数百毫秒,启动速度比PCI略慢。

(4)PCIe采用点对点连接,每个设备从数据流中恢复自己的时钟,可能会造成设备之间的时钟偏移(Drift)。而PCI所有设备共享同一个外部时钟,确保所有数据传输的时间基准相同。

7. 多通道配置

支持x1/x4/x8/x16等通道组合,通道数越多带宽越高。

优点

(1) 带宽可以线性增加,x16的带宽是x1的16倍。

(2) 灵活扩展,不同设备可以使用不用Lane数量。

缺点

(1) 管理多个Lane,控制器和交换机需要更复杂的设计。

8. 高扩展性

兼容热拔插(在计算机运行时拔插设备,无需重启系统),支持跨代降速使用。

优点

(1)兼容热拔插维护设备更方便和更灵活。不需要关机就可以更换PCIe设备(如硬盘、网卡)。

(2)支持跨代降速使用可以提高设备的兼容性,避免设备被淘汰。例如:PCIe 4.0 的 NVMe SSD 可以插在 PCIe 3.0 主板上,虽然带宽降低,但仍能工作。

缺点

(1)需要额外的硬件设计,增加系统复杂度。

(2)需要软件层面支持,增加开发难度。例如需要 PCIe 热插拔控制器(Hot Plug Controller) 处理插拔事件,并动态分配资源。

(3)成本增加。

下面是个人的小小感悟:

在芯片设计的世界里,任何技术的升级都是权衡(trade-off)。《中庸》有云:“致中和,天地位焉,万物育焉。” 任何技术的取舍,都是在极端之间寻找平衡之道。

PCIe 并非完全摒弃 PCI 的理念,而是以更加灵活的方式,结合串行传输、点对点连接、多 Lane 扩展等特性,使得计算机系统在性能与成本之间取得动态平衡。

芯片设计者的智慧,便在于如何运筹帷幄,顺势而为,使得技术在进步的同时,不至于被其负担所反噬。欢迎关注我的个人微信公众号【芯筹帷幄】,交流你的见解与经验!

推荐学习资料:《PCI Express System Architecture》-MindShare著(关注公众号「芯筹帷幄」私信 “PCIe” 可获取 PDF 版)

《PCI Express 体系结构导读》-王齐著,电子工业出版社(公众号私信 “PCIe中文” 可获取 PDF 版)

欢迎关注,获取更多技术资料与分享!

这里将分享芯片设计的相关知识、技术前沿以及行业动态,期待与您交流和探讨,共同进步!

255

255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?