对于Xilinx的异步fifo,在通常的使用过程中,会用到使用~empty信号, 去读取fifo的数据。

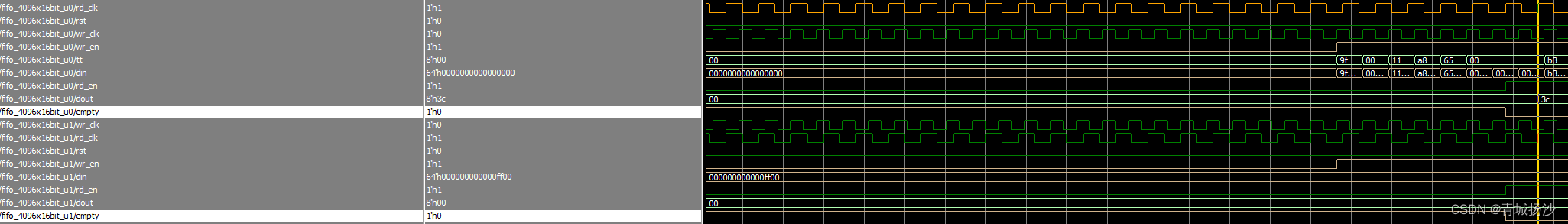

在此操作中需要注意的是,当用到两个或以上的fifo需要同步存取数据时,必须两个fifo的empty信号同时非空才能读取数据,即(~fifo_empty1) & (~fifo_empty2)。下图所示,仿真时fifo的两个empty信号是同步对齐的。

但是,在上板调试时两个fifo的写入信号是同步,但两个fifo的empty拉低的时刻并不同步;为了避免读取fifo数据的错误,要注意务必使用两个fifo的empty相与的操作。

2419

2419

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?