使用88E1514和FPGA连接做以太网通信,走的是LVDS接口

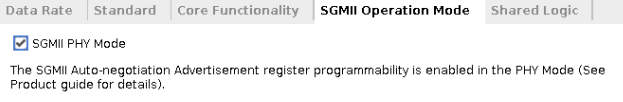

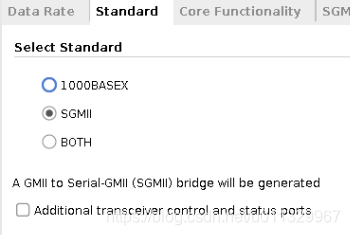

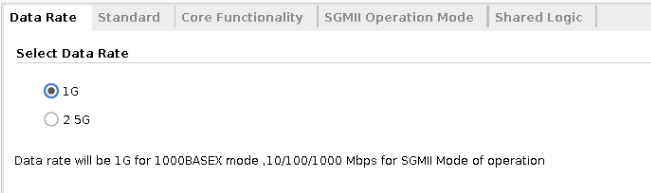

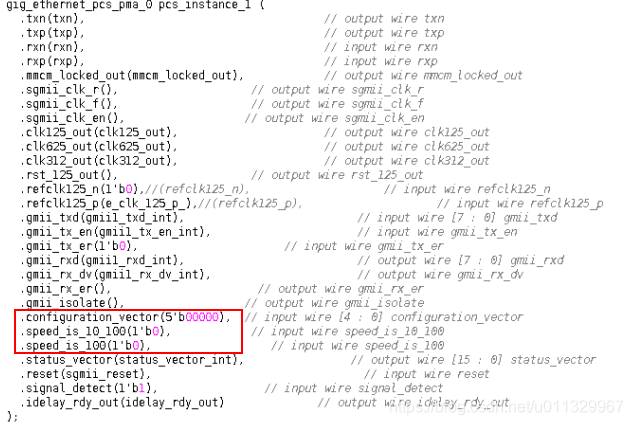

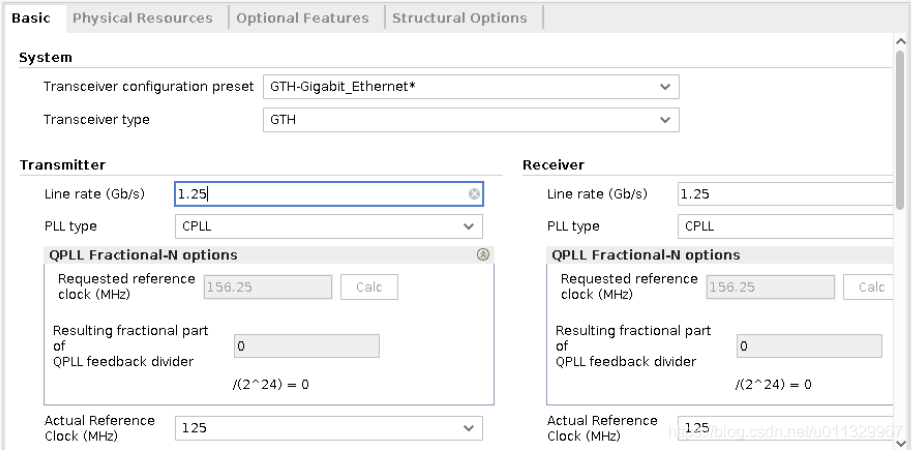

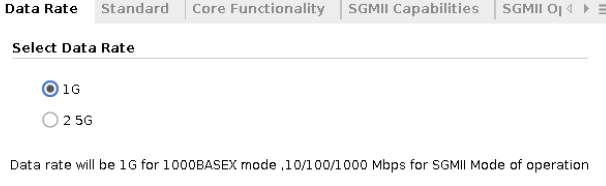

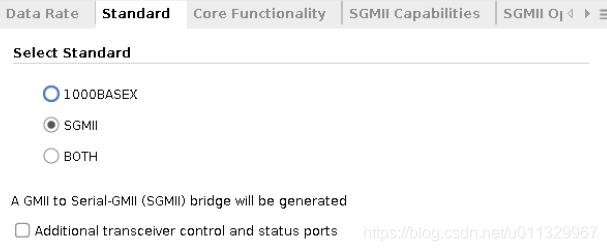

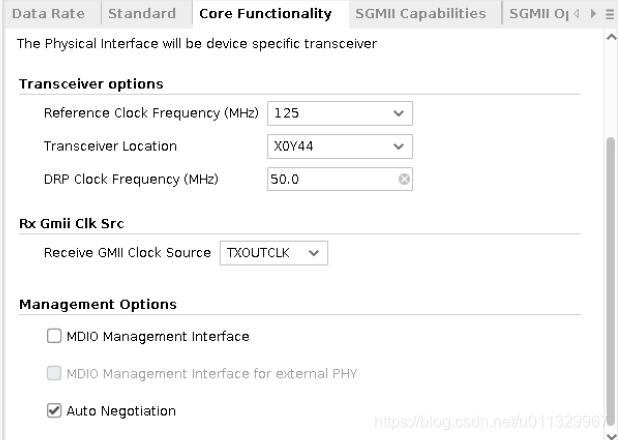

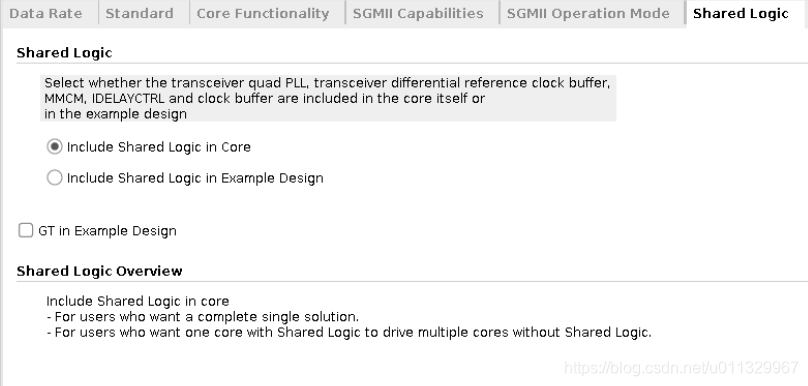

ip核使用:GMII转SGMII的桥,使用了同步SGMII模式,需要提供一路125MHz的同步时钟,并固定在1G模式。

------------------------------------------------------------------------------------------------------------------------

1、外部时钟使用GC管脚,可以直接给到MMCM/PLL,无需加BUFG会引入零点几纳秒的延时

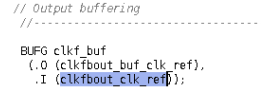

默认我们认为clk和data是对齐的,所以一般要使用MMCM的对齐功能,即输入时钟和输出时钟同相位。MMCM实现对齐的方式是在fbclk上插入了一个bufg,在例化代码可以看到:

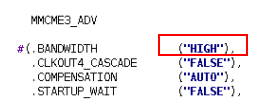

2、修改了xiliinx ip核源文件:(使用了最低抖动,默认是OPTIMIZED)

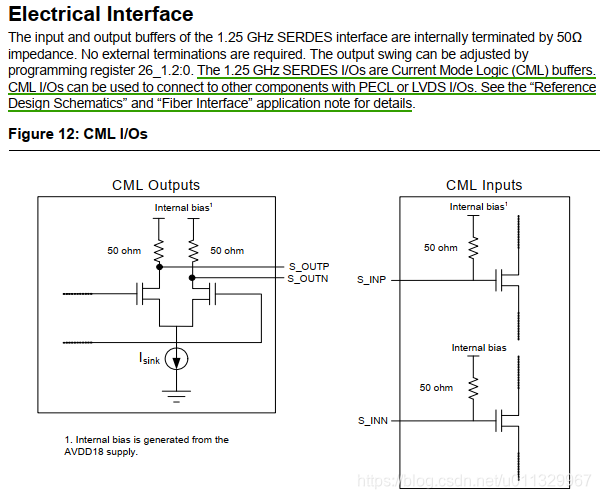

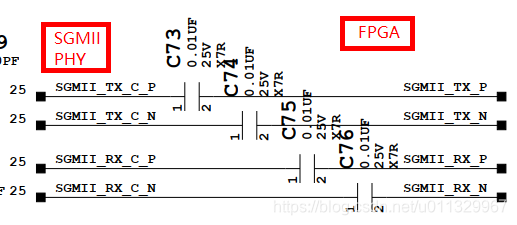

3、SGMII的PHY是CML电路,和FPGA LVDS端接时,FPGA输出需要使用交流耦合,一般串一个0.1~0.01uF/25V的

电容,FPGA输入可以直接耦合(也可以交流耦合),但注意不要使用外部终端电阻,使用FPGA内部电阻。

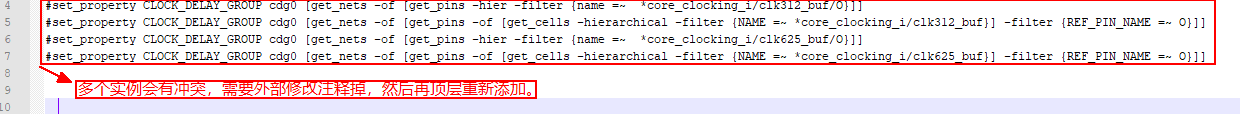

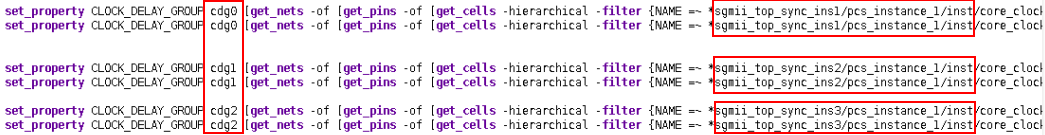

4、clock_delay_group约束

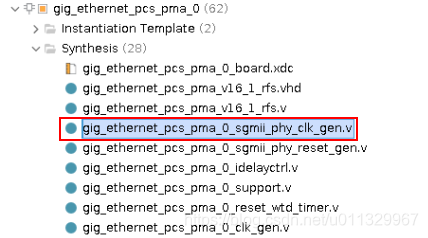

5、修改差分输入为单端时钟输入:

【虽然ip核文件不支持修改,但可以使用其它编辑器打开,在vivado外面修改,修改后在ip核重新生成的过程中替换上去即可(更好的办法是将ip生成设置为global模式,这样

外部修改源文件后会同步重新综合)】

gig_ethernet_pcs_pma_0_sgmii_phy_clk_gen.v

参考:

pg047-gig-eth-pcs-pma.pdf

Alaska®

88E1510/88E1518/

88E1512/88E1514

Integrated 10/100/1000 Mbps

Energy Efficient Ethernet

Transceiver

其它:

https://mindchasers.com/dev/hw-sgmii-review //借助示波器和实验台示例回顾了一些SGMII核心概念

//-----------------------------------------------------------------------------------------------------------------------------------------------------------

追记:sgmii用于serdes调试

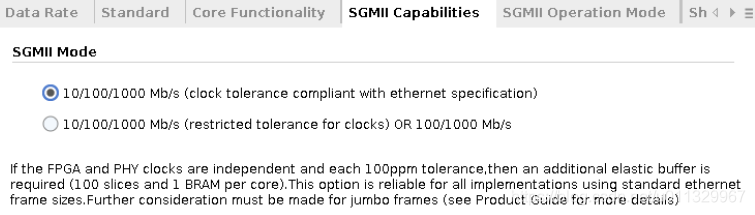

SGMII属于serdes通信,理论上应该不关心相位,但是频率的误差需要控制在200ppm以内,最好的电路模式应该使用

同源时钟。

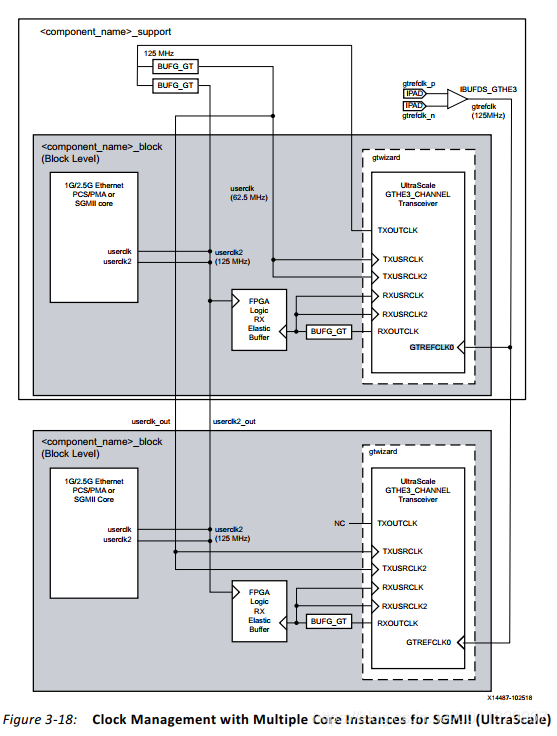

问题1:txoutclk是怎么产生的?为什么不同模块要共用userclk/2时钟,从自己的txoutclk产生不可以吗?

//----------------------------------------------------------------------------------

基于rtl8211fs sgmii调试:

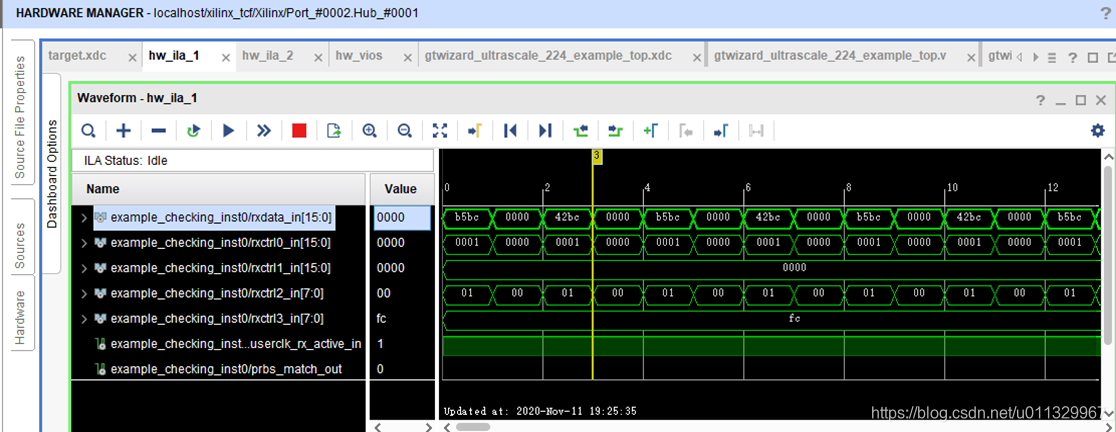

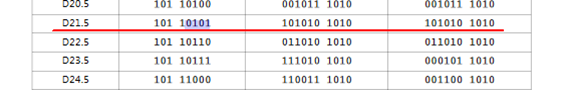

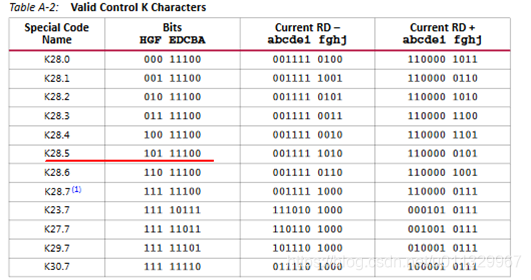

使用gt生成example可以直接抓取相应的1.25Gbps的数据码:根据8/10b可以翻译对应的数据,以及当前自动协商的状态:idel/data/configure

![]()

![]()

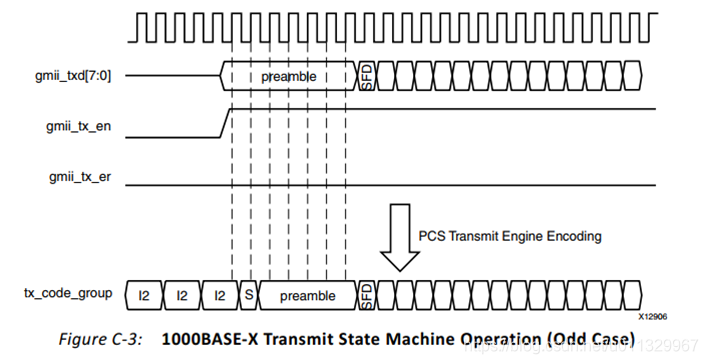

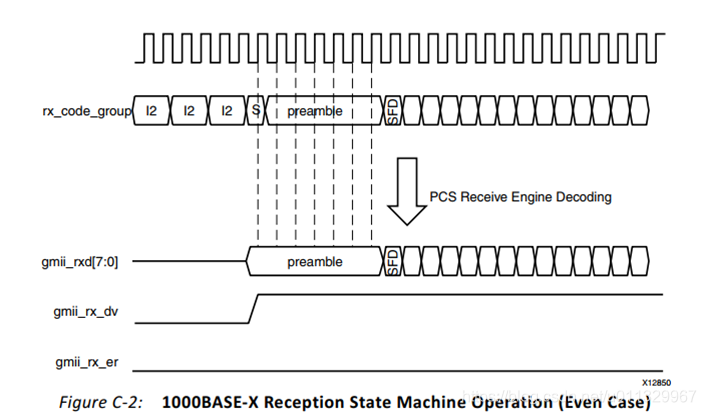

sgmii数据格式说明:

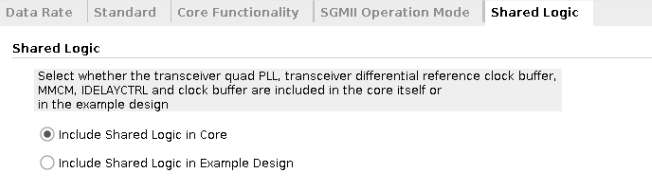

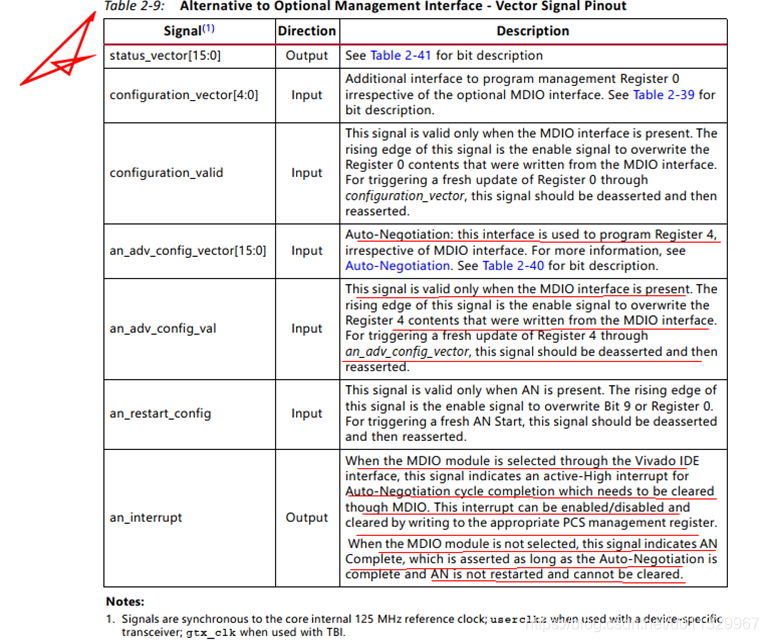

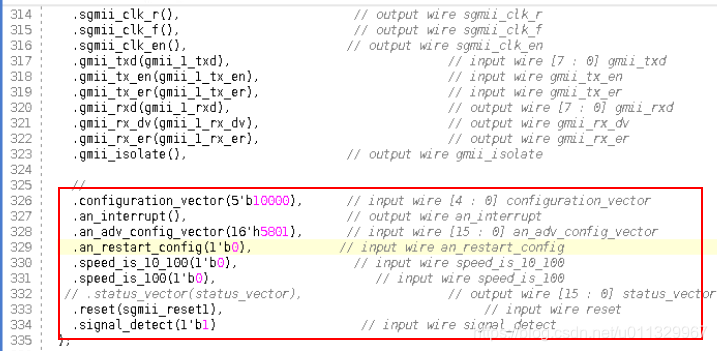

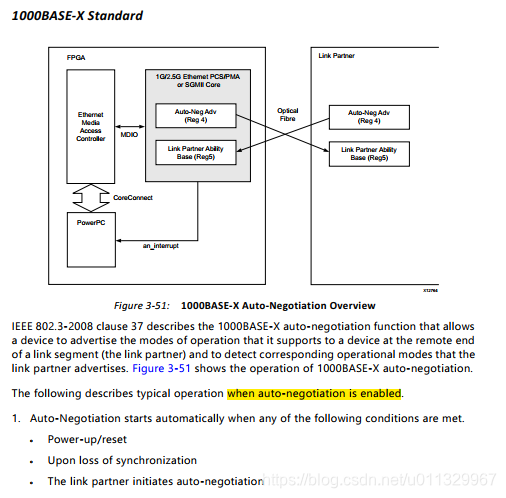

ip核配置需要开启自动协商:配置参考

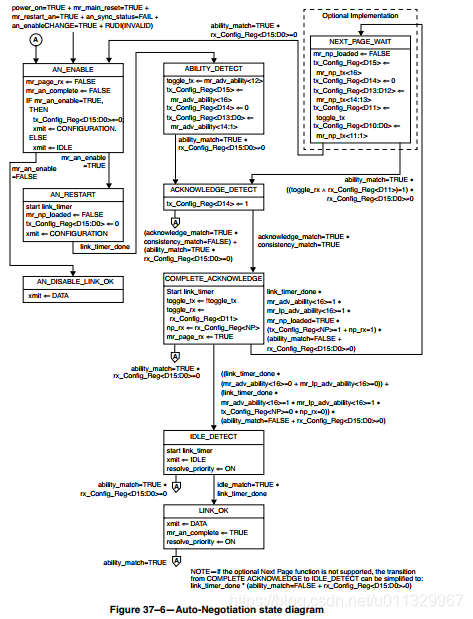

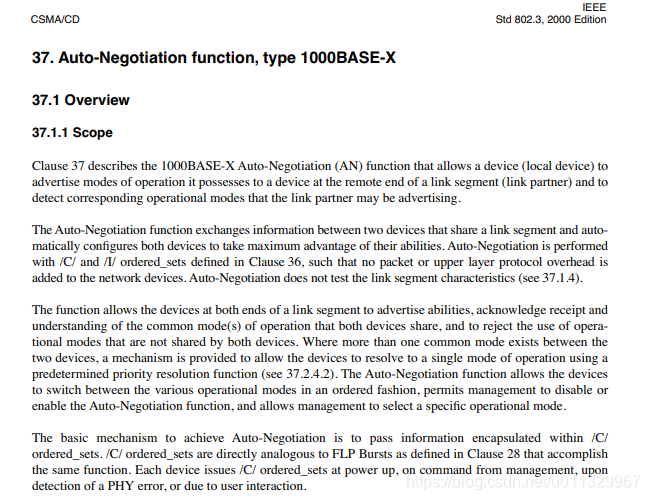

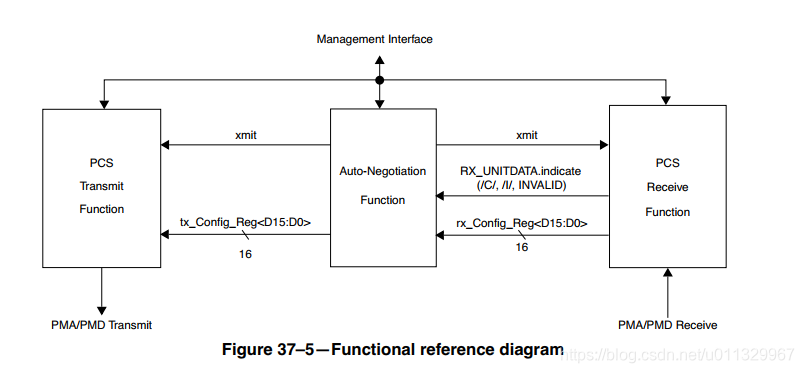

自动协商过程:参考part4,见附

以及pg047:

参考:

https://media.digikey.com/pdf/data%20sheets/csr%20pdfs/ar8031_ds_(atheros)_rev1.0_aug2011.pdf

8b/10b参考xilinx文件附录:

https://www.xilinx.com/support/documentation/user_guides/ug576-ultrascale-gth-transceivers.pdf

以太网标准:

https://ecfsapi.fcc.gov/file/1050839507018/IEEE%20Standard%20for%20Ethernet.pdf

http://download.xskernel.org/docs/ieee/ieee%20802/802.3-2000_part4.pdf

part3:

除了上面的802.3-2000 part4,pg047文档也详细描述了1000BASE-X的自动协商状态机:关于xmit三种工作状态:idel/data/configure

opencores还有一个sgmii的ip可以参考:

https://opencores.org/projects/sgmii

300

300

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?