一、SGMII的概念:

如果说到SGMII则会想到MII、GMII、XGMII、QGMII等信号接口。

SGMII–Serial Gigabit Media IndependentInterfaceSGMII是PHY与MAC之间的接口,类似与GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线相对麻烦,而且不适应背板应用。而SGMII是串行的,不需要提供另外的时钟,MAC和PHY都需要CDR去恢复时钟。另外SGMII是有8B/10b编码的,速率是1.25。所以,SGMII需要PHY来做8b/10b的解码工作。

SGMII在物理上是兼容SERDES信号的,所以走的通道也是SERDESlane。

(该部分概念转载自https://blog.csdn.net/pankul/article/details/8752327)

二、工程建立

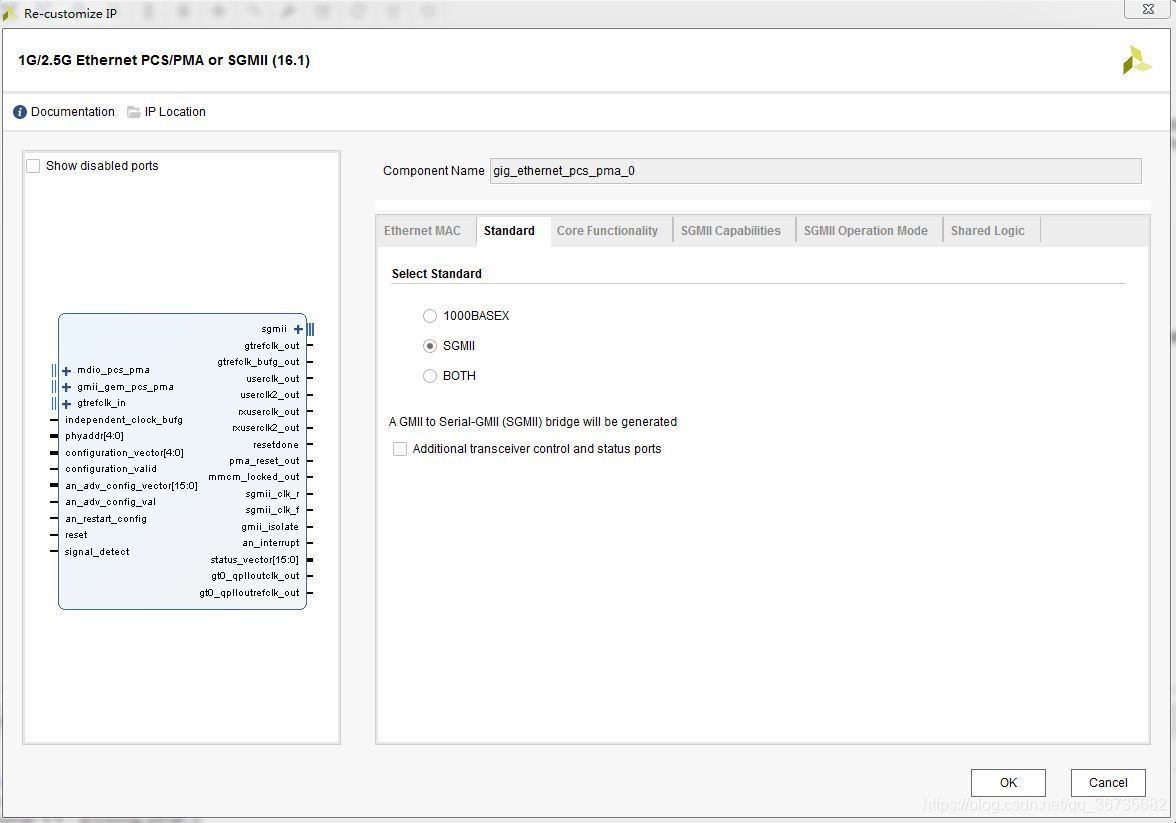

该工程采用Xilinx自带IP核(1G/2.5G Ethernet PCS/PMA or SGMII)进行工程建立,该IP核配置如下所示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2449

2449

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?