模块文件程序:

module selector(a,b,key,led);

input a;

input b;

input key;

output led;

assign led=(key==0)?a:b;

endmodule

`timescale 1ns/1ps

module selector_tb;

reg signal_a;

reg signal_b;

reg signal_c;

wire dout;

selector selector_tb(

.a(signal_a),

.b(signal_b),

.key(signal_c),

.led(dout)

);

initial

begin

signal_a=0;signal_b=0;signal_c=0;

#100;

signal_a=0;signal_b=0;signal_c=0;

#100;

signal_a=0;signal_b=0;signal_c=1;

#100;

signal_a=0;signal_b=1;signal_c=0;

#100;

signal_a=0;signal_b=1;signal_c=1;

#100;

signal_a=1;signal_b=0;signal_c=0;

#100;

signal_a=1;signal_b=0;signal_c=1;

#100;

signal_a=1;signal_b=1;signal_c=0;

#100;

signal_a=1;signal_b=1;signal_c=1;

#200;

$stop;

end

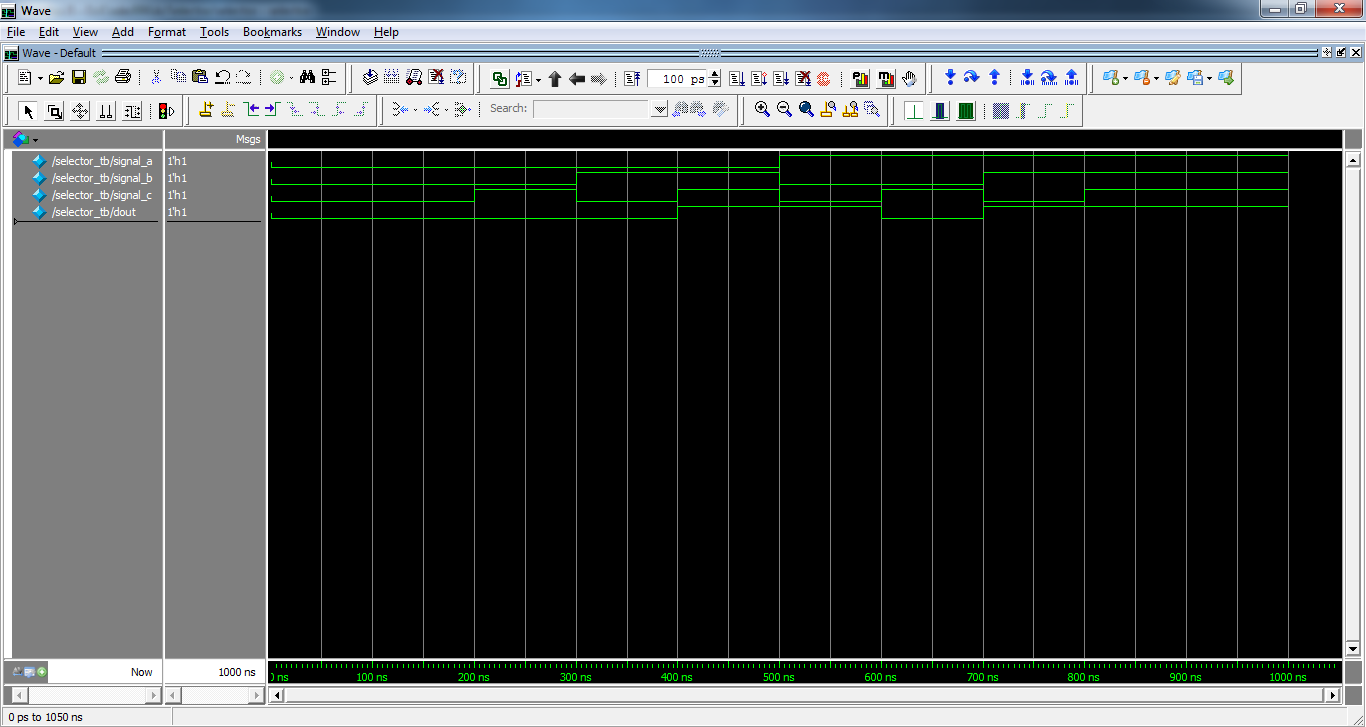

endmodule RTL仿真结果:

3981

3981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?