前言:

FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门开发基于总线的系统。

使用的板子是zc702。

AXI总线初识:

AXI (Advanced eXtensible Interface),由ARM公司提出的一种总线协议。总线是一组传输通道, 是各种逻辑器件构成的传输数据的通道, 一般由数据线、地址线、 控制线构成。 Xilinx从6系列的 FPGA 开始对 AXI 总线提供支持, 此时 AXI 已经发展到了 AXI4 这个版本, Vivado里都是基于AIX4的 IP。

ZYNQ支持三种AXI总线,拥有三种AXI接口,用的都是AXI协议:

AXI4:(For high-performance memory-mapped requirements)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输。

AXI4-Lite:(For simple, low-throughput memory-mapped communication)是一个轻量级的地址映射单次传输接口, 占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data)面向高速流数据传输,去掉了地址项,允许无限制的数据突发传输。

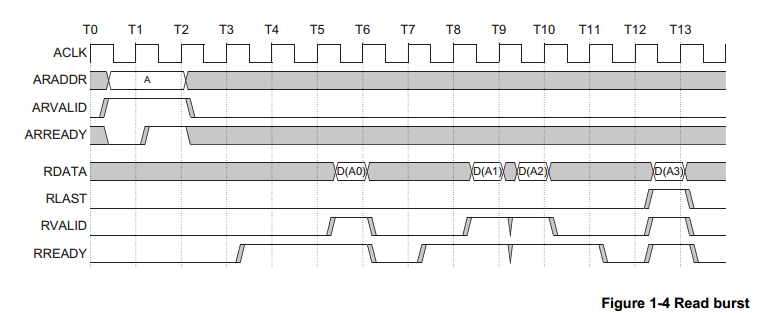

数据在总线上是遵守协议定的规则来传输的,AXI信号传输先是传地址,然后检测READY+VALID,都为高电平时开始传数据,当主机发送最后一个数据时LAST信号拉高,通知从机传输结束。

在介绍读写如何进行前先介绍握手协议:

READY,VALID握手通信机制,主机产生 VLAID 信号来指明何时数据或控制信息有效。从机产生 READY 信号来指明已经准备好接受数据或控制信息。传输发生在 VALID和 READY 信号同时为高的时候。(还有一个LAST信号表示什么时候传到最后一个数据了)

读时序:地址线上发来地址,地址准备和地址有效都高时,开始发送要读的数据,读准备和读有效都高时数据被读取到,发最后一个数据时读LAST信号拉高。

写时序:地址线上发来地址,地址准备和地址有效都高时,开始发送要写的数据,写准备和写有效都高时数据写入,发最后一个数据时写LAST信号拉高。写数据多了一个反馈信号,反馈给主机,主机接收到这个信号,就知道写成功了。

这个协议可以暂时不去理清,知道大致信号关系,后面会通过观察波形进一步加深印象,这次实验的重点是学习通过编程操作寄存器完成读写!

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?