前言

大多数FPGA工程师都知道HMC7044主要是给JESD204B/C接口的ADC/DAC供时钟的主流时钟芯片,那么假如要多片HMC7044时钟芯片输出的时钟要同步,又需要哪些注意事项呢?

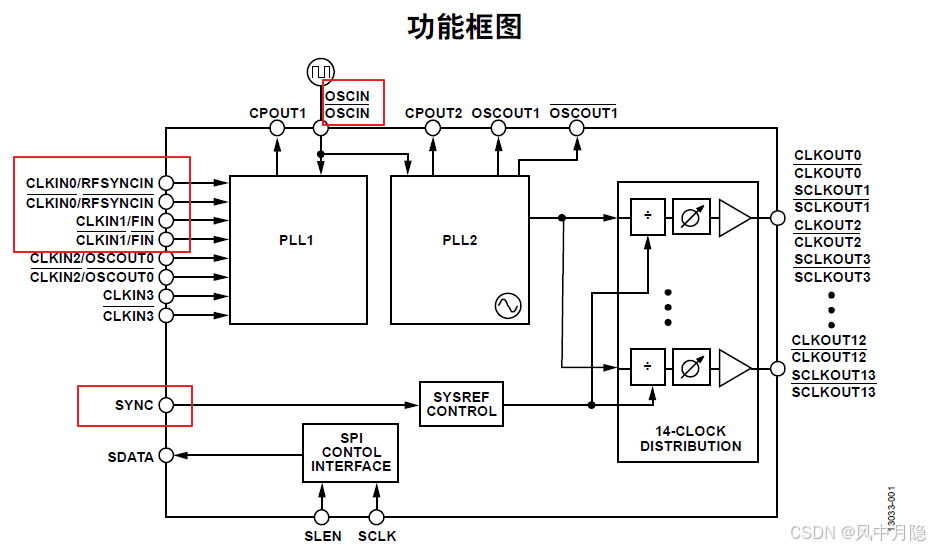

HMC7044的功能框图

HMC7044芯片手册对同步的描述

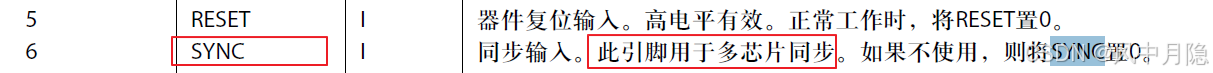

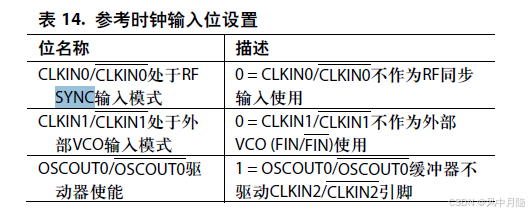

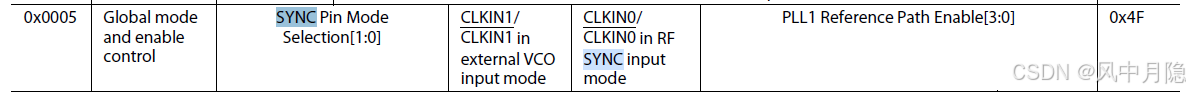

同步引脚描述

同步功能描述

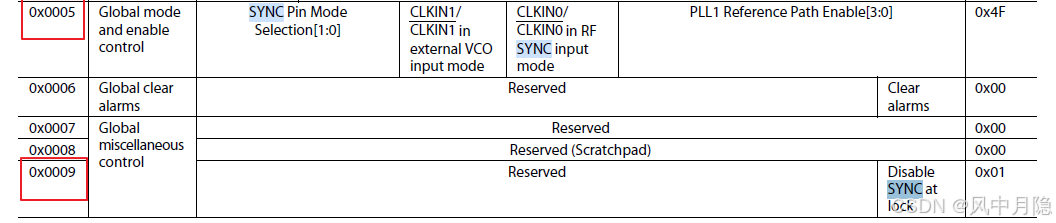

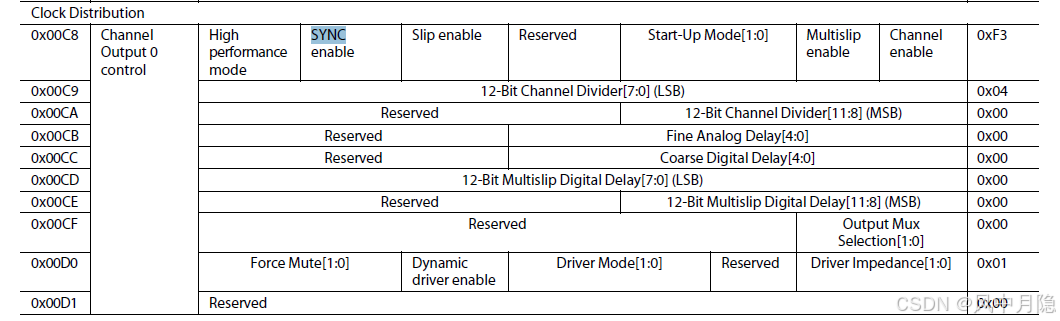

同步寄存器

总结

由HMC7044时钟芯片的手册得知HMC7044可以进行多片同步,其主要注意点如下:

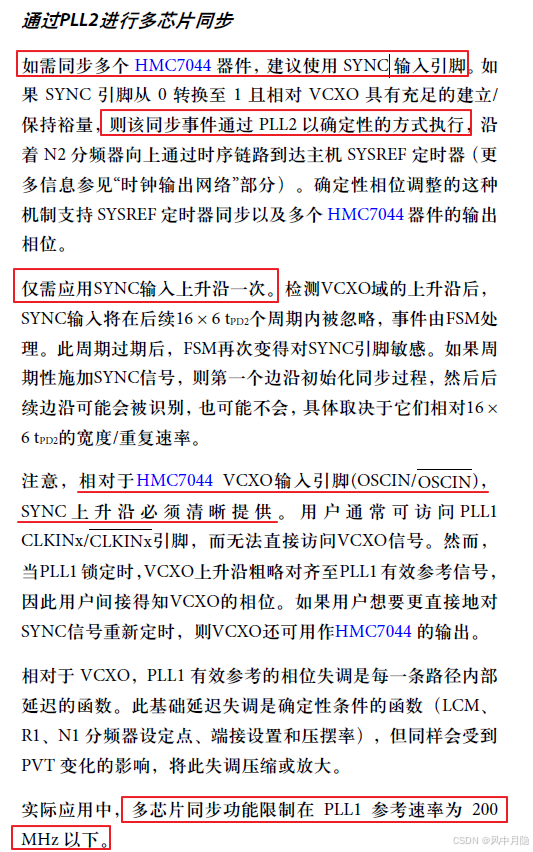

- 要使用SYNC作为同步输入信号时,主要是通过PLL2的VCXO进行同步,时钟输入引脚是OSCIN;

- HMC7044时钟同步检测是检测的SYNC的上升沿,且要SYNC的上升沿足够明显,即相对输入时钟频率低的多;

- 需要修改寄存器,使能SYNC信号;

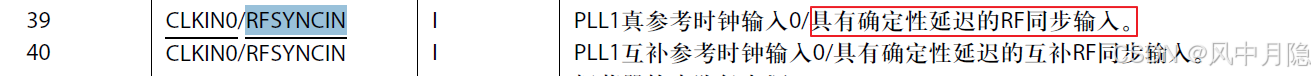

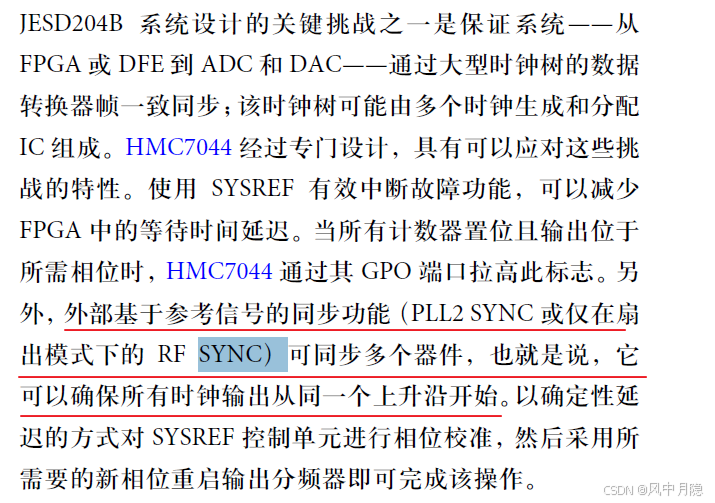

- RFSYNC也可以作为确定性延时RF同步输入的触发引脚;

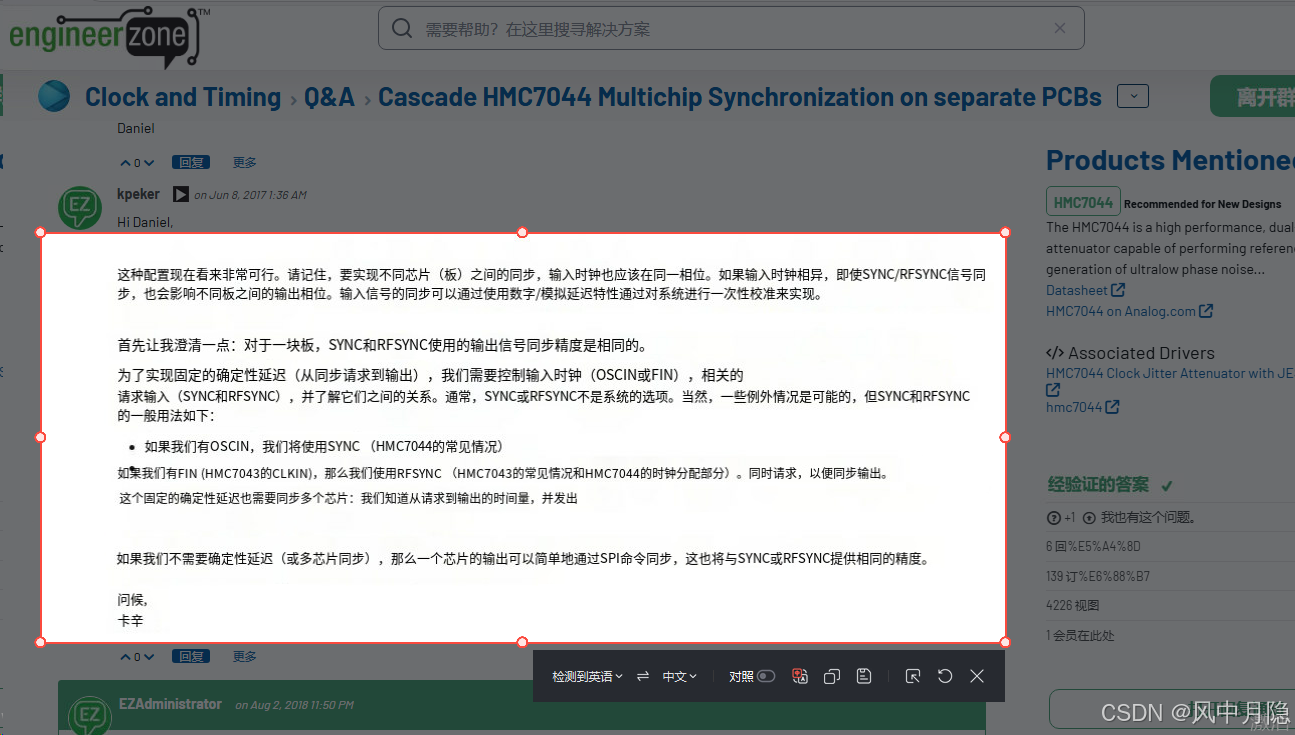

通过外网查询以及结合手册可知,假如使用RFSYNC作为确定性延时RF同步输入的触发引脚,则需要注意:

-

用FIN引脚作为参考时钟的输入引脚;

-

需要修改寄存器,启用RFSYNC功能(因为该引脚是功能复用引脚);

-

PLL1的输入参考时钟要在200MHZ以下;

补充:ADI官方论坛查询同步资料

若需要获取HMC7044的手册中文版,关注微信公众号后,回复"7044"即可获取

——————————————————————————————————————————

如果本文对你有所帮助,欢迎点赞、转发、收藏、评论让更多人看到,赞赏支持就更好了。

如果对文章内容有疑问,请务必清楚描述问题,留言评论或私信告知我,我看到会回复。

——————————————————————————————————————————

欢迎FPGA同行者关注微信公众号FPGA加速者,获取更多精彩

2712

2712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?