系列学习介绍DC相关知识,包括ASIC基本单元相关,DC指令工艺库脚本相关,后端综合实现相关等总结。本节包括锁存器,建立时间和保持时间,增强驱动能力的buffer介绍。

1.1 数字ASIC基本知识

1.1.1 锁存器产生

组合逻辑中case结构缺乏default

组合逻辑中if-else结构描述不全

组合逻辑always()中敏感列表不全

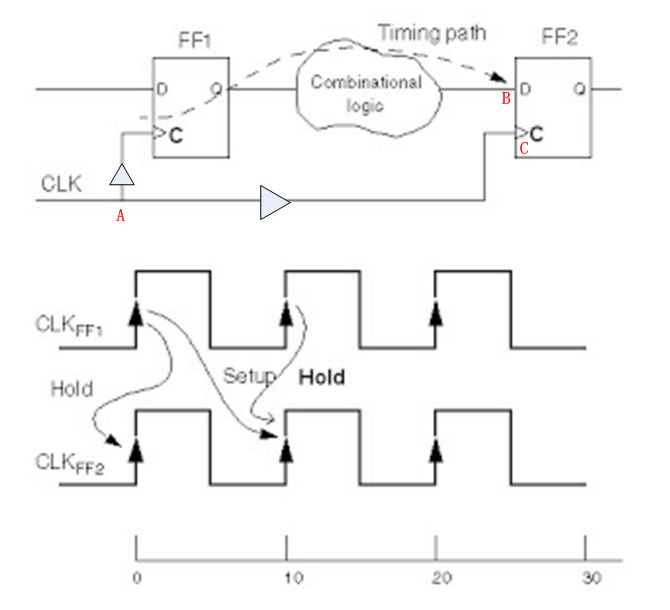

1.1.2 建立时间与保持时间

建立时间

Tdata_path+ Tsetup <= Tclk_path+ Tperiod

所以

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic+ Tsetup <= Tclk_delay_FF2 +Tperiod

保持时间

实质是当前时钟沿的FF1输出不能太快在当前沿到达FF2。

Tdata_path– Thold >= Tclk_path

所以:

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic– Thold >= Tclk_delay_FF2

1.1.3 能增强驱动能力的buffer介绍

buffer一般是几级器件尺寸逐步增大的反相器或类似结构的电路,以使得电阻在获得所需的驱动能力时,在功耗延时积上也达到最优。前后级的最佳驱动比例在2.718左右。buffer实际就是两个串联的反相器,常用于时钟路径中,用于增加时钟驱动能力,使得时钟clock具有良好的上升沿和下降沿。时钟buffer本身是输入负载较小,输出驱动能力较强。因此前级电路驱动buffer容易,而buffer驱动后级电路也比较容易。

工作原理:通过插buffer的方式减少了电路的负载电容,负载电容减少后,同样电压的情况下,对电容充电速度快(上升沿陡峭),同样电容小时存储的电容小,放电所需的时间短(下降沿陡峭)。一句话来说就是: 插buffer的方式减少了电路的负载电容,从而增大了电路驱动能力。

应用场景-1:通过插buffer减少负载数量

应用场景-2:减少连线负载

问题1:在时序路径中插入buffer到底是减缓了数据传输呢还是加快了呢?

在时钟树综合过程中,会在clock root pin和cells’ clk pin之间插入buffer产生延时,以求最小的skew;然而,我们又知道在时序路径中“断点插buffer”,目的是加快该路径上的信号传输速度。

解答:如果这个地方有transition 比较大,插buff会改善transition,加入buffer本身所带来的delay远远小于插入这个buffer所减小的delay,所以delay 变小;如果插之前之后都不存在transition问题,加入buffer本身所带来的delay远远大于插入这个buffer所减小的delay的时候,那么就是增加delay。

问题2:数学计算说明transition较大,插入buffer如何减小延时?

名词解释

LVT:低阈值开启电压,cell 容易被开启,速度快,但泄漏功耗大,常用于修复setup违规,但不能大规模使用。

RVT:正常的阈值开启电压,作为逻辑综合和布局布线主要的cell。

HVT:高阈值开启电压,cell不容易被开启,泄漏功耗小,但速度慢,常用于在Timing没有问题的情况下的功耗优化。

参考文档

【1】建立时间和保持时间(1)

5194

5194

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?