文章目录

系列学习介绍DC相关知识,包括ASIC基本单元相关,DC指令工艺库脚本相关,后端综合实现相关等总结。本节包括DC综合时的一些优化策略,内容有一些个人理解和各地方论坛总结学习,有不同认识欢迎探讨,fighting。

Synthesis Optimization Techniques

5.1 综合优化策略

level主要集中在gate_level,调用compile或compile_ultra。

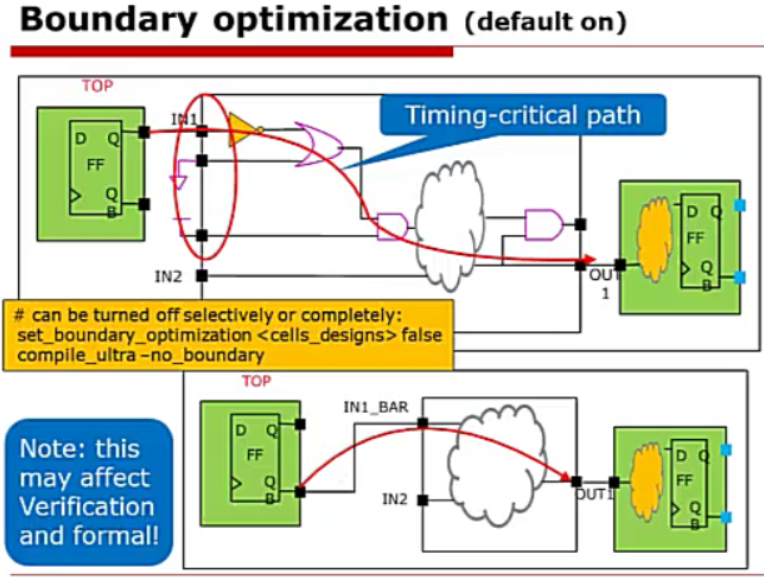

5.1.1 Boundary optimization边界优化

在编辑时,Design Compiler会对传输常数,没有连接的引脚和补码信息进行优化,也就是说边界优化会把边界引脚一些固定的电平,固定的逻辑进行优化。但是在formility(形式验证),需要告诉formility电路结构发生了改变。这个改变存放在DC的生成文件里。

set_boundary_optimization<cells_designs> false #可设置某些cell不做边界优化

compile_ultra -no_boundary #批量设置不进行边界优化

5.1.2 Auto-ungrouping及其取消

compile默认不打散,compile_ultra会自动将模块打散,打散后只能看到top层和具体实现;

set compile_ultre_ungroup_dw true ;#允许打散,取消desigware层次。也就是说,调用的一个加法器和一个乘法器,本来他们是以IP核的形式,或者说是以模块的形式进行综合的,但是设置了上面那么变量之后,综合后那个模块的界面就没有了。

为了使设计的结果最优化,建议将compile_ultra命令和DesignWare library一起使用。也就是说不打散较好。

set_ungroup <reference_or_cells> false ;#禁止cell打散

set_app_var compile_ultra_ungroup_dw false ;#禁止打散,使用designware层次

compile_ultra -no autoungroup ;#全部都不打散

论坛引用:全部ungroup打散后,没有boundary,一般功能是不会影响的,LEC来保证。但是function层次就没有了,比如对网表做一些verification,如STA时一些重要的点可能找不到了,如果还要debug的话几乎做不下去。

5.1.3 timing_high_effort_script

对时序做最好的优化,会把时序的优先级提升到超过DRC(Design Rule Check)的优先级,DRC是工艺厂商的要求,不满足DRC可能会出错。

compile_ultra -timing_high_effort_script

5.1.4 -timing 和 -retime

compile_ultra -timing #采用register replication的方法修复critical path时序

compile_ultra -retime #把时序不满足部分组合逻辑转移到有余量地方,前一级就得到很大的改善。后面的violation可以通过把时钟稍微往后挪一点来改善掉。

#Retiming的基本思想:这几种结构在功能和时序上是等效的

5.1.5 group_path划分原理

设计的时序路径分组,叫做path groups。默认每个时钟域对应一个path group,只有一个时钟情况下,划分为4个path_group:InputToReg、RegToReg、RegToOutput、InputToOutput。

==DC综合时序优化,每个path group,先优化关键路径(即最差的时序路径),然后才会优化接下来最差的时序路径。==这也是为什么区分不同path_group,如果最差的时序路径不满足,其余也不会优化,但有时优化次差路径有利于最差路径优化。

关键路径找不到优化解决方案,就会报告时序违反;也就是说关键路径没有达到时序满足,不会优化其它违反的时序路径。

group_path -name INREG -from [all_inputs]

group_path -name REGOUT -to [all_outputs]

group_path -name INOUT -from [all_inputs] -to [all_outputs]

group_path -name CLK -critical_range 0.2 #相比于critical_path差0.2ns的路径都可以得到优化,数值设置不能超过时钟周期的10%,过多的话需优化路径过多,效果未必更好

group_path -name CLK -critical 0.2 -weight 5 #权重为5优先优化RegToReg

名词解释

TNS: total negative slack总的负时序时间之和,即小于0的slack之和

WNS: worst negative slack最差的负时序

THS: total hold slack总的保持时间的负时序之和

WHS: worst hold slack最差的保持时间的负时序

参考文档

【1】DC学习(8)综合与优化

【2】[求助]ungroup使用

4152

4152

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?