数字设计 FPGA 应用,数字设计 FPGA 应用,第四章时序逻辑设计和实现,课程设计性质的作业题1

第一题:构建工程,实现计数器 74HC163,编写仿真代码进行测试,将该工程并生成 IP 核。(必须)

使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

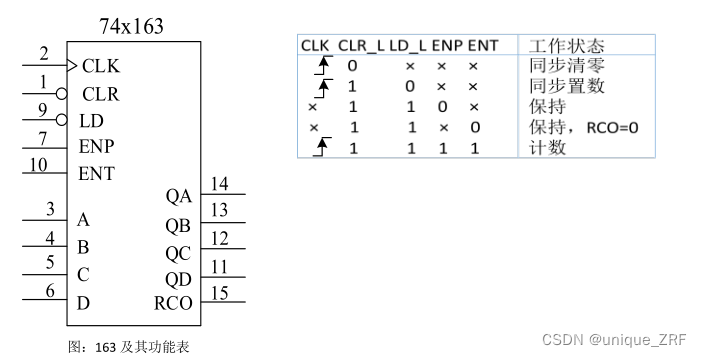

74HC163

74x163及其功能真值表

代码实现

1. verilog代码

`timescale 1ns / 1ps

//

// Module Name: v_74x163

// Revision 0.01 - File Created

// Additional Comments:

//

//

//文章有用的话记得给靓仔点个赞表示鼓励哟~

module v_74x163(clk,clr_l,ld_l,enp,ent,d,q,rco);

input clk,clr_l,ld_l,enp,ent;

input[3:0] d;

output[3:0] q;

output rco;

reg[3:0] q = 4'b0000;

reg rco = 0; //进位输出

always @(posedge clk) //时钟上升沿

begin

if(clr_l == 0) q<=0; //同步清零

else if(ld_l == 0)q<=d; //同步置数

else if((ent ==1)&&(enp==1))q<=q+1;//使能有效,计数

else q<=q;

end

always @(q or ent) begin

if((ent == 1) && (q==15)) rco = 1;//进位

else rco = 0;

end

endmodule

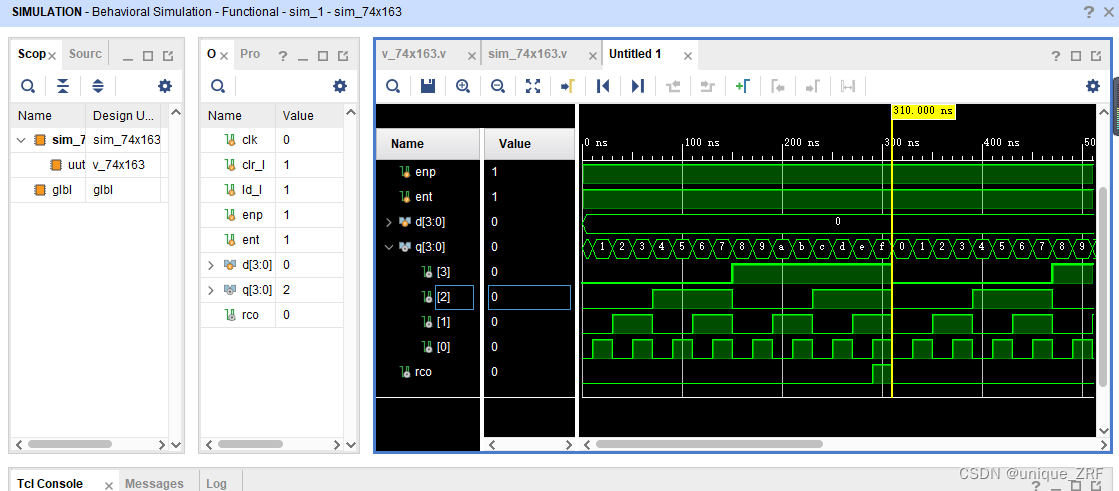

2. 仿真结果

2.1 计数功能

`timescale 1ns / 1ps

//

// Design Name:

// Module Name: sim_74x163

//

//文章有用的话记得给靓仔点个赞表示鼓励哟~

module sim_74x163();

reg clk=0;

reg clr_l=1;

reg ld_l=1;

reg enp=1;

reg ent=1;

reg[3:0] d=0;

wire[3:0] q;

wire rco;

v_74x163 uut(clk,clr_l,ld_l,enp,ent,d,q,rco);

always #10 clk=~clk;

endmodule

从图中可以看出,clr_l=1,ld_l=1,enp=pnt=1时,时钟信号每产生一个上升沿,计数加一,到q=1111时,进位rco=1,为16进制计数器,计数功能已实现。

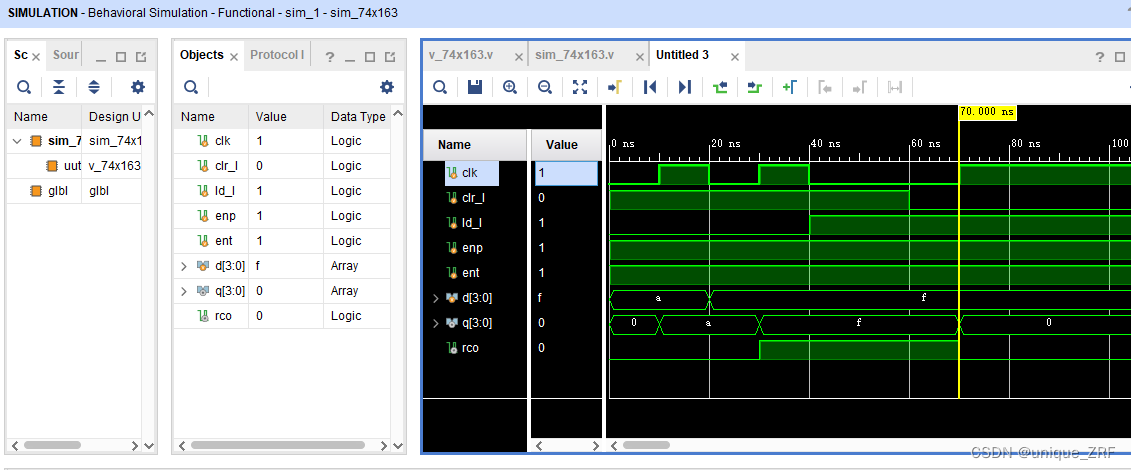

2.2 置数、保持和清零功能

//点个赞咯

reg clk,clr_l,ld_l;

reg enp=1,ent=1;

reg[3:0] d;

wire[3:0] q;

wire rco;

v_74x163 uut(clk,clr_l,ld_l,enp,ent,d,q,rco);

initial begin

clk=0;

clr_l=1;

ld_l=0; //置数

d=4'b1010;

#10

clk=1; //上升沿

#10

clk=0; //下降沿

d=4'b1111; //新的数

#10

clk=1;//上升沿

#10

//保持

clk=0;

ld_l=1;

#20

clr_l=0; //清零

#10

clk=1; //上升沿

end

从图中可以看出,在10ns的时候clk产生上升沿,q被置数为d的值即为a,30ns的时候,q被置数为f,经过40ns的保持之后,在clk产生上升沿的时候清零。

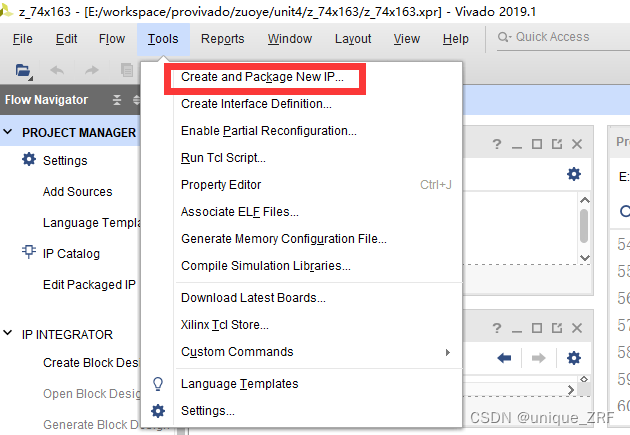

3. 生成ip核

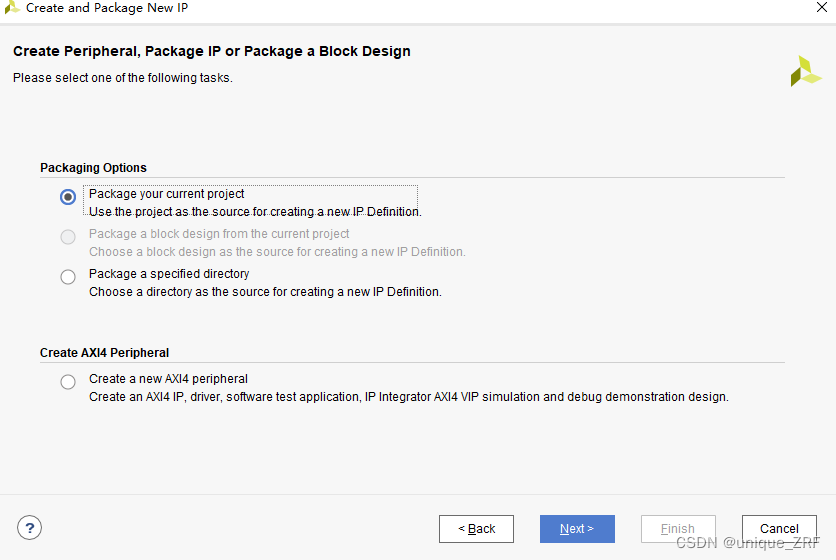

- 编写完代码之后保存,在菜单栏“Tools”下选择“Create and Package New IP…”

- 然后点next到达下一步,选择第一个选项,然后点next

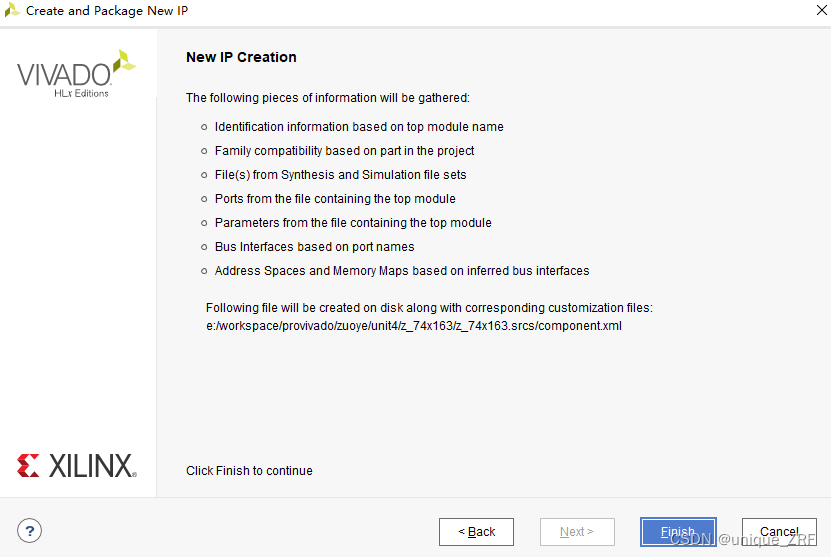

- 选择默认的名字和路径然后点击next,接着点finish即可完成IP核创建

1183

1183

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?