全文 3200字。

目录

接口芯片诞生?

图片来源: 与非网

作者:半导体产业纵横

内存接口芯片,作为连接CPU和内存之间的桥梁,扮演着至关重要的角色。它集成在内存模组上,实现了CPU对内存数据的访问。

在计算机体系中,CPU负责进行各种计算任务,而内存则是数据的存放地。然而,由于CPU技术的快速进步,处理速度大大提升,而DRAM内存的优势则在于其较大的容量和高性价比。这导致了内存读取速度的瓶颈,被戏称为“存储墙”。

为了解决这个问题,内存接口芯片应运而生。其设计的初衷就是解决服务器CPU处理速度与内存存储速度不匹配的困扰。

内存接口芯片的诞生填补了处理器与内存之间的速度差距,提高了系统的整体性能。它打破了“存储墙”,为计算机技术的发展带来了巨大的推动力。

接口芯片市场

大浪淘沙,现在内存接口芯片的供应商只剩下:Rambus, 瑞萨,澜起科技。

内存接口芯片,宛如一颗不起眼的小石子,单价不过20元,然而,它孕育着巨大的市场潜力。尽管市场规模并不算庞大,但它却在默默地逐年扩大。

截至2022年,全球内存接口芯片市场规模已突破11亿美元,而随着DD5技术的普及,这一数字有望在2028年飙升至约40亿美元。这令人惊叹的复合年增长率预计将高达28%。内存接口芯片,或许只是微不足道的一块小零件,但它却以迅猛的势头在市场上崭露头角,为数字世界的发展注入了活力。(来源: 乐晴智库,百家号)。

内存接口芯片下游客户集中在美光、海力士和三星这 3 家,非常集中。这样内存接口芯片厂商在价格谈判的话语权比较弱。

基础知识

DDR5将会有5-6个子代,澜起科技接口芯片速率第一子代为4800MT/s,第四子代为7200MT/s,提升了一半。

接口芯片公司如澜起,fabless 的芯片设计公司. 代工属于成熟制程,40/55/65纳米。

接口芯片数量

| DDR世代 | 接口芯片数量 |

|---|---|

| DDR4 | 12 |

| DDR5 | 24-32 |

接口芯片类型

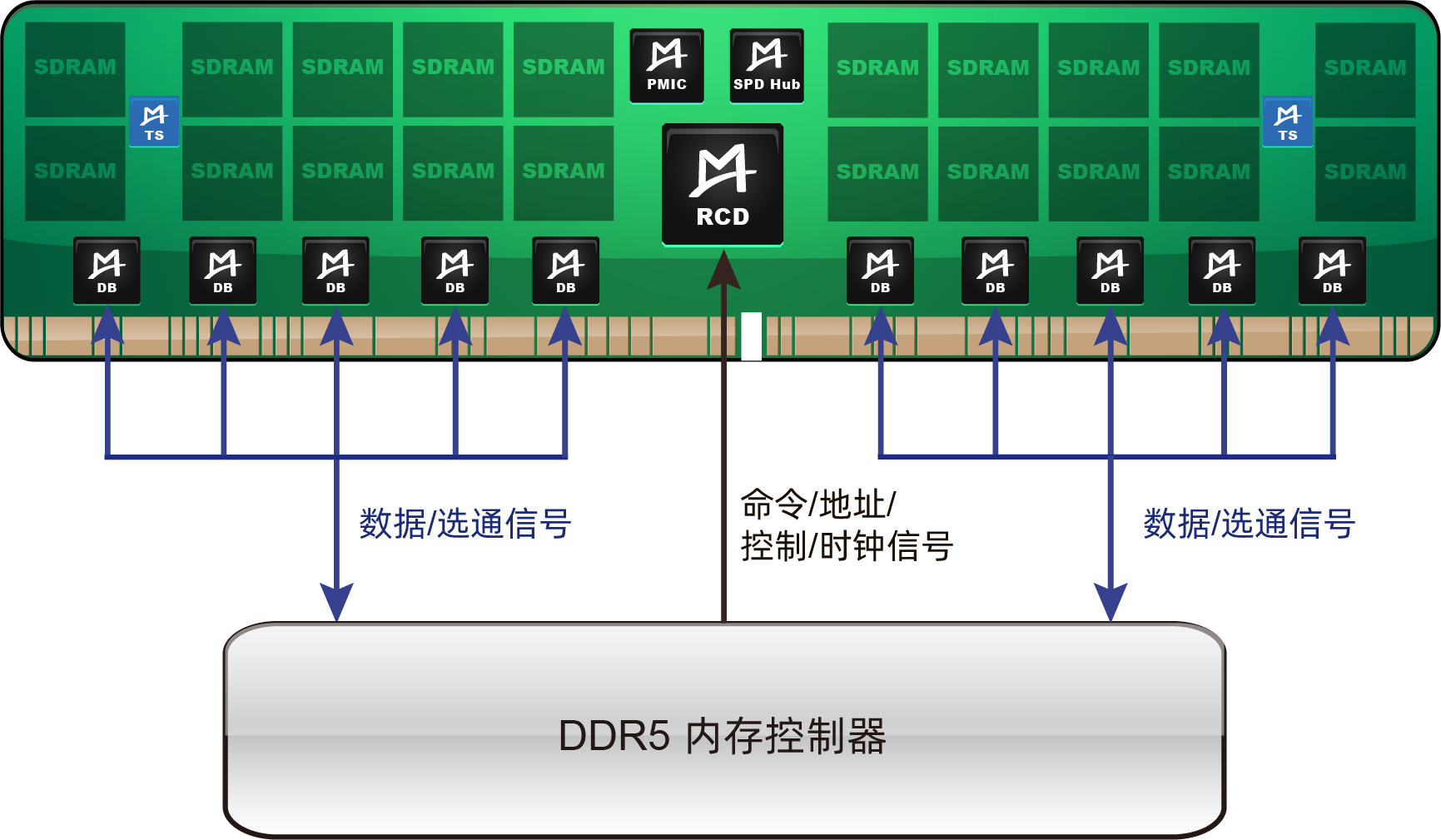

DDR5内存接口及模组配套芯片,是DDR5内存模组的重要组件,芯片类型包括:

-

温度传感器 (TS)

-

电源管理芯片 (PMIC)

-

寄存时钟驱动器 (RCD): 缓冲来自内存控制器的地址、命令、时钟、控制信号。

-

数据缓冲器 (DB):缓冲来自内存控制器或内存颗粒的数据信号。

-

串行检测集线器 (SPD Hub)

DDR5内存接口芯片数量较DDR4世代有所提升,同时新增内存模组配套芯片的需求。

价格方面,DDR5内存接口芯片的单价可达上代产品2倍以上。

内存更新换代周期一般在5年。

接口芯片技术

TS (温度传感器) 芯片

来源:澜起官网

上图蓝色就是TS,DDR5主流配 2 个 TS 芯片,在DIMM板子两侧。

功能特点

兼容 JEDEC 规范

支持 I²C 和 I3C 串行总线接口

支持 PEC (数据包错误校验) 功能和奇偶校验功能

支持总线重置功能

支持带内中断 (IBI)

封装:6 引脚 WLCSP

主要应用

DDR5 服务器的 RDIMM 和 LRDIMM 内存模组

温度管理

服务器 CPU 可经由 SPD Hub 与 TS 进行通讯,从而实现对内存模组的温度管理。

DB (数据缓冲器) 芯片

DB 芯片用来缓冲来自内存控制器或内存颗粒 (DRAM) 的数据信号。

DDR5需要更多的DB。在DDR5 LRDIMM中用到10颗DB,而DDR4 LRDIMM的方案是9颗DB。DB芯片与DDR5 RCD(寄存时钟驱动器)芯片一起组成套片,用于DDR5 LRDIMM

来源:澜起

来源:澜起

RCD (寄存时钟驱动器) 芯片

服务器CPU的并行内存信号输入对信号的稳定性要求较高。一种解决方案是通过物理手段确保信号线的长度完全一致,然而这种方法在实际应用时需要严格的工艺要求。而且当信号频率较高时,这种方式的效果明显不佳。而采用RCD(Resistor-Capacitor-Diode)技术则可以有效解决这一问题。

RCD芯片对内存信号进行缓冲驱动,从而保证了不同输入信号线的一致性。

CKD (时钟驱动器) 芯片

CKD零相位延迟,可提高客户端内存数据访问的速度及稳定性,以匹配高速CPU的速度。

DDR4世代,时钟驱动功能集成在寄存时钟驱动器(RCD)芯片上,主要用于服务器模组,而尚未应用于个人电脑。在 DDR5世代,当数据速率达到6400MT/s以上时,时钟驱动器(CKD)芯片也成为客户端内存模组不可或缺的组件。这意味着在个人电脑领域,集成时钟驱动功能将成为标配。(来源:澜起官网 )

2024年4月10日,澜起科技在业界试产DDR5一子代时钟驱动器芯片(简称CKD)。

来源: 澜起官网

来源: 澜起官网

SPD Hub (串行检测集线器 ) 芯片

SPD(Serial Presence Detect),是一个EEPROM(8 Kbit 容量),是DIMM的相关描述信息,记录内存的最基本的参数,主板启动对内存进行检查时可以参考其中的信息: 内存厂商、容量、频率、电压、速度与带宽等参数。进而调整对内存的读写等待时间等。

内部集成了, I²C/I3C 总线集线器, 主控设备与内存模组通过 I²C/I3C通信。

PMIC

PMIC 为其他芯片提供电源。

PMIC 需要符合JEDEC超高电流(PMIC5020)、高电流(PMIC5000)和低电流(PMIC5010)规范。

PMIC 包含 4 个直流-直流降压转换器和两个线性稳压器 (LDO,分别为 1.8 V 和 1.0 V),采用I²C/I3C 串行总线。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?