在平常的FPGA调试过程中,经常会遇到Vivado工程非常庞大的情况,其大小可能达到数百兆甚至几个G的级别。如果存在大量的调试版本,这样的工程大小可能超过了几个T的硬盘空间。那么我们该如何应对呢?

实际上,Vivado提供了一种使用Tcl命令保存Vivado工程为.tcl脚本的方法,这样可以大幅减小工程的存储空间。通常,几百兆大小的工程只需要几百K的存储空间就可以保存了。

这种方法的基本思路是将Vivado项目的所有设置、约束、源文件路径等信息保存为一个Tcl脚本文件,以便在需要时重新加载和重建工程。

下面把vivado最全面的工程压缩步骤总结一下,让你的工程小到几kb:

vivado工程瘦身:

vivado工程压缩:

先给大家看一下,瘦身后的效果对比:

如图可见,瘦身效果非常明显。

直接压缩了,好几个数量级,这样就可以方便的把代码保存,回头需要的时候,只需要简单的恢复就行了(恢复教程在第四步)。

首先来看一下,没有压缩前的工程大小:

开始压缩 ↓ ↓ ↓ ↓ ↓

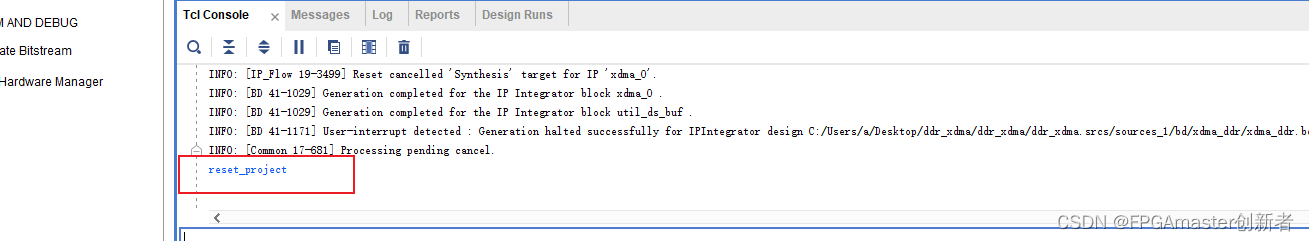

1、复位工程

在Tcl Console中输入reset_project 命令,

reset_project

工程成功压缩了95%,效果非常明显,但是还不够完美:

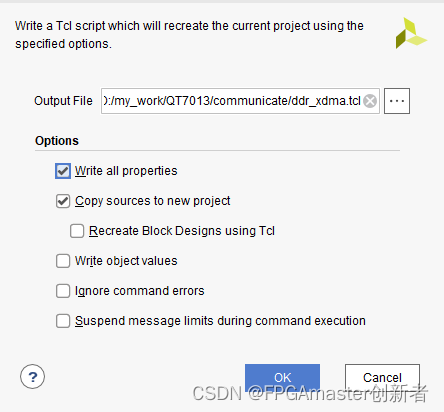

2、生成TCL脚本x

点击Vivado菜单File --> Project --> Write Tcl…

勾选这两个

工程又成功压缩了50%,效果非常明显,但是还不够完美:

3、删除无用文件

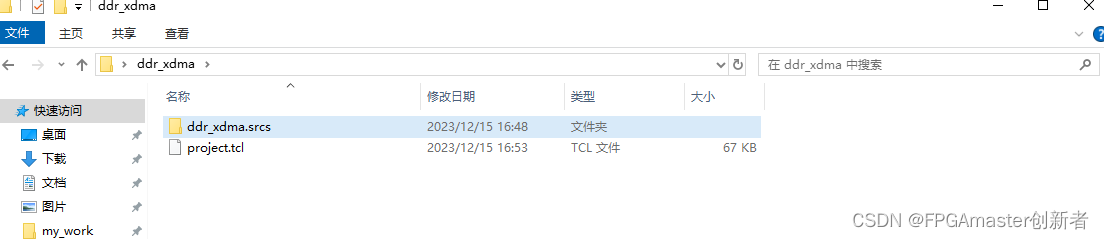

在工程路径下,产生了一个新创建的project.tcl文件,这时只需要保留.srcs文件夹和.tcl文件,其它文件或文件夹可以删除。

工程又成功压缩了95%,效果非常明显,非常完美:

具体压缩大小,要看你的工程代码大小和ip核的调用数量,一般压缩完为超不过20Mb!!

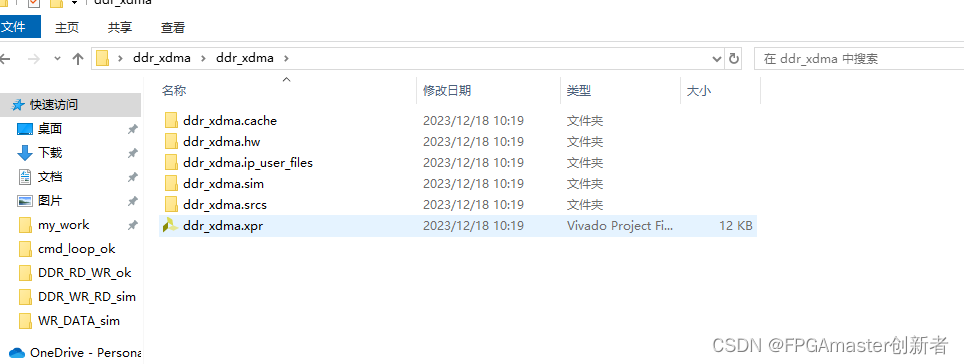

4、最后,来看看基于备份源码,如何还原工程?

在Tcl Console中使用cd命令打开.srcs和.tcl文件的备份路径:

cd C:/Users/a/Desktop/ddr_xdma/ /*路径换成你们自己的工程路径*/然后使用source命令

source project.tcl /*文件名换成自己的*/工程正常恢复:

通过使用Tcl脚本保存Vivado工程,您可以大大节省存储空间,并方便地重新加载和重建工程。这对于版本管理和共享工程也非常有用。

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!

8387

8387

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?